Устройство для контроля многока-нальной вычислительной машины

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскии

Социал истическик

Республик

G 06 F 11/22

Гооударствеииый комитет

СССР (53) УДК 681. .3 (088.8) Опубликовано 15.03.81. Бюллетень № 10

Дата опубликования описания 25.03.81 ио делан изобретений и открытий, (72) Авторы изобретения

Л. Н. Чудный, Б. И. Прокофьев и В..Д. Гапоченко (71) Заявитель

Ъ

l (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ МНОГОКАНАЛЬНОЙ

ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ

Изобретение относится к вычислительной технике, а именно к многоканальным вычислительным цифровым машинам и устройствам для их проверки.

Наиболее близким по технической сущности и достигаемому результату к предлагаемому является устройство для контроля многоканальной вычислительной машины, содержащее блокиратор, выходы которого соединены с управляющими входами ключей блокировки тактовой частоты процессоров, линии связи с вычислительной машиной и блок управления режимом работы процессоров, .включающий ключи, вентиль и формирователь одиночных импульсов (1).

Это устройство позволяет в ручном режиме создавать любые ситуации асинхронных режимов работы вычислительной машины.

Однако при этом контроль состояния процессоров производится оператором с пульта индикапии, что приводит к значительным затратам времени и субъективной оценке результатов контроля.

Цель изобретения — повышение быстродействия контроля в режиме рассинхронизации многоканальной цифровой вычислительной машины.

Поставленная цель достигается тем, что в устройство для контроля многоканальной вычислительной машины, содержащее блокиратор каналов, каждый выход которого соединен с управляющим входом элемента

И блокировки тактовой частоты соответствующего канала; введены счетчик импулБсов, элемент И и синхронизатор, причем тактовый вход устройства соединен с первыми входами элемента И и синхронизатора, выход которого соединен с тактовым входом блокиратора; управляющий вход устрой15 ства соединен со вторым входом элемента

И, выход которого соединен со счетным входом счетчика, установочный и информационный входы устройства соединены соответственно с установочным входом счетчика и информационным входом блокиратора, выход

20 счетчика соединен с управляющим входом синхронизатора.

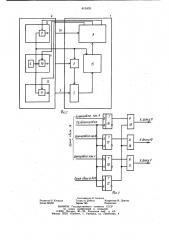

На фиг. 1 изображена структурная схема устройства для проверки многоканаль813435 нои вычислительной машины и часть схемы устройства управления многоканальной вычислительной машины; на фиг. 2 — пример выполнения узла блокировки.

Устройство 1 для контроля многоканальной вычислительной машины содержит счетчик 2, выполняющий роль преобразователя пачки импульсов тактовой частоты во время-импульсный код, установочный вход 3 счетчика 2, соединяющий выход многоканальной вычислительной машины 4, счетный вход счетчика 2 подключен через. элемент И 5 к выходу генератора.б импульсов, тактовой частоты процессора 7 вычислительной машины 4, узел 8 блокировки каналов, каждый выход которого соединен с управляющим входом элементов И 9 — 11 блокировки тактовой частоты процессоров 7, 12 и 13. Управляющий вход 14 узла блокировки соединен с вычислительной машиной 4, синхронизация сигналов блокировки, полученных на выходе счетчика 2 сигналами тактовой частоты генератора 6 происходит с помощью синхронизатора 15. Элемент И 5 соединен с управляющим входом устройства и с выходом тактового генератора 6.

Счетчик 2 программно управляемый, на установочный вход 3 которого от вычислительной машины 4 поступает установка, пропорциональная количеству тактовых импульсов рассинхронизации процессоров. Сигнал переполнения счетчика 2 соединен со входом синхронизатора 15. Узел 8 блокировки (фиг. 2) содержит триггера 16 — 18 блокировки процессоров, элементы И 19 — 21, триггер 22 останова по выходу соединен с управляющим входом элементов И 19 — 21 и определяет момент начала блокировки выбранного программой процессора. Управляющие входы триггеров 16 — 18 и 22 одним из входов «Разблокировка» подключены к управляющему входу 14, а установочный вход триггера 22 соединен с выходом синхронизатора 15 или, если в устройстве не используется синхронизация,.то с выходом счетчика 2.

Устройство для контроля многоканальной вычислительной машины в режиме рассинхронизации предназначено для контроля состояния процессоров в режимах асинхронной работы. Асинхронная работа процессоров не является основным режимом УВМ, но такой режим возможен в случае сбоев в одном из процессоров или в случае подключения, одного из процессоров в отслеживающее звено какого-либо процесса, а остальных процессоров — в жесткую программу управления этим процессом.

Устройство работает следующим образом, В режиме проверки рассинхронизации процессоров с выхода вычислительной машины 4, по программе на вход 3 устройства поступает уставка на вход счетчика 2 пропорциональная количеству тактовых импульсов рассинхронизации процессоров 7, 12 и 13.

Формула изобретения

25 зо

В соответствии с программой проверки сигнала блокировки выбранного процессора 7 (12 и 13) с вычислительной машины 4 по входу 14 поступает команда блокировки каналов А (В, С) (фиг. 1 и 2), которая подготавливает блокиратор 8 к работе, т. е. устанавливает триггер,16 (17 и 18) в состояние блокировки. В момент времени, определяемый управляющим сигналом, на входе 16 открывается элемент И 5 и на счетный вход счетчика 2 начинает поступать тактовая частота генератора 6. После определенного количества тактовых импульсов, определяемых уставкой, выдается сигнал переполнения, который поступает на триггер 22 узла 8 блокировки. Выход триггера

22 через элемент И 19 (20 и 21) блокирует, выбранный процессор в определенном такте работы, управляя работой соответствующих элементов И 9 (10 и 11). После останова выбранного процессора остальные процессоры продолжают работать в основном режиме. Момент съема блокировки происходит также программно по входу 14 командой «Разблокировка». Сигнал «Разблокировка» поступает на К входы триггеров 16—

18 и 22 и через элементы И 19 — 21 снимается блокировка заблокированного процессора. Использование изобретения позволяет автоматизировать процесс проверки вычислительной машины в режиме рассинхронизации процессоров за счет исключения ручных проверок и существенно увеличить тем самым быстродействие контроля, обеспечить его объективность и надежность.

Устройство для контроля многоканальной вычислительной машины, содержащее узел блокировки каналов, каждый выход которого соединен с управляющим входом элемента И блокировки тактовой частоты соответствующего канала, отличающееся тем, что, с целью повышения быстродействия контроля в устройство введены счетчик импульсов, элемент И н синхронизатор, причем тактовый вход устройства соединен с первыми входами элемента И и синхронизатора, выход которого соединен с тактовым входом узла, блокировки, управляющий вход устройства соединен со вторым входом элемента И, выход которого соединен со счетным входом счетчика, установочный и информационные входы устройства соединены соответственно с установочным входом счетчика и информационным входом узла блокировки, выход счетчика соединен с управляющим входом синхронизатора.

Источники информации, принятые во внимание при экспертизе

1. Устройство для проверки многоканальной ЦВМ ЗСТ1М вЂ” IK ХА2.702.141. ТУ (прототип).

813435

Редактор И. Касарда

Заказ 346/62

Составитель И. Сигалов

Техред А. фойкас Корректор М. Демчнк

Тираж 745 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, )К вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4