Устройство для контроля логическихсхем

Иллюстрации

Показать всеРеферат

Союз Советскнх

Соцналнстнчесннх

Республнк

ОЛ ИСААКИЕ

ИЗОьРЕТЕЙИЯ нщ 813436 т, б=-.". .г ° . 1 г, I

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6!) Дополнительное к авт. свид-ву ¹ 595735 (22) Заявлено 28.06.78 (21) 2635228/18-24 (51) M. Кл,а

G 06 F 11/26 с присоединением заявки №вЂ” (23) Приоритет—

Государственный комитет

Опубликовано 15.03.81. Бюллетень №10

Дата опубликования описания 25.03.8! (53) УДК 681.325 (088.8) по делам изобретеиий и откпытий

Ю. С. Манукян, Г. И. Филатов, С. В. Селезнев и Ю. А

I (72) А вторы изобретения

„ 1

Тбилисский филиал Всесоюзного научно-исследо ат метрологии им. Д. И. Менде лее (7!) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ СХЕМ

Изобретение относится к средствам для испытания цифровых устройств и обнаружении ошибок в их работе на основе тестирования.

По основному авт. св. № 595735 известно устройство для контроля логических схем, содержащее схемы сравнения, регистры задания, коммутаторы-формирователи, компараторы, блоки индикации и управления. и блок эталонов. Работа устройства основана на анализе откликов контролируемой схемы на контрольные тесты, содержащие ин- tO формацию об уровнях сигналов на входах и выходах испытуемой схемы (1).

Недостатком этого устройства является невысокая достоверность контроля.

11ель изобретения — повышение достоверности информации.

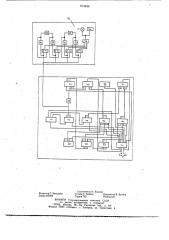

Для достижения поставленной цели в устройство для контроля логических схем введены переключатель и узел контроля регистров, при этом узел контроля регистров содержит элементы И вЂ” НЕ, ключи. индика- 2о тор, элемент ИЛИ и формирователь сигнала, нрн этом каждый разряд задающего регистра подклочен к первому входу соответствуюгцего элемента И вЂ” НЕ и через соответствующий ключ первой группы со вторым входом элемента И вЂ” НЕ, выходы ключей первой группы попарно объединены и через соответствующий ключ второй группы выходы элементов И вЂ” НЕ подключены к соответствующим входам элемента ИЛИ, выход которого соединен с индикатором и формирователем сигнала, выход которого подключен ко входу переключателя, выход которого соединен с соответствующими входами регистров. . На чертеже изображена принципиальная схема предлагаемого устройства.

Устройство содержит задающий регистр

1, элементы И вЂ” HE 2 — 5, элемент ИЛИ 6, индикатор 7, формирователь 8 сигнала, ключи 9 — 14, приемник 15 информации, переключатель 16.

Выход первого разряда задающего регистра 1 соединен со входом элемента И вЂ” — НЕ 2. Выход второго разряда соединен со входом элемента И вЂ” HE 3 и далее выход каждого последующего разряда регистра 1 соединен со входом соответствующего элемента И вЂ” НЕ 4 и 5. На чертеже показано. только четыре разряда регистра 1. Выходы всех схем антисовпадений соединены со вхо3 813436

50 дами элемента ИЛИ 6, выход которого соединен с индикатором 7 и с формирователем

8 сигнала. Вход каждого элемента И вЂ” HE

2 — 5, соединенный с выводом разряда регистра 1, соединен соответственно через один из кл1очсй 9 — 12 со вторым входом этого

we элемента И вЂ” HE. т. е. вход схемы 2 через ключ 9 соединен со вторым входом этой же схемы 2, вход схемы 3 соединен через ключ 10 со вторым входом 3 и т. д.

Аналогично соединены входы всех последующих элементов И вЂ” НЕ. Кроме того, выиоды ключей 9 — О и 1! — 12 попарно соединены межлу сооой посредством ключей 3 и 14. Выводы разрядов регистра 1 соединены с приемником 15 информации.

Работа предлагаемого устройства про- 15 исходит в два этапа при замкнутых ключах

13 и 14.

На первом этапе замыкаются ключи, связанные, например с нечетными разрядами регистра (на чертеже ключи 9 и 11).

Размыкатели !О и !2, связанные с четными разрядами регистра 1, остаются разомкнутыми. Во все разрялы регистра записывается одинаковый сигнал. При этом сигнал с нечетных разрядов регистра I поступает на соединенные с ним схемы 2 и 4 антисов- 25 падений и чсрез замкнутые ключи 9 и 11 на вторые входы этих схем. Поэтому на выходах схем 2 и 4 действует сигнал «0».

Одновременно через замкнутые ключи, 13 и 14 сигнал с нечетных разрядов поступает на вторые входы схем 3 и 5 антисовпадений, 30 на первые входы которых действует сигнал с четных разрядов регистра 1. Если сигналы, записанные в четных разрядах, совпадают с сигналами, записанными в соседних с ними нечетных разрядах, то на выходе элеметов И вЂ” НЕ 3 и 5 будет действовать сигнал «О», При несовпадении этих сигналов на их выходе появится сигнал «I», который через элемент ИЛИ 6 включит индикатор 7 и через формирователь 8 сигнала остановит устройство для контроля логичес- 40 ких схем., При замкнутых ключах 9 и 11 в регистр

1 записывается последовательно сигнал «О»

«1» и «О». После этого начинается второй этап раооты устройства, при котором ключи 10 и 12 замыкаются, а ключи 9 и 11

45 размыкаются, Работа устройства на этом этапе аналогична описанной выше. При этом сигнал, записанный во втором и четвертом разрядах регистра 1, действует соответственно на оба входа схем 3 и 5 антисовпадений, вследствие чего на их выходах действует сигнал «О». Сигнал с вывода второго разряда через замкнутые ключи !О и

13 поступает на вход элементов И вЂ” HE 2, где сравнивается с еигналом, записанным в первом разряде регистра 1. Сигнал с вывода третьего разряда регистра через замкнутые ключи 11 и 14 поступает на вход схемы 5,где сравнивается с сигналом, записанным в четвертом разряде регистра i. Ha этом этапе так же в регистр 1 последовательно записываются сигналы «0», »1» и «О», В случае появления сигнала несовпадения указанным способом через элемент ИЛИ 6 происходит включение индикатора 7 и через схему формирователя 8 сигналов устройства.

После окончания описанных выше процессов самоконтроля ключи !3 и 14 замыкаются, а клю ги 9 — !2 размыкаются, благодаря чему разряды задающего регистра оказываются соединенными с приемником 15 информации. В качестве приемника 15 информации в зависимости от функции, «ыполняемой задающим регистром в устройстве, могут, быть соответствующие схемы сравнения или схема сравнения и коммутатор-формирователь. Затем начинается контроль испытуемой схемы, осуществляемый в соответствии с программой ее испытания. Управление ключами 9 — 14 осуществляется программным путем через блок управления известного устройства.

Таким образом, предлагаемое устройство позволяет периодически произвести контроль исправности задающих регистров. Кроме того, проверке на рабочих режимах подвер.тся и устройство самоконтроля, так как ,учае возникновения в нем неисправнона этих режимах произойлет включение индикатора 7 и остановка устройства.

Формула изобретения

Устройство для контроля логических схем по авт. св. ¹ 595735, отличающееся тем, что, с целью повышения достоверности информации, в устройство введены переключатель и узел контроля регистров, при этом узел контроля регистров содержит элементы И вЂ” HE. ключи, индикатор, элемент

ИЛИ и формирователь сигнала, при этом каждый разряд задающего регистра подключен к первому входу соответствующего элемента И вЂ” HE и через соответствующий ключ первой группы со вторым входом элемента И вЂ” HE, выходы ключей первой группы попарно объединены и через соответствующий ключ-второй группы выходы элементов И вЂ” НЕ подключены к соответствующим входам элемента ИЛИ, выход которого соединен с индикатором и формирователем сигнала, выход которого подключен ко входу переключателя, выход которого соединен с соответствующими входами -регистров.

Источники информации, принятые во внимание при экспертизе

l. Авторское свидетельство СССР

No 595735, кл. G 06 F 11 00, 1977 (прототип), 813436

Составитель Н. Быкова

Редактор Т. Веселова Техред А. Бойкас Корректор В. Бутяга

Заказ 346/62 Тираж Т45 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, )К вЂ” 35, Раушская наб., д. 4/5

Филиал ППП Патент>, г. Ужгород, ул. Проектная, 4