Интегрирующее устройство

Иллюстрации

Показать всеРеферат

Ой И (: НИЕ

ИЗОБРЕТЕНИЯ

Союз Советскнк

Соцналнстнчесння

Республнк.Ф

К АВТОИ:КОА4У СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22}Заявлено 150179 (21) 2714580/18-24 (51)М. Кл. с присоединением заявки ¹â€” (23) Приоритет

G 06 G 7/18

Государственный комитет

СССР но делам изобретений и открытий

Опубликовано 150381, Бюллетень ИЯ 10 (53) УДК 681. ЗЗ5 (088. 8) Дата опубликования описания 150381 (72) Авторы изобретения

Н.Е.Болгов и С.Д.Лутов

"«) " с

Ц,,,. л

4, с

Ордена Ленина институт кибернетики AH Украййской ССР(71) Заявитель (54) ИНТЕГРИРУЮЩЕЕ УСТРОЙСТВО

Изобретение относится к автоматике и .может быть .использовано .в ре-. гулирующих и самонастраивающихся устройствах, например, для управления технологическими процессами.

Известны интегрирующие устройства, выполненные на основе одного или двух аналоговых запоминающих устройств (lj.

Недостатком последнего устройства являются ограниченные функциональные возможности (устройство осуществляет только интегрирование) и большая сложность (каждое АЗУ представляет собой усилитель с резисторами и ключом, выпрямителем и запоминающим элементом на магнитном сердечнике).

Наиболее близким к предлагаемому по техническому решению является интегрирующее устройство, содержащее запоминающие блоки, переменный входной резистор, входной переключатель, переменный выходной резистор и выходной переключатель . Запоминающий блок состоит из усилителя. с резистором в цепи обратной связи, запоминающего элемента и переклю" чателя. Все ключи управляются от датчика временных интервалов.

Устройство реализует алгоритм Y =К Х Х», K=c on st, т.е. осуществляет дискретное интегрирование (2).

Недостатком данного устройства являются ограниченные функциональные воэможности,так как оно выполняет только дискретное интегрирование.

Цель изобретения - расширение класса решаемых задач за счет формирования пропорциональной составляющей.

Указанная цель достигается тем, 15 что в интегрирующее устройство, содержащее два операционных усилителя, инвертирующий вход первого из которых:соединен с замыкающим контактом первого переключателя, через

2О первый масштабный резистор — с размыкающим контактом второго переключателя и через первый запоминающий элемент — с замыкающим контактом второго переключателя, переключающий контакт которого подключен к выходу первого операционного усилителя, размыкающийй контакт первого переключателя соединен с инвертиру ющим входом второго операционного

30 усилителя, подключенного через вто813454

25

55

65 рой масштабный резистор к замыкающему контакту третьего переключателя, размыкающий контакт которого подключен через второй запоминающий элемент к инвертирующему входу второго операционного усилителя, выход которого соединен с переключающим контактом третьего переключателя, а переключающий контакт первого переключателя через первый переменный масштабнЫй резистор подключен ко входу устройства, и датчик временных интервалов, подключенный к управляющим входам переключателей, дополнительно введены два переменных масштабных резистора, операционные усилители выполнены диффе- 15 ренциальными, причем их неинвертнрующие входы через соответственно второй и третий переменные масштабные резисторы соединены со входом устройства, а разьыкающий контакт второго переключателя и замыкающий контакт третьего переключателя подключены к выходу устройства.

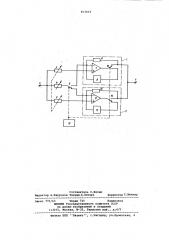

На чертеже представлена схема предлагаемого интегрирующего устройства.

Устройство содержит запоминающие блоки 1 и 2, переменные масштабные резисторы 3,4 и 5 и переключатель б.

Запоминающий блок 1 состоит иэ дифференциального операционного усилителя 7 с масштабным резистором 8 в цепи обратной связи, запоминающего элемента 9 и переключателя 10.Запоминающий блок 2 состоит иэ дифференциального операционного усилителя 35

11 с масштабным резистором 12 в цепи обратной связи, запоминающего элемента 13 и переключателя 14. Все переключатели управляются от датчика

15 временных интервалов.

Входом устройства является точка соединения всех переменных резисторов, а выходом — точка соединения выходов запоминающих блоков 1 и 2.

Интегрирующее устройство работает следующим образом.

Переключающий контакт переключателя 10 находится в верхнем положении, а переключателей б и 14 — в нижнем. При этом запоминающий блок

1 находится в режиме считывания вы" ходного сигнала, а запоминающий блок

2 - в режиме записи поступающих сигналов. Выходной сигнал Y{t) на выходе усилителя 7 представляет собой алгубраическую.сумму текущего входного сигнала x{t), подаваемого через переменный резистор 3, и сигнала, записанного в запоминающий элемейт

9 на предыдущем такте, В это же время на инвертирующий вход усилителя 11 подается входной сигнал x(t), поступающий через переменный резистор 4 и переключатель б, и выходной сигнал Y(t) - через . резистор 12. На неинвертирующий вход этого же усилителя подается через переменный резистор 5 входной сигнал х(t).

Предположим, в исходном состоянии в оба элемента памяти 9 и 13 записаны нули (Ye=0) . На первом шаге с появлением входного сигнала ,Х (1) получим на выходе запоминающего блока 1

Y (1 ) =К„Х1(t), где К, = - = -1 —.

1 R3 R5

В запоминающий блок 2 в это время записывается токовый сигнал

i Ä =X Ä (t), — — X Ä (t) — — Х.(() - i

1 R

Ню ч ВФ 4 ВЗ к

Rq

По команде датчика 15 временных интервалов в режим записи. пе реводится блок 1, а считывания— блок 2. Тогда на втором шаге на выходе запоминающего блока 2 получим .

YL (t) = Xe (t) -R» (—

Н» 1 1 R

Rq R5 R4 ВЪ

1 RR к ) Хч= КчХ г() +КгХ1 где К =

Ra R4

Ва

R4

Хч — значение входного сигнала в конце первого шага. Знак минус перед.вторым слагаемым взят ввиду того, что записанный в запоминающий элемент сигнал в режиме считывания инвертируется.

В это же время идет запись сигналов в запоминающий блок 1

13г =X%(t) — хг (t) ° -- — Х (t) х

4 1 R»

)гз 84 г Rg

l — — х к а Яв

После команды датчика 15 снова запоминающий блок 2 переводится в режим записи, а запоминающий блок

1 — в режим считывания.

Выходной сигнал на третьем шаге (t) = К Х (t)-В { — — — -К вЂ” )Х+

1 1 1

3 Rp R4 вайа

+ Кг КЧ=.КЧХЗ (х)+Кг (ХЧ+Хг)

Ву ка и т.д.

Предлагаемое устройство реализует алгоритм

Ф%-ч

Y (t) =К Х ч(1) +Кг f, Хч при 2 )=О, Как видно из формулы, первое слагаемое представляет собой пропорциональную составляющую текущего значения входного сигнала, Второе слагаемое есть сумма значений входных сигналов на предыдущих и-1 шагах, т.е. дискретный интеграл от входйого сигнала на этих шагах, Следовательно, устройство формирует сигнал но пропорционально-интегральному эакон9.

Настройка коэффициентов Кч осуществляется резисторами 3 и 5, Ка резистором 4. При К -ч 0 (сопротивле813454 ние резисторов 3 н 5 ) устройство работает в режиме дискретного интегратора. При К 0 (сопротивление

4- ) устройство вырождается в линейное звено, Постоянная времени интегрирования определяется величиной коэффициента К1 и длительностью интервала квантования. Она равна Гд Т/К .

Таким образом, наличие дополнительных переменных резисторов, вы- полнение операционных усилителей 10 дифференциальными и связь их неинвертирующих входов через переменные резисторы со входом устройства, а также соединение выходов запоминающих блоков с выходом устройства расширило его функциональные воэможности. Данное интегрирующее устройство формирует выходной сигнал по ПИ-закону, причем. настройка коэффициентов К„ и Кд независима. 29

B качестве запоминающих элементов в устройстве испольэовался электромагнитный модулятор света с фотоэлектрическим считыванием. Функции элемента памяти может выполнять лю- 2 бой активный запоминающий элемент с непрерывным токовым выходом.

Использование данного устройства для управления технологическими процессами улучшает качество регулирования, так как наличие пропорциональной составляющей является эффективным способом управления.

Формула изобретения

Источники информации, принятые во внимание при экспертизе

1. Розенблат М.А. Магнитные элементы автоматики и вычислительной

4О техники. М., Наука °, 1974, с.607609

2. Авторское свидетельство СССР по заявке В 2124758,кл.G 06 G 7/18, 1975 (прототип} .

Интегрирующее устройство, содержащее два операционных усилителя, инвертирующий вход первого из которых соединен с замыкающим контактом первого переключателя, через первый масштабный резистор — с размыкающим контактом второго переключателя и через первый запоминающий элемент— с замыкающим контактом второго переключателя, переключающий контакт которого подключен к выходу первого операционного усилителя, размыкающий контакт первого переключателя соединен с инвертирующим входом второго операционного усилителя, подключенного через второй масштабный резистор к эаьыкающему контакту третьего переключателя, размыкающий контакт которого подключен через второй запоминающий элемент к инвертирующему входу второго операционного усилителя, выход, которого соединен с переключающим контактом третьего переключателя, а переключающий контакт первого переключателя через первый переменный масштабный резистор подключен ко входу устройства, и датчик временных интервалов, подключенный к управляющим входам переключателей, о т л и ч а ю щ е е с я тем, что, с целью расширения класса решаеэых задач за счет формирования пропорциональной составляющей, в него дополнительно введены два переменных масштабных резистора, операционные усилители выполнены дифференциальными, причем их неинвертнрующие входы через соответственно второй и третий переменные масштабные резисторы соединены со входом устройства, а размыкающий контакт второго переключателя и заьнкающий контакт. третьего переключателя подключены к выходу устройства.

813454

Составитель С. Белан

Редактор A.Hàóðñêîâ Техред Л. Пекарь Корректор С Шекмар заказ,775/63 Тираж 745 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и откритий

113035, Москва, Ж-35, РаушскаЯ наб,, д.4/5 филиал ППП Патент, г.ужгорОд, ул.Проектная, 4