Устройство для выборки адресовиз блоков памяти

Иллюстрации

Показать всеРеферат

Союз Советсник

Соцналистннесннк

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ о)813504 (61) Дополнительное к авт. сеид-ву (22) Заявлено 271274 (2т) 2088102/18-24 с присоединением заявки ¹ (23) Приоритет

Опубликовано 150 3.81. Бюллетень №10

Дата опубликования описания 15,03,81 (51)М. Кл.з

6 11 С 8/00

Государственный комитет

СССР но делам изобретений и открытий (53) УДК 681. 327. .66(088.8) (72) Автор изобретения

Л. М. Шашук (71) Заявитель (54 ) УСТРОЙСТВО ДЛЯ ВЫБОРКИ АДРЕСОВ ИЗ БЛОКОВ

ПАМЯТИ

Изобретение относится к вычислительной технике и предназначено для организации последовательной адресации ячеек памяти при случайным образом перемещающихся заявках на запись и на чтение, в частности может быть использовано в буферных запоминающих устройствах.

Известны устройства:для выборки адресов из блоков памяти, содержащие адресные счетчики записи и считывания, реверсивный счетчик для определения разности кодов адресов записи и считывания и элементы И (1) и (2) . 15

Недостатком этих устройств является то, что при случайном сбое реверсивного счетчика происходит запоминание ложной информации, приводящее к неправильной работе всего 20 устройства, так как оно не обладает способностью самовосстановления правильного функционирования.

Наиболее близким к предлагаемому является устройство, содержащее адрес-25 ные счетчики записи и чтения и элемент сравнения, входы которого соединены с соответствующими выходными шинами адресных счетчиков, счетные входы которых соединены с управляю- 30 щими шинами, а входы сброса их — с шиной сброса (3) .

Однако в таком устройстве при каждой смене адреса записи или адреса чтения необходимо сравнение их на

"больше", "меньше" и "равно". Время выполнения операции "больше" или

"меньше" пропорционально количеству разрядов и сравниваемых кодов и равно п ° Т., где С вЂ” длительность переходного процесса в одном разряде элемента сравнения. Кроме того, трехоперационный элемент сравнения достаточно сложен.

Цель изобретения — повышение быстродействия и упрощение устройства.

Поставленная цель достигается тем, что устройство. содержит два элемента И, два дифференцирующих элемента и триггер, вход установки которого через первый дифференцирующий элемент соединен с выходной шиной старшего разряда адресного счетчика записи, первый вход сброса триггера через второй дифференцирующий элемент соединен с выходной шиной старшего разряда адресного счетчика чтения, второй вход сброса триггера соединен с шиной сброса, прямой выход триггера соединен с первым входом первого

813504 элемента И, выход которого соединен с шиной. запрета записи, инверсный б выход триггера соединен с первым входом второго элемента И, выход которого соединен с шиной запрета чтения, а вторые входы элементов И соединены с выходом элемента сравнения.

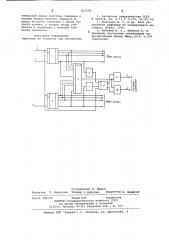

На чертеже представлена блок-схема предложенного устройства.

Устройство содержит адресный счетчик 1 записи, управляющую шину 2 подачи импульсов смены адреса записи, адресный счетчик 3 чтения, управляющую шину 4 подачи импульсов смены адреса чтения, элемент 5 сравнения, дифференцирующие элементы 6 и 7, триггер 8, элементы И 9 и 10, шину

11 запрета записи, шину 12 запрета чтения и шину 13 сброса.

Устройство работает следующим образом.

После включения питания Оба ад- 20 ресных счетчика и триггер по шине сброса сбрасываются в нулевое состояние. При этом элемент сравнения индицирует равенство кодов счетчиков, и на его выходе появляется сиг- 25 нал, соответствующий логической единице. Такой же сигнал присутствует и на инверсном выходе триггера. В результате совпадения сигналов логических единиц на входах элемента

И 10 на его выходе формируется сигнал запрета чтения, свидетельствующий о том, что информация в памяти не содержится. После того, как в память по нулевому адресу будет записана информация, на счетный вход адресного счетчика записи поступает импульс смены адреса записи и счетчик формирует следующий, отличающийся на единицу, адрес записи. Неравенство адресных кодов индицируется элемен.40 том сравнения и на его выходе появляется сигнал, соответствующий логическому нулю и снимается сигнал запрета чтения. Если теперь произойдет чтение, то изменится на единицу код ад- 45 реса чтения. Коды адреса записи и адреса чтения опять станут равными, что повлечет повторное формирование сигнала запрета чтения. При последующих записях и чтениях коды адресов будут возрастать, однако, код адреса чтения не сможет привысить кода адреса записи, что позволяет избежать чтения по адресам ячеек памяти, не содержащих информацию.

Каждый из адресных счетчиков представляет собой суммирующий счетчик с коэффициентом пересчета 2 . Поступлеtl ние 2"-ного импульса смены адреса за писи приводит счетчик адреса записи в нулевое состояние, и код адреса за- ф) писи станет меньше кода адреса чтения. При переходе адресного счетчика записи в нулевое состояние на выходной шине старшего разряда счетчика формируется сигнал переноса, и импульс, возникающий при этом на выходе дифференцирующего элемента 6, устанавливает триггер в единично состояние. Если код адреса записи продолжает увеличиваться, то в момент его равенства коду чтения на входах элемента И 9 произойдет совпадение сигналов логических единиц с выхода элемента сравнения и прямого выхода триггера, что приведет к формированию сигнала запрета записи. Если затем произойдет чтение, то элемент сравнения, определив наступившее неравенство адресных кодов, сформирует на своем выходе сигнал, соответствующий нулю, что приведет к снятию сигнала запрета записи. Таки, образом, теперь адрес записи не сможет стать больше адреса чтения, что предотвращает запись информации по адресам ячеек памяти, из которых информация еще не считана.

При поступл- 2 -ного импульса п смены адреса чтения адресный счетчик чтения придет в нулевое состояние и с этого момента адресный код чтения должен оставаться меньше адресного кода записи для чего импульс, сформированный из сигнала переноса адресного счетчика чтения дифференцирующим элементом 7, приводит триггер в состояние, при котором на его инверсном выходе появится сигнал, соответствующий логической единице, и в случае равенства адресных кодов на выходе элемента И 10 появится си.нал запрета чтения.

Экономический эффект устройства обуславливается его простотой и быстродействием.

Формула изобретения

Устройство для выборки адресов из блоков памяти, содержащее адресные счетчики записи и чтения и элемент сравнения, входы которого соединены с соответствующими выходными шинами адресных счетчиков, счетные входы которых соединены с управляющими шинами, а входы сброса их — с шиной сброса, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия и упрощения устройства, оно содержит два элемента И, два дифференцирующих элемента и триггер, вход установки которого через первый дифференцирующий элемент соединен с выходной шиной старшего разряда адресного счетчика записи, первый вход сброса триггера через второй дифференцирующий элемент соединен с выходной шиной старшего разряда адресного счетчика чтения, второй вход сброса триггера соединен с шиной сброса, прямой выход триггера соединен с первым вхо- дом первого элемента И, выход которого соединен с шиной запрета записи, 813504

Составитель Л. Шашук

Редактор Т. Веселова Техред H.Бабурка Корректор Н. Швыдкая

Заказ 782/66 Тираж 645 Подписное

ВНИИПИ Государственного-комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 инверсный выход триггера соединен с первым входом второго элемента И, выход которого соединен с шиной запрета чтения, а вторые входы элементов И соединены с выходом элемента сравнения.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 427379, кл. G 11 С 11/00, 05.05.74.

2. Войтенко Ю. Г. и др. Блок управления буферным ЗУ сканирующего ав-. томата. Дубна, 1970.

3. Бузунов Ю. A., Вавилов Е. Н.

Принципы построения управляющих вычислительных машин. Киев,1972, с.218 (прототип).