Многоканальный полосовой цифровойфильтр

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ фк+ Q

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 280378 (21) 2597744/18-09 с присоединением заявки ¹ (23) Приоритет

Ойубликовано 15.0381. бюллетень К9 10

Дата опубликования описания 25. 03. 81 (511м 3

Н 03 Н 7/12

Государственный комитет

СССР по делам изобретений и открытий (53) УДК 621 ° 372. . 57!088. 8) В.П.Сырский)и (72) Авторы изобретения

Ф.В.Халитов, С.T.Oðåíäàðåíêî

О.Л.СвинтицКий (71) Заявитель (54) МНОГОКАНАЛЬНЫЙ ПОЛОСОВОЙ

ЦИФРОВОЙ ФИЛЬТР

Изобретение относится к частотноселективным устройствам, а именно к многоканальным цифровым фильтрам, и может быть использовано в системах обработки информации частотных датчиков с целью разделения по каналам последовательностей полос частот следования импульсов для .зыдачи соответствующих исполнительных команд.

Известны цифровые фильтры для .выделения полос частот с заданными средними частотами и границами полос пропускания.

Известно устройство, представляющее собой систему цифровых Фильтров, 15 каждый из которых настроен на задан-, ную область частот и имеет общий кварцевый генератор импульсов эталонной частоты (1).

Однако данное устройство достаточ- 20 но сложно и требует тщательной настройки, Наиболее близким к предлагаемому по технической сущности является устройство, содержащее счетчик, счетный 25 вход которого соединен с выходом генератора эталонной частоты, и и параллельно включенных каналов фильтрации, каждый из которых состоит .из дешифратора, элемента памяти и эле- 3О мента совпадения, выход которого соединен с первым входом накопителя f2).

Недостаток устройства заключается в том, что возникающий случайно на выходе устройства ложный сигнал, например, в результает сбоя каких-либо элементов схемы, а также помех по цепи питания или входного сигнала, будет присутствовать в течение всего времени, пока дешифратор несколько раз не примет одно из фиксированных состояний. Кроме того, указанное устройство не позволяет обрабатывать входной сигнал. частота которого изменяется непрерывно.

Цель изобретения — повышение поме хоустойчивости.

Для этого в многоканальный полосовой цифровой фильтр, содержащий счетчик, счетный вход которого соединен с.выходом генератора эталонной частоты, н т параллельно включенных каналов фильтрации, каждый из которых состоит из дешифратора, элемента па мяти и элемента совпадения, выход которого соединен с первым входом накопителя, введены синхронизатор, распределитель частоты, дот1олнительный счетчик и в каждый канал фильтрации — дополнительный дешифратор, до81 3687 полнительный элемент памяти и дополнительный элемент совпадения, при этом в каждом канале фильтрации первый вход элемента совпадения соеди-нен с прямым выходом элемента памя— ти своего канала фильтрации. второй вход — с инверсным выходом элемента памяти последующего канала фильтра ции, третий вход — с прямым выходом дополнительного элемечта памяти своего канала фильтрации, а четвертый вход — с первым выходом синхронизатора, первый вход допол".êòåëüíoãî элемента совпадения подключен к прямому выходу элемента памяти последующего канала фильтрации, второй входК инверсному выходу элемента памяти своего канала фильтрации, третий вход — к инверсному выходу дополни-. тельного элемента своего канала фиЛьтрации, четвертый вход — к перво— му выходу синхрониз" òîðà,,а выход - 20 ко второму нходу накопителя, первый

Вход элемента гамяти соединен с выходом дешифратора, первый вход дополнительного элемента памяти — с выходом дополнительного дешифратора„ входы дешифраторов и первые входы дополнительных дешифраторов объединены и подключены к выходу счетчика, а вторые входы дополнительных дешифраторон — к выходу дополнительного счетчика, причем вь1ход генератора эталонной частоты соединен со счеткым входа;.T дополнительного счетчика к со входом распределителя частоты, выходы которого подключены к тактоным входам синхронизатора, второй

35 выход которого соединен с устансночными входами счетчика, дополнитель— ного счетчика, элементов памяти каждого канала Фильтрации.

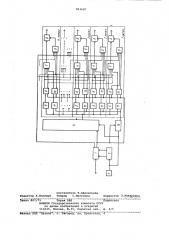

На чертеже представлена структУр- Щ ная электрическая схема многоканального полосового цифрового фильтра.

Истсчник импульсов измеряемой частоты подключен к входу синхронизатора 1, тактовые входы которого подсоединены к выходам распределителя частоты 2, подключенного к генератору эталонной частоты 3. На вход счетчика 4 подаются .импульсы с выхода генератора 3. Выходы счетчика 4 подключены к дешифраторам 5 заданных состояний, выходы которых соединены с входами элементов б памяти, выполненных на триггерах. Прямые выходы элементов б памяти соединены с первыми входами соответствующих элементов совпадения 7, второй вход каждого элемента совпадения 7 соединен с иннерсньж выходом элемента памяти б следующего канала, Выход каждого элемента совпадения 7 под- О ключен к входу соответствующего накопителя 8. Установочный вход каждого накопителя 8 подключен к выходу дополнительного элемента совпадения 9. Первый вход каждого дополнительного элемента овпадения 9 под ключен к прямому выходу элемента б памяти, второй вход — к инверсному выходу соответствующего элемента памяти б. Третьи входы схем дополнительных элементов совпадения 9, объединенные с третьими входами элементов совпадения 7, подсоединень» к выходу "Опрос" синхронизатора 1.

Установочные входы злементон б па.— мяти и счетчика 4 подключены к другому выходу (" Сброс" ) синхронизатора 1. Вход дополнительного счетчика

10 объединен с входом счетчика 4, выход его подключен ко нторьл входам дополнительных дешифраторов 11, каждому из которых соответствует контрольное состояние счетчика 4, близкое к фиксированному, выделяемому соответствующим дешифратором 5, и кратное состоянию дополнительного счетчика 10. Входы дополнительных элементов памяти 12 подключены к выходам дополнительных дешифраторов

11„ а выходы — к четвертью входам зле лентов совпадения 7 и 9.

При необхсдимости получения на выходе какого-либо канала полосы частот с заданной величиной перекры . тия по отношению к соседним каналам, вторые входы элементов совпадения

7 и 9 и-го канала могут быть подключены соответственно к иннерсному и прямому выходам элемента памяти (и + 1() канала„ где К = 2, 3 и т. д., как, например, это показано пунктиром на чертеже для первого и третьего каналов.

Устройство работает следующим образом.

При поступлении на вход устройства последовательности импульсон синхронизатор 1, управляемый сдвинутыми по фазе тактовыми импульсами с выхода распределителя 2, вырабатывает дне последовательности импульсов с периодом входного сигнала, сдвинутые друг относительно друга на период тактовой частоты. При этом импульсы на перном выходе распределителя 2 опережают по времени импульсы на другом его выходе. Импульсы тактовой частоты генератора 3 поступают на счетчик 4. При этом счетчик принима— ет ряд состояний, фиксируемых соотнетствующи."ли дешйфраторами, сначала дополнительным 11, затем основным 5, выходные сигналы которых фиксируются н элементах 12 и б памяти. При этом чем ниже частота поступающих на вход устройства импульсов, тем большее количество элементов 12 и б памяти переключится и выдаст разрешающий уронень сначала на четвертый. а затем и на пергый ьход соответствующих элементов совпадения 7. Однако с приходом с- гналB. "Опрос" на третьи входы -:лс.мсн-.оВ совпадения 7 нь:хо o» . сигнал будет прис.утствонать только

813687 на выходе того элемента совпадения

7, который соответствует последнему из дешифраторов 5, выдавшему с:ríàë на элемент 6 памяти до прихода сигнала "Опрос", поскольку на втором входе этого элемента имеется разрешающий уровень соседнего элемента б памяти, соответствующего очередному дешифратору 5, не получившему сигнал со счетчика 4. Таким образом, на выходе каждого элемента совпадедения 7 будут присутствовать импульсы, совпадающие по времени с импульсами "Опрос", частоты которых лежат в границах, задаваемых соседними дешифраторами.

На выходе накопителей 8 команд- 15 ный сигнал появляется только после уверенного приема соответствующим элементом совпадения 7 заданной полосы частот. (например, в количестве трех импульсов). Сигнал, случайно (» прошедший на выход элемента созпадения 7, в следующем цикле опроса сбрасывается с накопителя 8 с помощью дополнительного элемента совпадения 9. Сигналом "Сброс" с выхода синхронизатора элементы памяти б и

12 и счетчики 4 и 10 устанавливаются в исходное состояние.

Применение в устройстве четкой организации частот "Сброс" и "Опрос" введение дополнительных элеглентов со30 впадения, включение определенным образом йакопителей импульсов и элементов памяти, а также введение дополнительных дешифраторов с контрольными элементами памяти позволяет соr кратить до минимума вероятность появления на выходе ложной информации, что особенйо важно когда выходные сигналы являются командными для приведения в действие исполнительных 40 механизмов .как при обработке информации с заданной стабильностью полос частот, так и с непрерывно меняющейся частотой. Кроме того, включение синхронизатора в цепь.входного сигнала значительно повышает помехоустойчивость фильтра; фильтр не сложен по конструкции. по настройке и может быть реализован на микросхе- мах широкого применения.

Формула изобретения

Многоканальный полосовой цифровой фильтр, содержащий счетчик, c÷eòü é 55 вход которого соединен с выходом генератора эталонной частоты, и параллельно включенных каналов Фильтрации, каждый из которых состоит и дешифратора, элемента памяти и эл»мента совпадения, выход которого соединен с первым входом накопителя, отличающийся тем, что, с целью повышения помехоустойчивости в чего введены синхронизатор, распределитель частоты, дополнительный счетчик и н каждый канал фильтрациидополнительный дешифратор. дополнительный элемент памяти и дополнительный элемент совпадения, при эТом в каждом канале фильтрации первый вход элемента совпадения соединен с прямым выходом элемента памяти своего канала Фильтрации, второй вход — с инверсным выходом элемента памяти последующего канала фильтрации, третий вход — с прямым выходом дополнительного элемента памяти своего канала фильтрации, а четвертый вход — с первым выходом синхронизатора, первый вход дополнительного элемента совпадения подключен к прямому выходу элемента памяти последующего канала фильтрации, второй вход к инверсному выходу элемента памяти своего канала фильтрации, третий вход — к инверсному выходу дополнительного элемента памяти своего канала фильтрации, четвертый вход — к первому выходу синхронизатора, а выход — ко второму входу накопителя, первый вход элемента памяти соединен с выходом дешифратора, первый вход дополнительного элемента памяти с выходом дополнительного дешифратора, входы дешифраторов и первый входь. дополнительных дешифраторов объединены и подключены к выходу счетчика, а вторые входы дополнительных дешифраторов — к выходу дополнительного счетчика, причем выход генератора эталонной частоты соединен со счетньгл входом дополнительного счетчика и со входом распределителя частоты, выходы которого подключены к тактовым входам синхронизатора. второй выход которого соединен с установочными входами счетчика. дополнительного счетчика, элементов памяти и дополнительных элементов памяти каждого канала фильтрации.

Источники информации, принятые во внимание при экспертизе

1. Машбиц Л.N. Синтез систем частотной селекции с помощью числовых схем. "Радиотехника", т. 24, Р 9, 1969, с. 63-70.

2. Авторское свидетельство СССР г- 250235. кл. Н 03 у 17/62, 1968 (прототип).

813687

Составитель Т.АФанасьева

Редактор К.Волощук Техред С.Мигунова Корректор :.О.Макаренко

Эакаэ 807/75 Тираж 988 Подписное

ВНИИПИ Государственного комитета СССР по делам иэобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д. 4/5

Филиал ППП "Патент, г. Ужгород, ул. Проектная,