Многоканальный таймер

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 09.04.79 (21) 2749464/18-21 с присоединением заявки No— (23) Приоритет— (51) М К„з

Н 03 К 5/13

Государственный номитет (53) УДК 621.374..5 (088.8) по делам нзооретений и открытий

Опубликовано 15.03.81. Бюллетень Ме 10

Дата опубликования описания 25.03.81 (72) А вторы изобретения

А. К. Ваганов, В. С. Васильев и В. И. Гордин (71 ) Зая вител ь (54) МНОГОКАНАЛЬНЫИ ТАЛМЕР

Устройство относится к импульсной технике и может быть использовано для формирования временных интервалов в телеметрии, в различных системах таймирования, при исследованиях в области ядерной физики, в измерительной технике, в импульсной радиосвязи, и т. д. В связи с возросшим уровнем автоматизации различных технологических процессов, термоядерных и физических исследований, систем сбора и обработки информации, получаемой при экспериментах, резко увеличился объем электронной аппаратуры, значительная часть которой приходится на дол;о времязадающих устройств — таймеров. При этом большое значение приобретает вопрос уменьшения габаритов и повышения экономичности используемой аппаратуры.

В настоящее время в качестве времязадающих устройств находит широкое применение устройство квантованной задержки.

Известно устройство, содержащее ряд последовательно соединенных делителей (М счетчиков), ряд вентильных схем (N логических элементов И и N логических элементов ИЛИ), переключающее устройство (дешифратор) и выходной вентиль (логический элемент И1 (1).

Недостатками данного устройства являются большое количество используемых элементов, приводящее к увеличению габари5 тов. потребления мощности и стоимости устройства, и зависимость величины задержки каждого последующего канала от величины задержки предыдущего канала.

Цель изобретения — повышение экономичности, упрощение и получение независиt0 мой регулировки величины поканальной задержки.

Для достижения указанной цели в многоканальный таймер, содержащий установочный счетчик (1 + 1) логических элементов И и дешифратор, введены управляющий триггер, оперативное запоминающее устройство с произвольной выборкой и счетчик управления, причем сбросовый вход последнего соединен со сбросовым входом управляющего счетчика, с первым входом входного логического элемента И и с выходом управляющего триггера, вход установки единицы которого является входом старта, выход входного логического элемента И связан со счетным входом уста813737 новочного счетчика, а второй вход его — — co входом тактирук>шей частоты, информационные входы установочного счетчика соединены с выходами оперативного запоминающего устройства с произвольной выборкой,. входы данных КоТоро! связаны с шинами 5 записи, входы адреса — — с выходами c«cT— чика управления и входами дсшифратора, а вход разрешения выборки -- со счетным входом с Iåò÷èêà управления, выходом установочного счетчика и первыми входами х>выходных логических элементов И, вторые входы которых соединены с соответствуюгцими выходами дешифратора, причем второй вход N- выходного логического элемента И Jol>0.>íèòåëü>>o подключен ко Вхо;<у установки нуля управляющего триггера, выходы выходных логических элементов И подключены к выходам таймера.

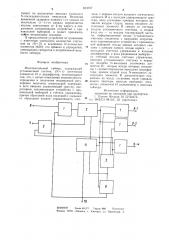

На чертеже представлена структурная схема многоканального таймера.

Устройство состоит из (N+ 1) логических элементов И 1, причем вылход входного логического элемента И связан со счетным входом установочного счетчика 2, а первые входы N-выходных логических элементов И вЂ”вЂ” с выходом установочного счетчика управляюшего триггера 3, выход которого соединен с первым входом входного логического элемента И и со сбросовыми входами установочного счетчика и счетчика управления, оперативного запоминающего устройства 4 с произвольной выборкой, у которого выходы подсоединены ко входам записи установочноп> счетчика, а входы адреса ко входам Дешифратора 5, подключенного к выходам счетчика 6 управления, при этом выходы дешифратора связаны со вторыми входами выходных логических элементов И, а второй вход N его выходного логического элемента И дополнительно соединен со входом установки нуля управляющего триггера, вход установки единицы которого связан со входом старта 7, входа тактовой частоты 8, подключенного ко второму входу входного логического элемента И, выходного устройства 9, которыми являются выходы 1-выходнь.х логических элементов И, шин 10 записей, связанных со входами оперативного запоминак>шего устройства с выборкой, выход установочного счетчика соединен со счетным входом счетчика управления и со входом разрешения выборки Оперативного запоминающего устройства с произвольной выборкой.

Многоканальный таймер работает следующим образом.

В исходном состоянии управляющий триггер 3 находится в нулевом состоянии, блокируя по первому входу входной логический элемент И, счетчики 2 и 6. На вход 8 подается тактирующая частота. В оперативном запоминающем устройстве 4 по шинам

10 записи записано N требуемых задержек (адрес записанных задержек. определяется состоянием счетчика 6) . Выходные логичес20

4 кие элементы И, кроме первого. блокированы по вторым входам уровнями напряжений, снимаемых с выходов дешифратора 5.

На втором входе первого выходного логического элемента И присутствует разрешающий потенциал, соответствующий нулевому состоянию счетчика 6, а на входах записи счетчика 2 присутствуют уровни напряжений, соответствующие устанавливаемой величине первой задержки. На выходах 9 сигналы отсутствуют. При подаче на вход 7 импульса запуска триггер 3 переключается в единичное состояние, деблокируя первый входной логический элемент

И и счетчики 2 и 6. При этом в счетчик 2 из оперативного запоминающего устройства 4 переписывается код, соответствующий величине первой задержки, а на его счетный вход поступает тактирующая частота. Счетчик 2 считает импу1bCI»I, ПОстхпающие на его вхОд.

В момент,, когда счетчик 2 отсчитает записанное количество импульсов и устанавливается в нулевое состояние. на его выходе появляется задержанный во времени относительно стартового сигнала импульс, который поступает на и-;рвые входы выходных логических элементов И, на счетный вход счетчика 6 и на вход разрешения выборки оперативного запоминающего устройства 4. В первом канале 9 — 1 появляется выходной импульс. На выходе счетчика

6 возникает новый код. При этом дешифратор 5 деблокирует второй выходной логический элемент И и блокирует первый выходной логический элемент И, а на выходах оперативного запоминающего устройства 4 появляются уровни напряжения, соответствующие коду устанавливаемой величины второй задержки. В счетчике 2 записывается код, соответствуюший величине второй задержки. Счетчик 2 считает импульсы, поступаюшие на его вход. В момент, когда счетчик 2 отсчитывает записанное количество импульсов и устанавливается в нулевое состояние, на его выходе появляется

3адержанный во времени относительно гыходного сигнала первого канала 9 -1 импульс, который поступает на первые входы выходных логических элементов И, на счетный вход счетчика 6 и на вход разрешения выборки оперативного запоминаюшего устройства 4. Во втором канале 9 — 2 появляется выходной импульс. На выходе счетчика 6 возникает новый код и I. д, В момент, когда в канале 9 — N появляется выходной импульс, на выходе счетчика 6 возникает новый код. На N-ом выходе дешифратора, связанный с Х-ым выходным логическим элементом И, появляется сигнал, который блокирует по второму входу N-ый выходной логический элемент И и перебрасывает триггер 3 в нулевое состояние. Триггер 3 блокирует по первому входу входной логический элемент И и счетчики 2 и 6. Устройство

ыозврашается в исходное состояние. Таким образом, многоканальный таймер выраба813737

Формула изобретения

ВНИИПИ Заказ 42 /77 Тираж 988 Подписное

Филиал ППП кПатент>, г. Ужгород, ул, Проектная, 4 тывает на раздельных выходах (каналах)

N-последовательных импульсов. Величина временной задержки каждого i-го канала относительно (i — 1) -го канала определяется .числом, записанным по i-му адресу в оперативное запоминающее устройство с произвольной выборкой, и может принимать любое независимое значение.

В предлагаемом устройстве по сравнению с известным уменьшено количество счетчиков на (N — 2) и исключено N-логических элементов ИЛИ, что прт вело к упрощению, уменьшению габаритов и потребляемой мощности таймера.

Многоканальный таймер, содержащий установочный счетчик, (N+ 1) логических элементов И и дешифратор, отличающийся тем, что, с целью повышения экономичности, упрощения и получения независимой регулировки величины поканальной задержки, в него введены управляющий триггер, оперативное запоминающее устройство с произвольной выборкой и счетчик управления, причем сбросовый вход последнего соединен со сбросовым входом управляющего счетчика, с первым входом входного логического элемента И и с выходом управляющего триггера, вход установки единицы которого является входом старта, выход входного логического элемента И связан со счетным входом установочного счетчика, а второй вход его — со входом тактирующей частоты, информационные входы установочного счетчика соединены с выходами оперативного запоминающего устройства с произволь- ной выборкой, входы данных которого связаны с шинами записи, входы адреса — с выходами счетчика управления и входами дешифратора, а вход разрешения выборки— со счетным входом счетчика управления, выходом установочного счетчика и первыми входами N-выходных логических эле- . ментов И, вторые входы которых соединены с соответствующиуи выходами дешифратора, причем второй вход N-выходного логического элемента И дополнительно подключен ко входу установки нуля управля20 ющего триггера, выходы выходных логических элементов И подключены к выходам таймера.

Источники информации. принятые во внимание при экспертизе

1. Патент Японии ¹ 52-24375, кл. 98/5 C4 98/5/С 32 (прототип) .