Компаратор

Иллюстрации

Показать всеРеферат

Оп ИСАНИЕ

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик

< 813753

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 04.01.79 (21) 2705100/18-21 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл.

Н 03 К 5/22//

G 05 В 1/01

Гооударстееииый комитет

СССР по делам изобретений и открытий

Опубликовано 15.03.81. Бюллетень № 10

Дата опубликования описания 25.03.81 (53) УДК 621.374..34 (088.8) ) к*ь

Е. А. Коломбет, Ю. В. Осокин. В. P. Вартина Е., .Ю. оокосрйбт;.В. Ф. Цеплис и Л. A. Михеев, - :. & "., ф" р

1 (72) Авторы изобретения и к (7I} Заявитель (54} КОМПАРАТОР

Изобретение относится к вычислительной технике и может быть использовано при проектировании быстродействующих аналоговых интегральных схем.

Известен комиаратор, содержантий дифференциальный каскад (ДК) на транзисторах, эмиттеры которых заземлены через стабилитрон, а базы подключены к источникам входного тока на основе входного

ДК (1).

Однако этот компаратор имеет сравнительно низкое быстродействие, так как насьицается один из транзисторов ДК.

Наиболее близким по технической сущности к предлагаемому изобретению является ком паратор, содержащий дифференциальный каскад на транзисторах, эмиттеры которых через стабилитрон соединены с общей шиной, базы подключены к входным клеммам, а коллекторы через первый и второй нагрузочные резисторы соединены перекрестно с базами транзисторов дифференциального каскада и подключены к эмиттерам каскадных транзисторов, базы которых объединены, а коллекторы подключены к шине питания через третий и четвертый нагрузочные резисторы, коллектор первого каскадного транзисторы и катод диода объединены и соединены с выходной клеммой, а к коллектору второго подключен анод диода (2).

Однако данный компаратор обеспечивает недостаточно быстрое переключение выходного напряжения, длительность которого определяется скоростью заряда (1/С) паразитных конденсаторов (С), подключенных к коллекторам каскадных транзисторов конечным током 1 ДК. Величина паразитных конденсаторов однозначно определена в рамках одной технологии изготовления ИС, а простое увеличение тока 1 приводит к увеличению потребляемой мощности и часто недопустимо.

Цель изобретения — повышение быстродействия компаратора без существенного увеличения потребляемой мощности.

Цель достигается тем, что в компаратор, содержаший дифференциальный каскад на транзисторах, эмиттеры которых заземлены через стабилитрон, базы подключены к пер20 вой и второй входным клеммам, а коллекторы через первый и второй нагрузочные резисторы перекрестно соединены с базами транзисторов и подключены к эмиттерам каскадных транзисторов, базы которых объеди813753 нены, а коллекторы подключены к шине питания через третий и четвертый нагрузочные резисторы, коллектор первого каскадного транзистора и катод диода объединены и соединены с выходной клеммой, а анод диода подключен к коллектору ьторого каскадного транзистора, дополнительно введены транзистор и резистор, причем эмиттеры транзисторов дифференциального каскада соединены через введенный резистор с базами каскадных транзисторов и эмиттером введенного транзистора, база которого сое10 динена с коллектором второго каскадного транзистора, а коллектор — с шиной питания.

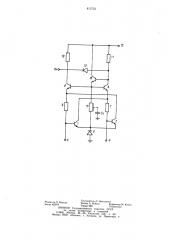

На чертеже приведена принципиальная электрическая схема компаратора. 15

Схема компыратора содержит дифференциальный каскад на транзисторах 1 и 2, базы которых соединены с входными клеммами 3 и 4, эмиттсры через стыбилитрон 5 заземлены, а коллекторы через нагрузочные резисторы 6 и 7 перекрестно соединены с ба-2О зыми транзисторов и 2 и подключены к эмиттерам каскадных транзисторов 8 и 9, базы которых об ьединены, а коллекторы подключены через нагрузоч Iblp резисторы 10 и 11 к шине 12 питания, коллектор каскадного транзистора 8 и катод диоды 13 объсдинены и соединены с выходной клеммой 14, àíî:I, Iиоды l2 подк. ючсп к коллек.ору каскадного транзисторы 9, дополнительно введенный резистор 15 соединен с эмиттерами

30 транзисторов 1 и 2 и базами каскадных гранзнсторов 8 и 9, которые соединены с эмиттером введенного транзистора 16, базы которого соединены с коллектором транзнсторы 9, ы коллектор — — с шиной 12 питания.

Устройство работает следующим образом.

Если в начальный момент протекает ток с входной клеммы 3, а с входной клеммы 4 ток равен нулю, то ток, протекающий через резисторы 10 и 11 и диод 13, втекает в трап-4О зистор 8, а затем в транзистор 2 и резистор 6. В резисторе 7 и транзисторах 1 и 9 ока нет. На выходе диодом 13 устанавливается уровень логического нуля, равный напряжению базы транз 1стора 8, т. е. ни один из транзисторов не насыщен. Благодаря включению транзистора 12 и высокоочного резисторы, имеющего небольшую, но конечной величины (единицы пФ) емкость

С„относительно средней точки (в случае ийтегрыльного исполнения схемы такую роль будет играть диффузионный резистор), в момент перек„11o eHHH TG co входа 3 на вход 4 изменение потенциала на базах

8 и 9 несколько задерживается (— 5 нс) .

Благодаря этому обратная связь через транзисторы 8 и 9 и резисторы 6 и 7 не успе- » вает скомпенсировать большое изменение дифференциального напряжения на базах транзисторов 1 и 2 (как это происходит в известных схемах), возникающее от изменения входных токов. Таким образом, в резисторах 10 и 11 на время переходного процесса достигается так называемый эффект динамического увеличения тока, и время переключения выходного напряжения значительно уменьшается. Кроме этого, и ток стабилитрона имеет конечную минимальную величину (2(1 -+ R<<>> -1 (®) R+, а напряжение на нем практически постоянно в процессе переключения.

При черезмерном увеличении сопротивления резистора 15 увеличивается выброс тока в резисторах 10 и 11, но уменьшается ток стабилитрона, и увеличиваются колебания напряжения на нем во время переходного процесса. Первое увеличивает быстродействие, второе — уменьшает. Таким образом, существует оптимальное сопротивление резистора 15, которое, как показали расчеты, подтвержденнь;е экспериментально, определяется из условия, что постоянная времени RC-цепи, подключенной к базам транзисторов 8 и 9 примерно на порядок меньше исходного (без 15 и 16) времени переключения. Аналогичные результаты получаются и при другом исходном состоянии компаратора.

Применение предлагаемого изобретения позволяет повысить быстродействие монолитно о компыратора в 4 — 6 раз. практически не увеличивая потребляемую мощность.

Формула изобретения

Компаратор, содержащий дифференциальный каскад на транзисторах, эмиттеры которых через стабилитрон соединены с общей шиной, базы подключены к первой и второй входным клеммам, а коллекторы через первый и второй нагрузочные резисторы перекрестно соединены с базами транзисторов дифференциального каскада и подключены к эмиттерам каскадных транзисторов, базы которых объединены, а коллекторы подключены к шине питания через третий и четвертый нагрузочные резисторы, коллектор первого каскадного транзистора и катод диода объединены и соединены с выходной клеммой, а анод диода подключен к коллектору второго каскадного транзистора, отличающий ся тем, что, с целью повышения быстродействия, в него введен транзистор и резистор, причем эмиттеры транзисторов дифференциального каскада соединены через введенный резистор с базами каскадных тра нзисторов и эмиттером введенного транзистора. база которого соединена с коллектором второго каскадного транзистора, а коллектор — с шиной питания.

Источники информации, принятые во внимание при экспертизе

1. Алексеенко А. Г. Основы микросхемотехники. М, Советское радиа, 1966.

2. Авторское свидетельство СССР № 604145; кл. Н 03 К 5/20, 1975 (прототип).

813753

12

Составитель Л. Николаева

Редактор Л. Повхан Техред А. Бойкас Корректор М. Коста

Заказ 422/78 Тираж 988 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и оз крытий ! 13035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4