Компаратор

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАHHE „„813757

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 27.03.79 (21) 2760670/18-21 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл.

Н 03 К 5/22//

G 05 В 1/01

Госудерстеенный комитет (53) УДК 621 374. 5 (088.8) Опубликовано .5.03.81. Бюллетень № 10 по делам изобретений и открытий

Дата опубликования описания 25.03.81 (72) Автор изобретения

В. П. Медведев (7! ) Заявител ь (54) КОМПАРЛТОР

Изобретение относится к измерительной технике, в частности к измерению постоянных и переменных напряжений и токов при цифровой обработке сигналов.

Известны компараторы, выполненные на дискретных элементах, например на подобранных транзисторных дифференциальных парах (1).

Недостатком известных компараторов является ограниченная разрешающая способность.

Известен также компаратор, содержащий дифференциальный усилитель, диодно-резистивную цепь и усилитель-ограничитель (2).

Недостатками такого компаратора являются невысокая точность, стабильность и ограниченная разрешающая способность.

Цель изобретения — повышение точности, стабильности и разрешающей способности сравнения сигналов постоянного и переменного токов малых уровней.

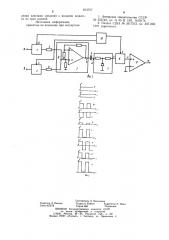

Указанная цель достигается тем, что в компаратор, содержащий дифференциальный усилитель, диодно-резисторную цепь и усилитель-ограничитель, введены три ключа, блок управления ключами, два суммирующих резистора и конденсатор, причем х вход днфференциального усилителя через суммирующие резисторы и два ключа соединен с входными шинами, а выход — через последовательно соединеннные конденсатор, диодно-резисторную цепь и третий ключ сое5 динен с входом усилителя-ограничителя, при этом, блок управления ключами соединен с входами каждого из трех ключей.

На фиг. 1 представлена функциональная схема компаратора; на фиг. 2 — временные

10 диаграммы.

Схема содержит ключи 1 и 2, на входы которых подаются входные сигналы, подлежащие сравнению, выходы которых через суммирующие резисторы 3 и 4 подключены ко входу дифференциального усилителя 5.

15 Выход дифференциального усилителя 5 через разделительный конденсатор 6 подключен ко входу диодно-резисторной цепи 7, выход которой, в свою очередь, через ключ 8 подключен ко входу усилителя-ограничителя 9. " Выходной сигнал усилителя-огра2" ничителя является выходом компаратора.

Для управления ключами 1, 2 и 8 на их входы подаются сигналы возбуждения от блока 10 управления ключами, который может работать как в автоколебательном, так

813757 и в режиме синхронизации внешним сигналом.

Предлагаемый компаратор работает следующим образом.

Входные сигналы постоянного тока противоположной полярности подлежащие сравнению (один из которых, опорный, показан на фиг. 2 а и б), подаются на входы ключей 1 и 2, »а другие входы которых подаются сигналы возбуждения прямоугольной формы и скважности Q = 2 (фиг. 2 в. г и к)

f0 от блока 10 управления ключами и открывают эти ключи одновременно. Когда ключи

1 и 2 открыты, на суммирующих резисторах

3 и 4 в точке их соединения происходит вычитание сигналов входных источников. (на фиг. 2 скважность Q сигналов управлеiIHB равна 2, однако она может быть любой).

I1n;Ii He!i!I IH разность (фиг. 2 д) усиливается дифференциальным усилителем 5 (фиг. 2е) и Ieðnç разделительный конденсатор б поьастся на диодно-резисторную цепь 7 (фиг. 2 ж), где отрицательная полуволна

20 напряжения ограничивается диодом, а положительная полуволна (фиг. 2 и) подается на вход ключа 8, который открывается с небольшим запаздыванием относительно открывания ключей 1 и 2 и пропускает положительные полуволны ко входу (фиг. 2 1) усилителя-ограничителя 9. Усиленный и ограниченный сигнал на выходе усилителяогpoliliч33тсля я33лястся выходцы,i сигналом компаратора. При очень малом сигнале на

l3xn, п 3, nHлите 1Н-nH!3ани чите 1R 9 H,IH fipH его отсутсгвии выходной сигнал усилителяограничителя 9 соответствует уровню логического «О», ра зному О,! - — 0,5 В. Г1ри увеличении входного сигнала,1n Г4! порог, выходной сигнал усилителя-ограничителя изменяет сНос состояние и соответствует уров° ню логической «1». равной 2,4--5 В. Усилите.3ь-ограничитель 9 является компаратороА напряжения.

Суммирующие резисторы 3 и 4 могут

40 быть подключены либо к одному входу дифференциального усилителя ..(фиг. ), либо по одному резистору на каждый отдельный вход дифференциального усилителя 5. В последнем случае источники входных сигналов должны быть оди3 аковой полярности или фазы. Ключи I, 2 и 8 могут быть как последовательного, так и параллельного типа, т. е. они могут быть включены как iinследовательно с входными сигналами, так и параллельно. В последнем случае ко входам ключей 1 и 2 могут быть подключены дополнительные резисторы, чтобы не закорачивать источники входных сравниваемых сигналов. При сравнении переменных напряжений эти напряжения синхронизированы друг с другом и с сигналами управления ключей 1, 2 и 8, вырабатываемых блоком 10 управления ключей который в этом случае работает в режиме синхронизации внешним сигналом.

В компараторе на выходе дифференциаль ного усилителя 5 включен разделительный конденсатор 6, предназначенный для разделения постоянной составляющей сигнала, т. е. дрейфа дифференциального усилителя 5, от полезного переменного сигнала, что позволяет снизить дрейф дифференциального усилителя 5 и увеличить его коэффициент усиления в 20-300 раз. Ключ 8 предназначен для фазочувствительной демодуляции переменного сигнала дифференциального усилителя 5. Однако основное назначение его — подавление выбросов на выходе усилителя 5. диодно-резисторная цепь предназначена для ограничения сигнала отрицательной полярности, который не изменяет состояние усилителя-ограничителя 9, а лишь уменьшает величину его выходного уровня логического «О», что улучшает работу схемы.

Основное преимущество и отличие схемы предлагаемого компаратора от известной заключается в том, что сравнение сигналов в компараторе происходит на входе дифференциального усилителя 5 в суммирующих резисторах 3 и 4 которые являются практически линейными и бездрейфовыми элементами. Для обеспечения точности, стабильности и разрешающей способности сравниваемых сигналов малых уровней в предлагаемом компараторе применяются ключи

1 и 2 на полевых транзисторах противоположного типа проводимости, например В ключах 1 и 8 п-канальные, а в ключе 2 рканальный полевые транзисторы с изолированным затвором. При этом достигается высокая компенсация дрейфа этих ключей.

Можно применять в ключах 1, 2 и 8 полевые транзисторы одного типа проводимости, но при этом в блоке 10 возбуждения ключей необходимо предусмотреть компенсацию дрейфа ключей; кроме того, в предлагаемом устройстве предусмотрена компенсация выбросов и дрейфа входных ключей, а также компенсация дрейфа усилителя и выбросов усилителя и выходного ключа.

Формула изобретения

Компаратор, содержащий дифференциальный усилитель, диодно-резисторную цепь и усилитель-ограничитель, отличающийся тем, что, с целью повышения точности, стабильности и разрешающей способности, в него введены три ключа, блок управления ключами, два суммирующих резистора, и конденсатор, причем вход дифференциального усилителя через суммирующие резисторы и два ключа соединен с входными шинами, а выход — через последовательно соединенные конденсатор, диодно-резисторную цепь и третий ключ соединен с входом усилителя-ограничителя, при этом, блок управ813757

uz.1

Составитель Л. Николаева

Редактор Л. Повхан Техред А. Бойкас Корректор Л. Иван

Заказ 422/78 Тираж 988 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и от крытий

113035, Москва, Ж вЂ” 35, Раушская иаб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4 ления ключами соединен с входами каждого из трех ключей.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 553742, кл. G 05 В 1/Ol, 1 6.08.74.

2. Патент США № 351 7215, кл. 307-235, 1970 (прототип).