Устройство для фазирования элек-тронного телеграфного приемника

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБВЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Социалистическик

Республик ()813808 (61) Дополнительное к авт. свид-ву— (22) Заявлено 26.06.79 (21) 2785059/18-09 (51) М.К . с присоединением заявки №вЂ” (23) Приоритет—

Н 04 L 7/02

Гевударстненный кемнтет

СССР но делам изобретений н открытий

Опубликовано 15.03.81. Бюллетень № 10

Дата опубликования описания 25.03.81 (53) УДК 621.394..662 (088.8) (72) Авторы изобретения

Н. В. Захарченко и А. С. Николаев

1>е

Ф (71) Заявитель

Одесский электротехнический институт свя и им. А. С. Попова (54) УСТРОЙСТВО ДЛЯ ФАЗИРОВАНИЯ ЭЛЕКТРОННОГО

ТЕЛЕГРАФНОГО ПРИЕМНИКА

Изобретение относится к технике телеграфной связи и может использоваться в устройствах передачи данных.

Известно устройство для фазирования электронного телеграфного приемника, содержащее стартстопный триггер, первую дифференцирующую цепь и последовательно соединенные задающий генератор, первый ключ, распределитель тактов и первый триггер, а также последовательно соединенные приемный блок, вторую дифференцирующую цепь и первый элемент И, ко второму входу которого подключен выход первого триггера 11).

Однако известное устройство имеет низкую точность и обладает медленным фазированием. 15

Цель изобретения — повышение точности и ускорение фазирования.

Для этого в устройство для фазирования электронного телеграфного приемника, содержащее стартстопный триггер, первую дифференцирующую цепь и последовательно соединенные задающий генератор, первый ключ, распределитель тактов и первый триггер, а также последовательно соединенные приемный блок, вторую дифференцирующую цепь и первый элемент И, ко второму входу которого подключен выход первого триггера, введены два элемента ИЛИ, по- следовательно соединенные второй триггер, второй элемент И и третья дифференцирующая цепь, а также последовательно соединенные третий триггер, четвертая дифференцирующая цепь, четвертый триггер, второй ключ, счетчик, дешифратор, третий элемент

И, пятый триггер и четвертый элемент И, выход которого подключен ко второму входу первого ключа, вход которого объединен с вторым входом второго ключа, а к второму входу четвертого элемента И подключен выход стартстопного триггера, к второму входу которого подключен выход первого элемента ИЛИ, к первому входу которого, объединенному с первым входом второго элемента ИЛИ, подключен выход первой дифференцирующей цепи, ко входу которой подключен выход пятого триггера, при этом соответствующий выход распределителя тактов подключен к вторым входам третьего элемента И, первого элемента ИЛИ и первому входу третьего триггера, а к BTQ813808 рому входу второго элемента ИЛИ подключен выход второго элемента И, выход вто рого элемента ИЛИ подключен к второму входу четвертого триггера и счетному входу счетчика, при этом выход первого элемента И подключен к второму входу третье- 5 го триггера, дополнительные выходы распределителя тактов подключены ко входам второго триггера, второй выход дешифратора подключен к второму входу пятого триггера, а ко входу третьей дифференцирующей цепи подключен выход приемного блока.

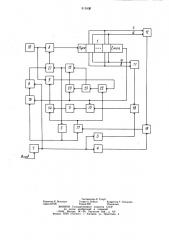

На чертеже представлена структурная электрическая схема предлагаемого устройства.

Устройство для фазирования электронного телеграфного приемника содержит рас-

2, 3, 4 и 5 соответственно, стартстопный триггер 6, приемный блок 7, первый и второй ключи 8, 9 соответственно, задающий генератор 10, первый, второй, третий, четвертый, пятый триггеры 11, 12, 13, 14, 15 соответственно, первый и второй элементы

ИЛИ 16, 17 соответственно,.первый, второй, третий и четвертый элементы И 18; 19, 20, 21 соответственно, счетчик 22, дешифратор 23.

Устройство работает следующим образом.

Стартовый переход, пройдя приемный блок 7, устанавливает стартстопный триггер 6 в единичное состояние. С выхода стартстопного триггера 6 сигнал поступает на четвертый элемент И 21, на другой вход которого поступает разрешающий сигнал с пятого триггера 15. С выхода четвертого элемента И 21 поступает управляющий сигнал на первый ключ 8 и разрешает прохождение тактов с задающего генератора

10 на распределитель 1. Распределитель 1 при своей работе вырабатывает такты, по которым производится регистрация посылок, а также четыре последовательности импуль- 4о сов — а, в, с и d. Последовательность а переводит первый триггер 11 в единичное состояние, последовательность в возвращает его в нулевое состояние. С выхода триггера 11 на элемент И 18 поступают сигналы запрещенных зон, внутри которых не должно быть фронтов при синфазной работе распределителя 1. Последовательность импульсов с переводит триггер 12 в единичное состояние, а последовательность d возвращает его в нулевое состояние. На выходе триггера 12 вырабатываются разрешенные зоны, которые формируются вокруг точек, в которых может произойти смена полярности сигнала при синфазном состоянии.

При синфазной работе распределителя 1 и отсутствии переходов внутри запрещенных зон подстройка фазы не производится. Если какая-либо смена полярности сигнала из единицы в ноль происходит во время запрещенной зоны, то на выходе дифференцирующей цепи 3 появляется импульс, который, пройдя элемент И 18, приходит на вход триггера 13 и устанавливает его в единичное состояние. Сброс триггера 13 в нулевое состояние производится по окончании работы распределителя 1, поэтому триггер 13 может быть переведен в единичное состояние один раз за стартстопный цикл. Переход ноль-единица с выхода третьего триггера 13 дифференцируется четвертой диф фере нцирую щей цепью 5 и попадает на вход четвертого триггера 14, переводя его в единичное состояние. Сигнал с выхода триггера 14 разрешает работу второго ключа 9. С выхода задающего генератора 10 через ключ 9 такты поступают на вход счетчика 22, который считает количество тактов, следующих с периодом, равным длительности одной посылки, попавших на его вход.

Дальнейшая работа схемы зависит от того, чем был вызван фронт сигнала, попавшего в запрещенную зону. Если фронт был вызван помехами в канале связи, то следом за ним будут идти фронты, совпадающие во времени с разрешенными зонами.

Первый из них выделяется на третьей дифференцирующей цепи 4, проходит элемент

И 19, элемент ИЛИ,17 и возвращает триггер 14 в нулевое состояние. Одновременно он устанавливает в исходное состояние счетчик 22. С выхода триггера 14 перестает поступать сигнал, разрешающий прохождение тактов с задающего генератора 10 на счетчик 22. В этом случае подстройка фазы не производится.

Если фронт, попавший в запрещенную зону, вызван асинфазной работой распределителя 1, то в дальнейшем остальные фронты данного стартстопного цикла распределителя 1 также будут попадать в запрещенные зоны. При этом до конца стартстопного цикла сброс триггера 14 и счетчика 22 не производится. Счетчик 22 продолжает подсчет тактов, поступающих с задающего генератора 10. Емкость счетчика равна количеству посылок в стартстопной комбинации. Выход счетчика подключен к дешифратору 23, который при исходном состоянии счетчика 22 или при окончании им счета выдает сигнал. Этот сигнал с выхода дешифратора 23 поступает на вход триггера

15, по которому производится установка последнего в единичное состояние. Инверсный выход дешифратора 23 подключен к элементу И 20. Так как счетчик 22 в данном стартстопном цикле начал счет, то он уже вышел из начального состояния, но к моменту окончания стартстопного цикла 0Н не успевает прийти в конечное состояние.

Следовательно, к моменту окончания стартстопного цикла сигнала на прямом выходе дешифратора 23 не будет, а сигнал с ин813808 версного выхода дешифратора 23 совпадает на элементе И 20 с сигналом окончания стартстопного цикла, пришедшим с распределителя 1. С выхода элемента И 20 сигнал попадает на триггер 15 и устанавливает его в нулевое состояние. Этот же стоповый сигнал с распределителя 1 устанавливает в исходное состояние триггер 13 и через элемент ИЛИ 17 стартстопный триггер 6.

С началом следующего стартстоп ного цикла стартстопный триггер 6 переходит в единичное состояние, но такты с задающего генератора 10 не попадают на распределитель 1, так как ключ 8 закрыт, потому что на элемент И 21 подается нулевой потенциал с триггера 15. Счетчик 22 продолжает считать такты и заканчивает счет в момент, непосредственно предшествующий моменту прихода первого фронта, который попал в запрещенную зону в предыдущем стартстопном цикле. Этот фронт и является истинным стартовым переходом. В момент окончания работы счетчика 22 срабатывает дешифратор 23 и устанавливает триггер 15 в единичное состояние. С триггера

15 на элемент И 21 подается разрешающий сигнал. Этот сигнал через дифференцирующую цепь 2 и элемент ИЛИ 17 устанавливает в нулевое состояние триггер 14, который закрывает ключ 9. С приходом истинного стартового перехода стартстопный триггер 6 переходит в единичное состояние и начинается следующий стартстопный цикл.

Положительный эффект заключается в уменьшении вероятности искусственного вывода распределителя из фазы и ускорении процесса фазирования.

Формула изобретения

Устройство для фазирования электронного телеграфного приемника, содержащее стартстопный триггер, первую дифференцирующую цепь и последовательно соединенные задающий генератор, первый ключ, распределитель тактов и первый триггер, а также последовательно соединенные приемный блок, вторую дифференцирующую цепь и первый элемент И, ko второму входу которого подключен выход первого тригге5 ра, отличающееся тем, что, с целью повышения точности и ускорения фазирования, введены два элемента ИЛИ, последовательно соединенные второй триггер, второй элемент И и третья дифференцирующая цепь, а также последовательно соединенные третий триггер, четвертая дифференцирующая цепь, четвертый триггер, второй ключ, счетчик, дешифратор, третий элемент И, пятый триггер и четвертый элемент И, выход которого подключен ко второму входу первого ключа, вход которого объединен с вторым входом второго ключа, а к второму входу четвертого элемента И подключен выход стартстопного триггера, к второму входу которого подключен выход первого элемента ИЛИ, к первому входу которого, объ20 единенному с первым входом второго элемента ИЛИ, подключен выход первой дифференцирующей цепи, ко входу которой подключен выход пятого триггера, при этом соответствующий выход распределителя

25 тактов подключен к вторым входам третьего элемента И, первого элемента ИЛИ и первому входу третьего триггера, а к второму входу второго элемента ИЛИ подключен выход второго элемента И, выход второго элемента ИЛИ подключен к второму входу зp четвертого триггера и счетному входу счетчика, при этом выход первого элемента И подключен к второму входу третьего триггера, дополнительные выходы распределителя тактов подключены ко входам второго триггера, второй выход дешифратора подключен к второму входу пятого триггера, а ко входу третьей дифференцирующей цепи подключен выход приемного блока.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 340108, кл. Н 04 L 7/02, 1970 (прототип).

813808

Составитель Е. Голуб

Редактор К. Волощук Техред А. Бойкас Корректор Г. Назарова

Заказ 427/81 Тираж 698 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4