Устройство фазирования по циклам всистеме передачи данных

Иллюстрации

Показать всеРеферат

О Il И С А Н И Е ()813809

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических реслублик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ.(61) Дополнительное к авт. свид-ву— (22) Заявлено 04.06.79 (21) 2776884/18-09 (51) М. Кл. с присоединением заявки №вЂ”

Н 04 L 7/04

Гееударстеевкый комитет

СССР ао делам нзееретеккй и еткрыткй (23) Приоритет—

Опубликовано 15.03.81. Бюллетень №10

Дата опубликования описания 25.03.81 (53) УДК 621.394. .662 (088.8) А. А. Беляков, Л. А. Вишняков, Л. К. Дуничева, В. А. Перегудов и М. С. Цыпина

/ . (р(« (,, (/ ,,«j

1 (72) Авторы изобретения (7l) Заявитель (54) УСТРОЙСТВО ФАЗИРОВАНИЯ ПО ЦИКЛАМ

В СИСТЕМЕ ПЕРЕДАЧИ ДАННЫХ

Изобретение относится к технике электросвязи и может использоваться для фазирования по циклам в системах передачи данных (СПД), использующих амплитуднофазовую модуляцию (АФМ).

Известно устройство фазирования по циклам в системе передачи данных, содержащее последовательно соединенные счетчик цикла, блок дешифраторов, блок управления, формирователь фазирующих комбинаций, накопитель, кодер, элемент ИЛИ и преобразователь, а также скремблер, вход 10 которого объединен со входом формирователя фазирующих комбинаций, а выход скремблера подключен к второму входу накопителя, выход которого подключен к второму входу элемента ИЛИ (1).

Однако такое устройство имеет большую вероятность ложного фазирования по циклам;

Цель изобретения — уменьшение вероятности ложного фазирования по циклам.

Для достижения этой цели в устройство 20 фазирования по циклам в системе передачи данных, содержащее последовательно соединенные счетчик цикла, блок дешифраторов, блок управления, формирователь фазирующих комбинаций, накопитель, кодер, элемент ИЛИ и преобразователь, а также скремблер, вход которого объединен со входом формирователя фазирующих комбинаций, а выход скремблера подключен к второму входу накопителя, выход которого подключен к второму входу элемента ИЛИ, введены последовательно соединенные триггер и элемент И, к второму входу которого подключен тактовый выход преобразователя, информационный выход которого подключен к первому входу триггера, второй вход которого объединен со вторым входом блока управления, при этом выход триггера подключен к первому входу счетчика цикла, к второму входу которого подключен выход элемента И.

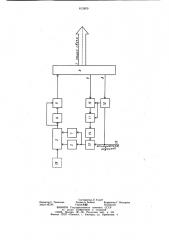

На чертеже представлена структурная электрическая схема предложенного устройства.

Устройство фазирования по циклам в системе передачи данных содержит скремблер 1, формирователь 2 фазирующих комбинаций, накопитель 3, кодер 4, элемент ИЛИ 5, преобразователь 6, имеющий выход 7 соединенный с каналом связи, информационный выход 8 и тактовый выход 9, триггер 10, 813809 счетчик 11 цикла, элемент И 12, блок 13 управления, блок 14 дешифраторов, причем на другой вход накопителя подана информация с источника 15 информации, а вторые входы блока управления и триггера соединены с цепью 16 циклового фазирова- 5 ния.

Устройство работает следующим образом.

При обнаружении расхождения цикловых фаз на передаче и приеме приемник форми 0 рует сигнал цикловое фазирование, который по цепи 16 поступает на блок 13 управления и на триггер 10. Триггер 10 включается, сигналом со своего выхода осуществляет сброс счетчика 11 цикла и запрещает прохождение тактовых импульсов с выхода 9 преобразователя через элемент И 12 на вход счетчика 11 цикла. Счетчик 11 цикла установлен в исходное состояние.

Первым после прихода сигнала асцикловое фазирование» сигналом .АМ/ФМ с выхода 8 преобразователя, осуществляющим

20 разделение в преобразователе 6 информации по дискретным подканалам с АМ и ФМ, включается триггер 10, который прекращает формировать сигнал «сброс» счетчика 11 цикла и разрешает прохождение через элемент И 12 на вход счетчика 11 цикла тактовых импульсов. Счетчик 11 цикла начинает отсчитывать циклы передачи блоков.

Блок 14 дешифраторов обеспечивает синхросигналами и управляющими си" алами, находящимися в необходимых фазовых со- 30 отношениях с началом передаваемых блоков, все узлы предложенного устройства.

Благодаря этому начало работы первого переда ваемо го блока и всех последующих после фазирования по циклам синхронизировано сигналом АМ/ФМ таким образом, 35 что все. нечетные разряды блоков передаются по дискретному подканалу с AN, а все четные разряды блоков передаются по дискретному подканалу с ФМ.

Сигнал «цикловое фазирование», кроме 40 того, поступает в блок 13 управления, откуда после стробирования сигналами управления с блока 14 дешифраторов один раз за цикл в импульсном виде поступает на формирователь 2 фазирующих комбинаций и скремблер 1.

Формирователь 2 фазирующих комбинаций и скремблер 1 осуществляют формирование в накопителе в процессе фазирования по циклам передаваемого блока. Для устойчивой работы систем автоматической регулировки в преобразователе 6 во время фазирования по циклам не принципиально необходимо содержанйе разрядов блока, передаваемых по дискретному подканалу с АМ.

Поэтому формирователь 2 фазирующи 1 комбинаций по импульсному сигналу «цикловое фазирование» с выхода блока 13 управле ния осуществляет запись в нечетные разряды накопителя 3 фазирующей комбинации, объем которой в предложенном устройстве доведен до 50О/р передаваемого блока, а скремблер 1 по этому же сигналу осуществляет запись в четные разряды накопителя 3 символов псевдослучайной последовательности.

По окончании фазирования по циклам сигнал «цикловое фазирование» приемника снимается и в накопитель начинает поступать информация с источника 15 информации.

Таким образом, в результате синхронизации работы счетчика 11 цикла сигналами АМ/ФМ однозначно определяются разряды блока, которые передаются по дискретным подканалам с АМ и ФМ. Благодаря этому объем фазирующей комбинации в зависимости от предъявленных требований может быть увеличен до 50 /ц передаваемого блока. В результате этого значительно уменьшается вероятность ложного фазирования по циклам СПД.

Формула изобретения

Устройство фазирования по циклам в системе передачи данных, содержащее последовательно соединенные счетчик цикла, блок дешифраторов, блок у.правления, формирователь фазирующих комбинаций, накопитель, кодер, элемент ИЛИ и преобразователь, а также скремблер, вход которого объединен со входом формирователя фазирующих комбинаций, а выход скремблера подключен к второму входу накопителя, выход которого подключен к второму входу элемента ИЛИ, отличающееся тем, что, с целью уменьшения вероятности ложного фазирования по циклам, введены последовательно соединенные триггер и элемент И, к второму входу которого подключен тактовый выход преобразователя, информационный выход которого подключен к первому входу триггера, второй вход которого объединен со вторым входом блока управления, при этом выход триггера подключен к первому входу счетчика цикла, к второму входу которого подключен выход элемента И.

Источники информации, принятые во внимание при экспертизе

1. Дуплексная универсальная мультиплексная каналообразующая аппаратура.

Техническое описание Зт2 131025 ТО, 1978 (прототип) .

813809

М

Редактор С. Тимохина

Заказ 427/81

Составитель Е. Голуб

Техред А. Бойкас Корректор Г. Назарова

Тираж 693 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4