Цифровой интегратор

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (»)815726

ИЗОБРЕТЕН ИЯ

Союз Советскии

Социалистических

Республик

Ф

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 15.12.78 (21) 2697493/18-2! с присоединением заявки №вЂ” (23) Приоритет— (51) Я Кл 3

G 06 F 7/52

Гасударственный комитет по делам изобретений и открытий

Опубликовано 23.03.81. Бюллетень № 11

Дата опубликования описания 28.03.81 (53) УДК 681.327 (088,8) (72) Авторы изобретения

А. М. Петух, Д. Т. Ободник и Н. М. Hàíè (7!) Заявитель

Винницкий политехнический институт (54) ЦИФРОВОЙ ИНТЕГРАТОР

Изобретение относится к вычислительной и информационно-измерительной технике, а также к системам автоматического управления и может найти применение в системах числового программного управления, а также в измерительных и вычислительных устройствах.

Известен цифровой интегратор параллельного переноса, содержащий регистр управляющего кода и накопительный сумматор (1).

Недостатком этого устройства является сложность конструкции.

Наиболее близким к предлагаемому по технической сущности является цифровой интегратор, содержащий М-разрядный регистр, выходы N младших рязрядов которого подключены к первым N входам логи- 15 ческого блока умножителя, N-разрядный счетчик, вход которого соединен с входной шиной, а выходы — с вторыми N входами логического блока умножителя (2).

Недостатком его является большая погрешность, вызываемая неравномерностью следования импульсов на выходе.

Цель изобретения — повышение точности.

Для достижения указанной цели в цифровой интегратор, содержащий М-разрядный регистр, выходы N младших разрядов которого подключены к первым входам логического блока умножителя, N-разрядный счетчик, вход которого соединен с входной шиной, а выходы — с вторыми входами логического блока умножителя, введен накопительный сумматор, тактовый вход которого подключен к входной шине, вход переноса — к выходу логического блока умножителя, кодовые входы — к выходам М-N старших разрядов М-разрядного регистра, а выход — к выходной шине.

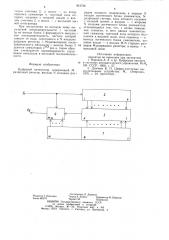

На чертеже представлена функциональная схема цифрового интегратора.

Цифровой интегратор содержит М-разрядный регистр 1 управляющего кода, Nразрядный счетчик 2, логический блок 3 умножителя и накопительный сумматор 4.

Выход сумматора подключен к выходной шине.

Выходы М-N старших разрядов регистра 1 подключены к кодовым входам накопительного сумматора 4, а N младших разрядов — к 1х1 первым входам блока 3, N других входов которого подключены к вы815726

Формула изобретения

Составитель Л. Дарьина

Реда кто р Т. Киселева Техред А. Бойкас Корректор М. Шароши

Заказ 662/79 Тираж 745 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проекуная, 4 ходам счетчика 2, а выход — ко входу переноса сумматора 4, тактовый вход которого соединен с входной шиной и входом счетчика 2, а выход — с выходной шиной интегратора.

При поступлении на входную шину импульсной последовательности с частотой

fo на выходе блока 3 формируется импульсная последовательность, частота которой зависит от кода, записанного в N младших разрядах регистра 1. Неравномерная последовательность импульсов с выхода блока 3 10 делится сумматором 2 раз и, таким образом уменьшается неравномерность следования импульсов в выходной последовательности.

Цифровой интегратор, содержащий Мразрядный регистр, выходы N младших разрядов которого подключены к первым Х входам логического блока умножителя, Nразрядный счетчик, вход которого соединен с входной шиной, а выходы — с вторыми

N входами логического блока умножителя, отличающийся тем, что, с целью повышения точности, в него введен накопительный сумматор, тактовый вход которого подключен к входной шине, вход переноса — к выходу логического блока умножителя, кодовые входы — к входам М-N старших разрядов М-разрядного регистра, а выход — к выходной шине.

Источники информации, принятые во внимание при экспертизе

1. Воронов А. А. и др. Цифровые аналоги в системах автоматического управления. М-Л., АН СССР, 1960, с. 57.

2. Данчеев В. П. Цифро-частотные вычислительные устройства. М., «Энергия», 1976, с. 24 (прототип) .