Цифровой частотный детектор

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ((((815863

Союз Советсиик

Соцналистичесиик республии (61) Дополнительное к авт. саид-ву(22) Заявлено 01.06.7g (21) 2778804/18-21 (51)M. Кл. с присоединением заявки %в

Н 03 0 13/00

Грсудэкствеииый комитет

СССР кк делам изобретений и етирытий (23) Приоритет—

Опубликовано 23..03.81. Бюллетень М 11

Дата опубликования описания 25.03.81 (53) УД К 62 1. 374 (088.8) f -".: .

В. А. Могунов, К. Д. Лазинцев и P. Н. Туровский (!

„ (72) Авторы изобретения (7! ) Заявитель (54) ЦИФРОВОЙ. ЧАСТОТНЫЙ ДЕТЕКТОР

Изобретение относится к радиотехнике и может быть использовано в частотных системах телемеханики.

Известен частотный дискриминатор, содержащий формирователь импульсов, узел задержки, фазосдвигающий элемент, 5 дополнительный формирователь, схемы совпадения накопительные и выходные элементы 1) .

Недостатком известного дискримина10 тора является невысокая стабильность, вызванная наличием резонансного четырехполюсника и работой.на его крутой части фазовой характеристики.

Наиболее близким техническим решением к прецлагаемому является цифровой частотный цетектор, содержащий формирователь импульсов, вход которого является вхоцом устройства, элемент задержки, триггер, первый выход которого подключен к первому .входу логического элемента, соединенные последовательно реверсивный счетчик и дешифратор (2Д.

Недостатком устройства является его. низкое быстродействие.

Бель изобретения - повышение быст- . роцействия устройства.

Поставленная цель достигается тем, что в цифровой частотный детектор, содержащий формирователь импульсов, вход которого является входом устройства, элемент задержки, триггер, первый выход которого подключен к первому входу логического элемента, соединенные последовательно реверсивный счетчик импуль- . сов и дешифратор, ввецены делитель частоты, расширитель импульсов, ключ и накопительные блоки, причем вход устрой ства соединен со вхоцом триггера и вто-! рым входом логического элемента, пер-, вый и второй выхоцы триггера соединены соответственно со входами направления счета реверсивного счетчика импуль« сов, выхоц формирователя импульсов соединен со входом расширителя импульсов, выход которого подключен к третьему входу логического элемента и к упрявляюще815863, му вхоцу ключа, коммутируемый переход которого включен межцу управляющим входом делителя частоты и счетным входом реверсивного счетчика импульсов, а выход логического элемента подключен ко входу установки нуля делителя частоты и входу элемента задержки, выход которого подключен ко входу установки реверсивного счетчика импульсов, и вхо» дам записи накопительных блоков, выходы которых являются выхоцами устройства, информационные входы которых соединены с выходами дешифратора, а выхоцы являются выхоцами устройства.

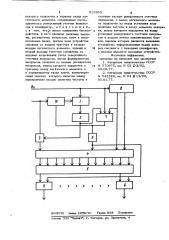

На чертеже приведена структурная

15 электрическая схема устройства.

Устройство содержит формирователь

1 импульсов, расширитель 2 импульсов, ключ 3, счетчик 4 импульсов, реверсивный дешифратор 5, накопительные блоки

6, логический элемент 7, триггер 8, элемент 9 задержки, делитель 10 частоты.

Устройство работает следующим образом.

Импульсы входной частоты поступают на входы формирователя 1, логического элемента 7 и триггера 8. На выходе триггера 8 импульсы следуют с частотой, равной половине входной, период этой частоты равен времени опрецеления значения входной частоты. Одновременно с перебросом выхода триггера 8, импульсы входной частоты устанавливают выход формирователя 1 и логического элемента 7 в единичное состояние. "Единичное" напряже- 35 ние на выхоце лог ического элемента 7 устанавливает целитель 1 0 в счетный режим. На выходе делителя 10 формируются отрицательные импульсы, имеющие пе.риоц следования равный среднему периоду 40 вхоцной частоты, и сдвинутые относительно импульсов входной частоты на время, 1„

Появившийся со сдвигом на Ф выхоц- ной импульс делителя 10 возвращает формирователь 1 в нулевое" состояние. С

В

45 выхода формирователя 1 сформированные импульсы поступают на вход расширителя 2 импульсов, где их длительность увеличивается в К раз. Величина К выбирается такой, чтобы импульс максимальной длительности после расширения не превышал величины минимального периода входного сигнала. Таким образом, за время анализа на выхоце расширителя 2 импульсов появляется пара импульсов. Если длительность импульсов пары одинакова, то входная частота равна частоте импульсов с выхода делителя 10. Если длитель4 ность второго импульса больше первого, то входная частота больше частоты с выхода делителя 10, а если второй импульс короче первого, то входная частота меньше частоты с выхода делителя

10. В количественной величине разницы длительностей импульсов заключена количественная величина отклонения входной частоты от величины частоты сформированной на выходе делителя 10. Импульсы с выхода расширителя 2 импульсов управляют ключом 3, который пропускает на счетный вхоц реверсивного счетчика

4 серию импульсов опорной частоты. Выходы триггера 8 управляют направлением счета реверсивного счетчика 4, при единичном состоянии первого выхода триггера 8 импульсы опорной частоты суммируются, а при "нулевом - вычитаются.

Поцключенный к выходам разрядов реверсивного счетчика 4 дешифратор 5 выдает на одном из своих выходов сигнал зависящий or числа записанного в реверсивном счетчике 4. После окончания расширенного импульса заканчивается время анализа и на выходе логического элемента 7 формируется импульс, который устанавливает делитель 10 в исхоцное состояние и блокирует поступление на его вхоц импульсов опорной частоты. Элемент

9 задержки при поступлении на его вход отрицательного перепада напряжения формирует на своем выходе короткий отрицательный импульс, задержанный относительно пере паца напряжения на время, достаточное цля завершения переходных процессов в реверсивном счетчике 4 и дешифраторе 5. Импульс с выхода элемента 9 задержки дает разрешение на запись в накопительные элементы 6 информации с выхода дешифратора 5 и возвращает реверсивный счетчик 4 в исходное состояние. Схема готова к следующему циклу работы. Когца в накопительных элемента х 6 на ка пливается информация, достаточная цля принятия решения о величине вхоцной частоты, на выхоце одного из. накопительных элементов 6 появляется сигнал, свицетельствующий о нахождении вхоцной частоты в интервале частот, определяемом цешифратором 5.

Формула изобретения

Цифровой частотный цетектор, содержащий формирователь импульсов, вхоц которого является входом устройстве, элемент задержки, триггер, первый выход

815863

ВНИИПИ Заказ 1050/87 Тираж 988 Подписное

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4 которого подключен к первому вхоцу логического элемента, соединенные после- . цователы о реверсивный счетчик импульсов и цешифратор, о т л и ч а ю щ и йс я тем, что с целью повышения быстродействия, в него введены делитель часто- ты, расширитель импульсов, ключ и накопительные блоки, причем вход устройства соецинен со входом триггера и вторым вхоцом логического элемента, первый и 10 второй выходы триггера соединены со вхоцами направления счета реверсивного счетчика импульсов, выход формирователя импульсов соединен со входом расширителя импульсов, выхоц которого подключен к is третьему вхоцу логического элемента и к управляющему входу ключа, коммутируемый переход которого включен между управляемым входом делителя частоты и счетным вхсцом реверсивного счетчика импульсов, а выхоц логического элемен» та поцключен ко входу установки нуля целителя частоты и входу элемента задержки, выход которого подключен ко входу установки реверсивного счетчика импуль- сов и входам записи накопительных блоков, выходы которых являются выходами . устройства, информационные входы которых соецинегы с выходами цешифратора, а выходы являются выходами устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

J4 570975, кл. Н 03 О З/02е

30. 08. 77.

2. Авторское свидетельство СССР

N 542328, кл. Н 03 Q 13/00, 05. 01. 77.