Селектор импульсов по частотеследования

Иллюстрации

Показать всеРеферат

((() 815891

ОЛ ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву— (22) Заявлено 17.05.79 (21) 2767040/18-21 с присоединением заявки №вЂ” (53) М. Кл з

Н 03 К 5/22

Гооударствеиный комитет

СССР (23) Приоритет— ао делам изобретений и открытий

Опубликовано 23.03.81. Бюллетень №11

Дата опубликования описания 28.03.81 (53) УДК 621.374..382 (088. 8) С. Н. Грибакии, Б. Н. Никифоров, А. Б. Ско ( и В. Е. Шермаков рБхниик(иа ааааа% 1{00 7Et;1 (72) Авторы изобретения (71) Заявитель (54) СЕЛЕКТОР ИМПУЛЬСОВ ПО ЧАСТОТЕ

СЛЕДОВАНИЯ

Изобретение относится к. импульсной технике.

Известен селектор импульсов, содержащий одновибратор, элемент задержки, элемент И, RS-триггер и дифференцирующий элемент. Дифференцирующий элемент включен между первым выходом одновибратора и первым входом элемента И. Второй выход одновибратора подключен ко входу элемента задержки, а второй вход элемента И соединен с выходом триггера, один вход которого связан с выходом элемента задержки а другой — со входом одновибратора (1) .

Недостатком известного селектора является узкий диапазон селектирования.

Наиболее близким по технической сущности к предлагаемому является селектор импульсов, содержащий входной триггер, один вход которого соединен с входной шиной, а выход через элемент задержки соединен с первым входом RS-триггера, второй вход которого подключен к входной шине, а выход соединен с одним из входов элемента И (2).

Недостатком известного селектора является малый динамический диапазон.

Цель изобретения — расширение динамического диапазона.

Поставленная цель достигается тем, что в селектор импульсов, содержащий входной триггер, один вход которого соединен с входной шиной, а выход через элемент задержки соединен с первым входом RS-триггера, второй вход которого подключен к входной шине, а выход соединен с одним из входов элемента И, введены последовательно включенные интегратор и пороговый элемент, выход которого соединен с вторыми входами входного триггера и элемента И, а вход интегратора подключен к выходу входного триггера.

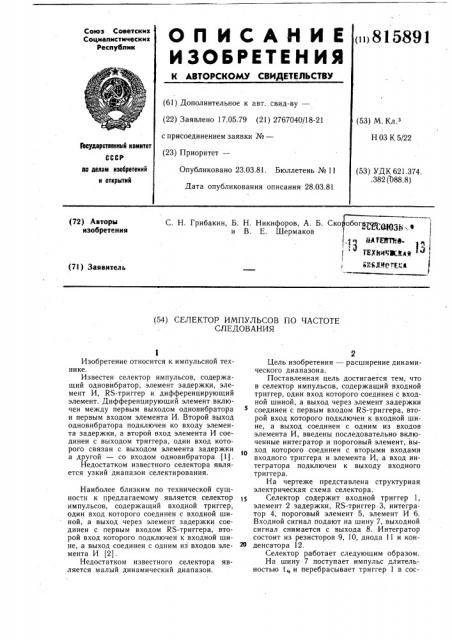

На чертеже представлена структурная электрическая схема селектора.

Селектор содержит входной триггер 1, элемент 2 задержки, RS-триггер 3, интегратор 4, пороговый элемент 5, элемент И 6.

Входной сигнал подают на шину 7, выходной сигнал снимается с выхода 8. Интегратор состоит из резисторов 9, 10, диода 11 и конденсатора 12.

Селектор работает следующим образом.

На шину 7 поступает импульс длительностью {„и перебрасывает триггер 1 в сос815891

Формула изобретения

Составитель А. Артюх

Техред А. Бойкас Корректор В. Бутяга

Тираж 9SS Поднисное

ВНИИПИ Государственного комитета СССР но делам изобретений и открытий

1 l 3035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», r. Ужгород, ул. Проектная, 4

Редактор Н. Рогулич

Заказ 695/88 тояние U . Через время, определяемое элементом 2 задержки — tq (равное длительности входного импульса t<), на первом входе

RS-триггера 3 появляется уровень UT u RSтриггер 3 становится чувствительным по второму входу. С появлением на выходе триггера 1 уровня UT конденсатор интегратора 4 начинает заряжаться с постоянной времени

= Rq С до уровня срабатывания порогового элемента 5. При этом пороговый элемент 5 перебрасывается в состояние U» и тем самым сбрасывает триггер 1 по второму входу в исходное состояние. Интегратор

4 начинает разряжаться с постоянной времени т = Ri С и пороговый элемент 5 перебрасывается в исходное состояние. Через время t3 на первом входе RS-триггера 3 1g установится начальное состояние «О» и он становится нечувствительным ко второму входу. Возникший короткий импульс на выходе порогового элемента 5 проходит через элемент И 6 на выход устройства, так как на выходе триггера 3 в этом случае находится уровень «1» при котором элемент И

6 открывается по первому входу.

Если. во время заряда конденсатора интегратора 4 на шине 7 появляется хотя бы один импульс, то триггер 3, находящийся в это время в состоянии чувствительном ко второму входу, перебрасывается по выходу в состояние «О». После срабатывания порогового элемента 5, все устройство восстанавливается в исходное состояние, аналогичным образом, но импульс с выхода порогового элемента 5 через элемент И не проходит, и на выходе устройства не появляется ни од-. ного импульса.

Время выдержки устройства определяется временем заряда конденсатора интегратора 4 до уровня напряжения порога порогового элемента 5.

Селектор импульсов по частоте следования, содержащий входной триггер, один вход которого соединен с входной шиной, а выход через элемент задержки соединен с первым входом RS-триггера, второй вход которого подключен к входной шине, а выход соединен с одним из входов элемента И, отличающийся тем, что, с целью расширения динамического диапазона, в него введены последовательно включенные интегратор и пороговый элемент, выход которого соединен с вторыми входами входного триггера и элемента И, а вход интегратора подключен к выходу входного триггера.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 549885, кл. Н 03 К 5/20, 06.12.76.

2. Патент ФРГ № 1180840, кл. 21 е 36/03, 21. 09. 76.