Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (ii)815902

Ф (61) Дополнительное к авт. свид-ву— (22) Заявлено 16.05.79 (21) 2766402/18-21 с присоединением заявки №вЂ” (23) Приоритет— (51) М Кл з

Н 03 К 13/09

Гооударотееииык комитет

СССР во делам иаооретеиий и открытий

Опубликовано 23.03.81. Бюллетень № 11

Дата опубликования описания 28.03.81 (53) У@К 681.325 (088.8) Ъю

В. А. Блохин, В. П. Сафронов, В. П. Ше ченко

В. М. Шляндин и А. Г. Милехи (72) Авторы изобретения

I (71) Заявитель

Пензенский политехнический инст (54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к электроизмерительной технике и используется в информационно-измерительных системах.

Известен аналого-цифровой преобразователь, содержащий два .блока аналоговой свертки, образованные дифференциальными каскадами, причем инверсный (неинверсный) выход предыдущего дифференциального каскада соединен с неинверсным (инверсным) выходом последующего дифференциального каскада и три набора компараторов, входы двух из которых подключены к выходам блоков аналоговой свертки соответственно, а вход третьего соединен со входами блоков аналоговой свертки, соединенных с входной клеммой аналого-цифрового преобразователя (1) .

Однако известный аналого-цифровой преобразователь имеет низкую надежность и точность преобразования.

Цель изобретения — повышение точности и надежности аналого-цифрового преобразователя.

Поставленная цель достигается тем, что в аналого-цифровой преобразователь, содержащий два набора компараторов, два блока аналоговой свертки, выполненный на дифференциальных каскадах, причем инверсный выход предыдущего дифференциального каскада соединен с неинверсным выходом последующего дифференциального каскада, а неинверсный выход с инверсным выходом последующего дифференциального каскада, при этом входы блоков аналоговой свертки подключены ко входной клемме аналогоцифрового преобразователя, а к выходам блоков аналоговой свертки подключены соответственно наборы компараторов, введены в блоки аналоговой свертки дифференциальный усилитель, два делителя напряжения, пять источников тока, группа транзисторов, проводимость которых противоположна проводимости транзисторов дифференциальных каскадов, при этом дополнительно введены в первый блок развертки четыре компаратора, кодирующих старшие разряды, два источника стабильных токов и вторая группа транзисторов, проводимость коорых идентична первой, при этом базы

20 транзисторов первой группы подключены к эмиттерам транзисторов дифференциальных каскадов, базы транзисторов второй группы соединены с эмиттерами транзисторов второго, третьего, шестого и седьмого диффе815902

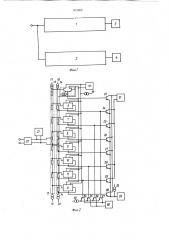

Блок 1 аналоговой свертки содержит дифференциальные каскады 5 — 12, входы которых соответственно подключены к делителям 13 и 14 напряжения, а инверсный (неинверсный) выход предыдущего дифференциального каскада подключен к неинверсному (инверсному) выходу последующего.

Соединенные таким образом выходы дифференциальных каскадов подключены к входу компаратора 15 и источнику 16 стабильного тока. Крайние резисторы делителей 13 и 14 соответственно подключены к источникам 17 — 20 стабильного тока и ко входам дифференциальных каскадов 5 — 12. К средним резисторам делителей 13 и 14 подключены входы компаратора 21 и инверсный и неинверсный выходы дифференциального усилителя 22, первый вход которого. является входом аналого-цифрового преобразователя, а второй соединен с источником опорного напряжения.

Эмиттеры транзисторов дифференциальных каскадов 5 — 12 соответственно подклю40

55 ренциальных каскадов, эмиттеры транзисторов первой группы соединены с первым источником стабильного тока и с входом соответствующего набора компараторов, а коллекторы первого, четвертого, пятого и восьмого транзисторов этой группы соединены с первым входом первого компаратора, коллекторы второго, третьего, шестого и седьмого транзисторов — со вторым входом первого компаратора, а эмиттеры транзисторов второй группы соединены со вторым источником стабильных токов, а коллекторы первого и четвертого транзисторов этой группы соединены с первым входом второго компаратора, коллекторы второго и третьего транзисторов — со вторым входом второго компаратора, выходы дифференциальных каскадов соединены с входами третьего компаратора и третьим источником .стабильного тока, входы дифференциальных каскадов последовательно подключены к делителям напряжения, при этом первый и последний резисторы первого и второго делителя напряжения соединены соответственно с четвертым, пятым, шестым и седьмым источниками стабильных токов и с входами соответственно первого и последнего дифференциальных каскадов, средняя точка делителя напряжения подключена к инверсному и к неинверсному выходам дифференциальных усилителей и ко входу четвертого компаратора.

На фиг. 1 представлена структурная схема аналого-цифрового преобразователя; на 30 фиг. 2 — схема первого блока аналоговой свертки; на фиг. 3 — эпюры, поясняющие работу преобразователя.

Преобразователь содержит первый блок 1 аналоговой свертки, второй блок 2 аналоговой свертки и наборы компараторов 3 и 4, входы которых подключены к выходам блоков 1 и 2 аналоговой свертки. чены к базам транзисторов 23 — 30 противоположной проводимости. Коллекторы транзисторов 23, 26, 27 и 30 объединены и подключены к первому входу компаратора 31, а коллекторы транзисторов 24, 25, 28 и 29— к второму входу этого компаратора. Эмиттеры трачзисторов 29 — 30 подключены к источнику 32 стабильного тока и ко входу 33 набора компараторов. Базы транзисторов

34 — 37, проводимость которых та же, что и транзисторов 23 — 30, подключены соответственно к базам транзисторов 29, 28, 25 и 24. Коллекторы транзисторов 34, 37 подключены к первому входу компаратора

38, а коллекторы транзисторов 35 — 36 ко второму.

Эмиттеры транзисторов 34 — 37 подключены к источнику 39 стабильного тока. Ток источника 17 тока выходит из источника, а ток источника 19 тока входит в источник.

Ток источника 18 тока имеет направление обратное току источника 17, а ток источника 20 тока обратное току источника 19 тока.

Схема второго блока аналоговой свертки аналогична первой, но отсутствуют транзисторы 34 — 37, компараторы 21, 31, 15 и 38, источники 39 и 18 тока. Коллекторы транзисторов дифференциальных каскадов подключены к одному источнику напряжения, остальные транзисторы к другому источнику напряжения. Количество дифференциальных каскадов на один больше.

Разница напряжения с выходов дифференциального усилителя 22 (фиг. 2) преобразуется с помощью делителей 13 и 14 напряжения и стабильных источников 17 — 20 тока и симметрично подается на входы дифференциальных каскадов 5 — 12 и вход компаратора 21. При съеме напряжения с эмиттеров транзисторов, образующих дифференциальный каскад, каждый дифференциальный каскад становится двухполупериодным выпрямителем. Выпрямленное таким образом напряжение поступает на транзисторы

23 — 30, которые пропускают на выход то входное напряжение U<, Uq,...U, которое больше, при этом формируется функция преобразования.

Формирование линейных участков функции преобразования осуществляется эмиттерными повторителями, получающимися из дифференциальных каскадов 5 — 12, когда один из транзисторов открыт, другой закрыт, и эмиттерными повторителями, образующимися из схемы на транзисторах 23-30, когда один из транзисторов открыт. Нелинейные участки функции преобразования образуются при переключении транзисторов дифференциальных каскадов 5 — 12 или транзисторов 23-30.

На фиг. 3 а представлены зависимости напряжений U<, Uz, ..., U, ..., снимаемые с эмиттеров транзисторов каждого дифференциального каскада, от разности напряжений U между выходами дифференциаль815902 ного усилителя 22, а на фиг. 3 б — сформированная функция преобразования блока аналоговой свертки.

Функция преобразования второго блока аналоговой свертки формируется аналогич- ным образом, но при этом смещена по 5 входному напряжению так, чтобы нелиней- ные участки одной перекрывались относительно линейными участками другой, с целью равномерного распределения уровней срабатывания ком параторов набора компараторов 3 и 4 (фиг. 1), которые кодируют младшие разряды. Кодирование старших разрядов производится компараторами 15, 21, 31 и 38 (фиг. 2), подключенными к «внутренним» точкам первого блока аналоговой свертки.

Аналоговые сигналы сформированные суммированием токов коллекторов транзисторов 23-30 и 34-37, дифференциальных каскадов, а также непосредственно на делителях 13 и 14 поступают на входы соответственно компараторов 31, 38, 15 и 21 и 20 представлены на фиг. 3 г, е, з, и. На выходе каждого компаратора появляется единица, когда аналоговый сигнал на его входе превышает нулевой уровень и ноль, если имеет место обратное.

На фиг. 3 в, д, ж графически представ25 лено изменение токов коллекторов при изменении разницы. напряжений на выходе дифференциального усилителя 22, Ii Ii I, 1, ..., Is, 1в — соответственно ток неинверсного и инверсного выхода дифференциального каскада 5, 6, 7,...,12; 1, I, ..., 1 ив токи коллекторов транзисторов 23-30, и 1

I», ..., 1, — токи коллекторов транзисторов 34 — 37.

При кодировании старших разрядов используется по одному компаратору на каж- З5 дый двоичный разряд, из-за чего общее число компараторов преобразователя уменьшается при той же разрядности, что повышает надежность его работы. Кроме того, линейность рабочих участков функции преобразования блоков аналоговой свертки определяется эмиттерными повторителями и они приближаются к идеальным, повышая точность преобразования.

Формула изобретения

Аналого-цифровой преобразователь, содержащий два набора компараторов, два блока аналоговой свертки, выполненный на дифференциальных каскадах, причем 50 инверсный выход предыдущего дифференциального каскада соединен с неинверсным выходом последующего дифференциального каскада, а неинверсный выход с инверсным выходом последующего дифференциального каскада, при этом входы блоков аналоговой свертки подключены ко входной клемме аналого-цифрового преобразователя, а к выходам блоков аналоговой свертки подключены соответственно наборы компараторов, отличающийся тем, что, с целью повышения точности и надежности, введены в блоки аналоговой свертки дифферен. циальный усилитель, два делителя напряжения, пять источников тока, группа транзисторов, проводимость которых противоположна проводимости транзисторов дифференциальных каскадов, при этом дополнительно введены в первый блок развертки четыре компаратора, кодирующих старшие разря- ды, два источника стабильных токов и вторая группа транзисторов, проводимость которых идентична первой, при этом базы транзисторов первой группы подключены к эмиттерам транзисторов дифференциальных каскадов, базы транзисторов второй группы соединены с эмиттерами транзисторов второго, третьего, шестого и седьмого дифференциальных каскадов, эмиттеры транзисторов первой группы соединены с первым источником стабильного тока и с входом соответствующего набора компараторов, а коллекторы первого, четвертого, пятого и восьмого транзисторов этой группы соединены с первым входом первого компаратора, а коллекторы второго, третьего, шестого и седьмого транзисторов — со вторым входом первого компаратора, эмиттеры транзисторов второй группы соединены со вторым источником стабильных токов, коллекторы первого и четвертого транзисторов этой группы соединены с первым входом второго компаратора, коллекторы второго и третьего транзисторов — со вторым входом второго компаратора, выходы дифференциальных каскадов соединены с входами третьего компаратора и третьим источником стабильного тока, входы дифференциальных каскадов последовательно подключены к делителям напряжения, при этом первый и последний резисторы первого и второго делителя напряжения соединены соответственно с четвертым, пятым и шестым и седьмым источниками стабильных токов и с входами соответственно первого и последнего дифференциальных каскадов, средняя точка делителей напряжений подключена к инверсному и к неинверсному выходам дифференциальных усилителей и ко входу четвертого компаратора.

Источники информации, принятые во внимание при экспертизе

1. Агвеl А., Кцга R. FAST ADC. «1ЕЕЕ

Trans.Nucl. Sci>, 1975, № 1, чо1,5-22, р. 450 (прототип) .

815902 фиг.3

Составитель А. Кузнецов

Редактор Н. Рогулич Техред А. Бойкас Корректор М. Коста

Заказ 727/89 Тираж 999 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий! 13035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4