Коммутатор

Иллюстрации

Показать всеРеферат

(111815909

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К .АВТОРСКОМУ СВИДЕТЕЛЬСТВУ.

Союз Советскии

Социалистических республик

i

l (61) Дополнительное к авт. свид-ву— (22) Заявлено 18.05.79 (21) 2768140/18-21 с присоединением заявки №вЂ” (23) Приоритет— (51) М.К .

Н 03 К 17/00

Гесударстееииый комитет

СССР

Опубликовано 23.03.81. Бюллетень №11

Дата опубликования описания 28.03.81 пп делам изебретеиий и открытий (53) УДК 681.32 (088.8) (72) Авторы изобретения

В. В. Апинян, Н. И. Лычагин, В. А. Пушкин, Л. И. Сулин, В.. И. Антюхов и И. А. Маслова (71) Заявитель (54) КОММУТАТОР

Изобретение относится к коммутационной технике.

Известны, коммутаторы, содержащие передатчики, приемники и матрицу коммутации (1) .

Недостатком известного устройства является низкое быстродействие.

Наиболее близким техническим решением к предлагаемому является коммутатор, содержащий М передатчиков и N приемников, а также матрицу из М-N узлов, в каждом из которых расположен элемент И коммутации, при этом первые входы элементов И коммутации каждого столбца матрицы объединены и подключены к информационному выходу соответствующего передатчика, а выходы элементов И коммутации каждой строки матрицы объединены и подключены ко входу соответствующего приемника (2) .

Недостатком известного устройства является низкое быстродействие.

Цель изобретения — повышение быстродействия коммутатора.

Указанная цель достигается за счет того, что в коммутаторе, содержащем М передат чиков и N приемников, а также матрицу

2 из М-N узлов, в каждом из которых расположен элемент И коммутации, при этом первые входы элементов И коммутации каждого столбца матрицы объединены и подключены к информационному выходу соответствующего передатчика, а выходы элементов И коммутации каждой строки матрицы объединены и подключены ко входу .соответствующего приемника, введены входной

М-канальный и выходной N-канальный блоки приоритетного обслуживания, шифратор то М регистров с разрядностью logtN, М дешифраторов, N канальных элементов ИЛИНЕ, управляющий элемент ИЛИ-НЕ и Nразрядный регистр маски, при этом каждый из входов входного блока приоритетного обслуживания соединен с управляющим выход дом соответствующего передатчика, каждый из информационных выходов — со входом считывания соответствующего регистра и управляющим входом соответствующего дешифратора, первый и второй управляющие выходы подключены соответственно к управляющим входам регистра маски и выходного блока приоритетного обслуживания, информационные входы которого соединены с выходами регистра маски, а вы815909 дами регистров 8, выходы каждого из которых подключены к информационным входам соответствующего дешифратора 9, каждый из выходов каждого из которых соединен со вторым входом одного из элементов И 4 коммутации соответствующего столбца матрицы 3 и одним из входов соответствующего канального элемента ИЛИ-НЕ 10, выходы которых подключены к информационным входам регистра 12 маски, а дополнительные входы объединены и подключены к выходу управляющего элемента ИЛИ-НЕ 11, входы которого соединены с информационными выходами входного блока 5 приоритетного обслуживания.

Функционирование коммутатора ществляется следующим образом.

55 ходы подключены ко входам шифратора, выходы которого соединены с информационными входами регистров, выходы каждого из которых подключены к информационным входам соответствующего дешифратора, каждый из выходов каждого из которых соединен со вторым входом одного из элементов И коммутации соответствующего столбца матрицы и одним из входов соответствующего канального элемента ИЛИ-НЕ, выходы которых подключены к информационным вХодам регистра маски, а дополнитель- 10 ные входы объединены и подключены к выходу управляющего элемента ИЛИ-НЕ, входы которого соединены с информационными выходами входного блока приоритетного обслуживания.

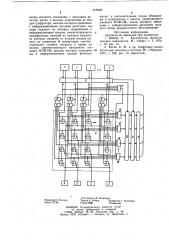

На чертеже представлена функциональная схема коммутатора.

Схема содержит передатчики 1, приемники 2, матрица 3, в каждом узле которой расположен элемент И 4 коммутации, первые входы которых в каждом столбце мат- 20 рицы 3 объединены и подключены к информационному выходу соответствующего передатчика 1, а выходы элементов И 4 коммутации каждой строки матрицы 4 объединены и подключены ко входу соответствующего приемника 2, входной блок 5 приори- 25 тетного обслуживания, выходной блок 6 приоритетного обслуживания, шифратор 7, регистры 8, дешифраторы 9, канальные элементы ИЛИ-НЕ 10, управляющий элемент

ИЛИ-НЕ 11, регистр 12 маски.

Каждый из входов входного блока 5 приоритетного обслуживания соединен с управляющим выходом соответствующего передатчика 1, каждый из информационных выходов — со входом считывания соответствующего регистра 8 и управляющим входом соответствующего дешифратора 9, первый и второй управляющие выходы подключены соответственно к управляющим входам регистра 12 маски и выходного блока 6 приоритетного обслуживания, информационные входы которого соединены с вы- 40 ходами регистра 12 маски, а выходы подключены ко входам шифратора 7, выходы которого соединены с информационными вхо

Активный передатчик 1 выдает сигнал опроса, который обрабатывается входным блоком 5 приоритетного обслуживания. После подтверждения блоком 5 приоритетного обслуживания получение сигнала опроса, активный передатчик 1 через указанный блок устанавливает регистр 12 маски и выдает сигнал на управляющий вход выходного блока 6 приоритетного обслуживания. Вследствие этого с выходов выходного блока 6 приоритетного обслуживания снимается код номера того из запрошенных свободных приемников 2, который имеет более высокий приоритет и выборка которого не запрещена регистром 12 маски. Указанный код через шифратор 7 записывается в соответствующем регистре 8. После получения разрешения от соответствующего выхода входного блока 5 приоритетного обслуживания указанный регистр 8 на одном из выходов одноименного дешифратора 9 вырабатывает единичный логический уровень, который разблокирует соответствующий элемент И 4 коммутации, подсоединяя тем самым активный передатчик 1 с выбранным приемником 2, и через соответствующий элемент

ИЛИ-НЕ 10 обнуливает одноименный разряд регистра 12 маски. В случае замены двух приемников 2 блоком связи и подключения его выхода ко входам передатчиков 1, коммутатор через два элемента И 4 коммутации осуществляет связь между двумя передатчиками 1.

Формула изобретения

Коммутатор, содержещий М передатчиков и N приемников, а также матрицу из

М - Nузлов,,в каждом из которых расположен элемент И коммутации, при этом первые входы элементов И коммутации каждого столбца матрицы объединены и подключены к информационному выходу соответствующего передатчика, а выходы элементов И коммутации каждой строки матрицы объединены и подключены ко входу соответствующего приемника, отличающийся тем, что, с целью повышения быстродействия, введены входной М-канальный и выходной N-канальный блоки приоритетного обслуживания, шифратор, М регистров с разрядностью 1од N, М дешифраторов, N канальных элементов ИЛИ-НЕ, управляющий элемент ИЛИ-НЕ и N-разрядный регистр маски, при этом каждый из входов входного блока приоритетного обслуживания соединен с управляющим выходом соответствующего передатчика, каждый из информационных выходов — со входом считывания соответствующего регистра и управляющим входом соответствующего дешифратора, первый и второй управл цощие выходы подключены соответственно к управляющим входам регистра маски и выходного блока приоритетного обслуживания, информационные входы которого, соединены с выходами регистра маски, а выходы подключены ко входам шифратора, выходы которого соединены с информационными входами регистров, выходы каждого из которых подключены к информационным входам соответствующего дешифратора, каждый из выходов каждого из которых соединен со вторым входом одного из элементов И коммутации соответствующего столбца матрицы и одним из входов соответствующего канального элемента ИЛИ-НЕ, выходы которых подключены к информационным входам регистра

815909

6 маски, а дополнительные входы объединены и подключены -к выходу управляющего элемента ИЛИ-НЕ, входы которого соединены с информационными выходами входного блока приоритетного обслуживан14я.

5 Источники информации, принятые во внимание при экспертизе

1. Байцер Б. Архитектура вычислительных комплексов. М., «Мир», т. 1, 1974, с. 19, рис. 14.

2. Каган Б. М. и др. Цифровые вычис10 лительные машины и системы М., «Энергия»

1973, с. 542, рис. 10 (протогип).

Редактор Н. Рогулич

Заказ 727 89

Составитель В. Чачанидзе

Техред А. Бойкас Корректор Г. Решетник

Тираж 983 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035; Москва, )К вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», r. Ужгород, ул. Проектная, 4