Коммутатор

Иллюстрации

Показать всеРеферат

ОП ИСАНИ Е

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Соеетскии

Социалистическии

Республик!

1

В

Ф (61) Дополнительное к авт. свид-ву— (11) Заявлено 18.06.79 (21) 2780335/18-21 с присоединением заявки №вЂ” (23) Приоритет— (51) М.К .

Н 03 К 17/04

Гооударотаеииый комитет

СССР

IIo делам иаобретеиий и открытий

Опубликовано 23.03.81. Бюллетень № 11

Дата опубликования описания 28.03.81 (53) УДК 621.316..56 (088.8) (72) Авторы изобретения

В. П. Запольских, В. П. Распопов и В. А. Фалелеев

Карагандинский филиал Особого конструкторского бюро

Всесоюзного научно-исследовательского института автоматизации черной металлургии (71) Заявитель (54) КОММУТАТОР

Изобретение относится к импульсной технике и может быть использовано в системах автоматического регулирования технологических параметров и устройствах управления телеметрических систем, например в системах автоматического регулирования -темпе- 5 ратуры смотки на широкополосных станах горячей прокатки.

Известны многоразрядные коммутирующие устройства, содержащие в . каждом разряде D-триггер, элементы И и элемент

ИЛИ- .НЕ (1).

1О

Недостаток устройства — невозможность корректирования записанной информации.

Известен электронный коммутатор, содержащий ключи, кодирующее устройство и регистр сдвига, а в каждом разряде—

15 основной и дополнительный триггеры и элементы И (2) .

Недостаток этого устройства — невысокая точность коммутации, из-за невозможности корректирования записанной инфор- ао мации в сторону уменьшения числа включенных исполнительных механизмов без предварительного сброса, а затем записи новой информации.

Цель изобретения — повышение точности устрой ства.

Поставленная цель достигается тем, что в коммутатор; состоящий из К разрядов каждый из которых содержит основной триггер, первый вход которого соединен с шиной сдвига, а выход — с соответствующей выходной шиной, первый и второй элементы И и дополнительный триггер, выходы которого соединены с первыми входами первого и второго элементов И соответственно, а вход подключен к соответствующей шине управления, в каждый разряд дополнительно введены третий и четвертый элементы И и элементы ИЛИ, причем первый вход первого элемента ИЛИ К-го разряда соединен с выходом основного триггера К-1-го разряда и с первым входом второго элемента ИЛИ

К-2-го разряда, второй вход — с выходом первого элемента И К-1-го разряда, а выход — со вторым входом первого элемента

И и вторым входом второго элемента И К-го разряда, третий вход которого подключен к шине «Сдвиг вправо», а выход — к первому входу третьего элемента ИЛИ, при этом выход последнего соединен со вторым входом основного триггера, а второй вход—

815912 с выходом третьего элемента И К-ro разряда, первый вход которого подключен ко второму выходу дополнительного триггера, второй вход — к шине «Сдвиг влево», а третий — к выходу второго элемента ИЛИ и к первому входу четвертого элемента И, второй его вход соединен с первым выходом дополнительного триггера, а выход — со вторым входом второго элемента ИЛИ-. К1-го разряда, кроме того, первый вход второго элемента ИЛИ-К-го разряда подключен к выходу основного триггера К+1-ro разря- 10 да, а второй вход — к выходу четвертого элемента И К + 1-го разряда.

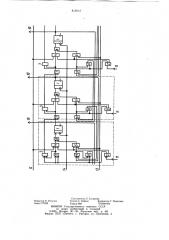

На чертеже представлена функциональная схема устройства, для числа разрядов

К = 3.

Каждый разряд содержит триггеры 1 и 2, элементы И 3 — 6, элементы ИЛИ 7, 8 и 9, выходную шину 10, шину 11 управления; шину 12 «Сдвига вправо», шину 13 «Сдвиг влево», шину 14 сдвига.

Коммутатор работает следующим обра- >О зом.

Если триггеры 2 находятся в состоянии, при котором на их первых и вторых входах присутствует сигнал логической «1» и логического «О» соответственно, на шине 12

«Сдвига вправо» присутствует сигнал логической «1» (разрешение сдвига вправо).

На шине «Сдвиг влево» .присутствует сигнал логического «О» (запрещение

Сдвига влево) и на входах элемента ИЛИ 7 первого разряда присутствует сигнал логи- Зо ческой «1», то при поступлении на шину 14 сдвига, и импульсов,,первые и триггеров 1 устанавливаются в состояние логической «11, поскольку в этом случае сразу дается разрешение установки в единицу триггеру 1 первого разряда, так как сигнал логической «1» с выхода элемента ИЛИ 7 первого разряда поступает-через элемент И 4, элемент ИЛИ 8 первого разряда на триггер 1. После прихода первого импульса на шину 14 сдвига и установления триггера 1 первого разряда в состояние логической «1» этот сигнал передается через элемент ИЛИ 7, элемент И 4 и элемент ИЛИ 8 второго разряда на основной триггер 1 этого разряда, который устанавливается в состояние логической «1»

45 вторым импульсом, поступившим на шину 14 сдвига. Триггеры 1 последующих разрядов последовательно устанавливаются в состоявают в состояние логического «О». Поскольние логической «1» описанным образом.

Если же первые и основных триггеров 1 находятся в состоянии логической «1», вспо- 50 могательные триггеры 2 в прежнем состоянии, коммутатору разрешается сдвиг влево и на входах элемента ИЛИ 9 последнего разряда присутствует сигнал логического «О», то при поступлении на шину 14 сдвига m импульсов т < и, последние m триггеров, из тех, которые в состоянии логической «1», последовательно устанавлику в этом случае разрешение установки в состояние логического «О» с выхода триггера 1 и + 1 разряда передается через элемент ИЛИ 9, элемент И 5 и элемент ИЛИ 8 п разряда на D вход основного триггера 1 п разряда, который после прихода первого импульса на шину 14 сдвига установится с состояние логического «0», тем самым давая разрешение установки в состояние логического «О» триггеру 1 п — 1 разряда.

Это разрешение в свою очередь будет передано соответствующими логическими схемами и — 1 разряда, который установится в состояние логического «О» вторым импульсом, поступившим на шину 14 сдвига. Триггеры 1 предыдущих разрядов и — 2, п — 3 и т; д. последовательно устанавливаются в состояние логического «О» подобным образом.

Вспомогательный триггер 2 К разряда находится в состоянии, при котором на его первом и втором выходах присутствует сигнал логического «О» и логической «1» соответственно, коммутатору разрешен сдвиг вправо, на входах элемента ИЛИ 7 первого разряда присутствует сигнал логической

«1». Тогда при поступлении на шину 14 сдвига п импульсов п >V, триггеры 1,..., К-1 разрядов последовательно устанавливаются в состояние логической «1», затем.устанав" ливаются в состояние логической «1» триггеры 1 К + 1, ..., и + 1 разрядов, триггер же К разряда остается в прежнем состоянии, так как в этом случае разрешение установки в состояние логической «1» последовательно передается с помощью элемента ИЛИ 7, элемента И 4 и элемента ИЛИ 8 соответствующих разрядов на входы основных триггеров 1 этих разрядов. После установки основного триггера 1 К-1-го разряда в состояние логической «1», разрешение установки в состояние логической «-1» передано основному триггеру 1 К+1 разряда,,поскольку вспомогательный триггер 2 К разряда -находится в состоянии, обеспечивающем прохождение сигнала разрешения установки в состояние логической «1» с основного три1 гера 1 К-1-ro разряда через элемент ИЛИ 7

К-разряда, и элемент И 3 К разряда на вход элемента ИЛИ 7 К + 1-го разряда, затем этот сигнал через элемент ИЛИ К +

+ 1-го разряда, элемент И 4 К + 1-го разряда и элемент ИЛИ 8 К+ 1-го разряда подается на вход основного триггера 1 К + 1-го разряда. Одновременно сигнал с другого выхода вспомогательного триг-. гера 2 К разряда, поступающий на элемент И 4 К разряда, блокирует прохождение сигнала разрешения на вход основного триггера 1 К разряда.

Если после этого коммутатору дано разрешение сдвига влево, то при поступлении на шину 14 сдвига m импульсов (m < и;

m >и — к) m основных триггеров 1 разрядов и+1,...,К+1, К вЂ” 1..., m — п+1, последо815912 ватеаьно устанавливаются в состояние логического «О», Сначала последовательно устанавливается в состояние логического «О» основные триггеры 1 разрядов, п + 1,...,К + 1, затем основные триггеры разрядов К вЂ” 1,..., m — и+ 5 так как в этом случае сигнал разрешение установки в состояние логического «О» последовательно передается с помощью элемента ИЛИ 9, элемента И 5, элемента

ИЛИ 8 соответствующих разрядов основным триггером 1 данных разрядов. А разрешение tO установки в состояние логического «О» триггеру 1 К-1-го разряда передается с выхода триггера 1 К + 1-го разряда (после установки триггера 1 К + 1-ro разряда в состояние логического «О») через элемент ИЛИ.9

К разряда, элемент И 6 К разряда, элемент

ИЛИ 9, .элемент И 5 и элемент ИЛИ 8

К-1-ro разряда на вход основного триггера 1 К-1 разряда, поскольку вспомогательный триггер 2 К-1-го разряда в этом случае разрешает прохождение сигнала раз- 20 решения установки в состояние логического «О» с основного триггера 1 К + 1-ro разряда на основной триггер 1 К-1 разряда, одновременно блокируя поступление этого сигнала на вход основного триггера 1 К разряда.

Таким образом, если необходимо вывести какие-либо разряды электронного коммутатора из работы (и соответствующие им исполнительные механизмы), то на управляющие входы соответствующих разрядов по- зв даются сигналы, исключающие данные разряды из работы. Сдвиг же информации, записанной в коммутаторе как влево, так и вправо, осуществляется в обход заблокированных разрядов.

Возможности исключения отдельных разрядов из работы позволяет при использовании коммутатора в системах автоматического регулирования управлять распределением регулирующего воздействия.

Возможность работы коммутатора в реверсивном и нереверсивном режимах позволяет производить непрерывную коррекцию записанной информации как в сторону увеличения, так и в сторону уменьшения числа включенных исполнительных механизмов„ воздействуя непосредственно на старшие 15 разряды, что особенно необходимо в быстродействующих системах автоматического регулирования, работающих по принципу предварительного расчета степени регулирования воздействия, а затем коррекций этого расчета.

Формула изобретения

Коммутатор, состоящий из К разрядов, каждый из которых содержит основной триггер, первый вход которого соединен с шиной сдвига,. а выход — с соответствующей выходной шиной, первый и второй элементы И и дополнительный триггер, выходы которого соединены с первыми входами первого и второго элементов И соответственно, а вход подключен к соответствующей шине управления, отличающийся тем, что,-с целью повышения точности, в каждый разряд коммутатора введены третий и четвертый элементы И и элементы ИЛИ, причем первый вход первого элемента ИЛИ К-го разряда соединен с выходом основного триггера К1-го разряда и с первым входом второго элемента ИЛИ К-2-ro разряда, второй вход— с выходом первого элемента И К-1-го разряда, а выход — со вторым входом первого элемента И и вторым входом второго элемента И К-го разряда, третий вход которого подключен к шине «Сдвиг вправо», а выход — к первому входу третьего элемента ИЛИ, при этом выход последнего соединен со вторым входом основного григгера, а второй вход — с выходом третьего элемента И К-го разряда, первый вход которого подключен ко второму выходу дополнительного триггера, второй вход — к шине «Сдвиг влево», а третий — к выходу второго элемента ИЛИМ к первому входу четвертого элемента И, второй его вход соединен с первым выходом дополнительного триггера, а выход — со вторым входом второго элемента ИЛИ К-1-го разряда, кроме того, первый вход второго элемента

ИЛИ К-го разряда подключен к выходу основного триггера К + 1-го разряда, а второй вход — к выходу четвертого элемента

И К + 1-го разряда.

Источники -информации, принятые во внимание при экспертизе 1. Проектирование радиоэлектронной аппаратуры на интегральных микросхемах.

Под ред. С. Я. Шаца. М., «Советское радио», 1976, с. 260.

2. Авторское свидетельство СССР № 414738, кл. Н 03 К 17/64, 05.02.74.

815912

Составитель Л. Захарова

Редактор Н. Рогулич Тех ред А. Бойкас Корректор Г. Решетник

Заказ 727 89 Тираж 988 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4