Устройство для выделения фазомани-пулированных сигналов

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗЬБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ () 815925

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву— (22) Заявлено 31.05.79 (21) 2775703/18-09 (51) М.К .з

Н 04 В 1/10

Н 04 L27/18 с присоединением заявки №вЂ”

Гасударственный кенитет

СССР (23) Приоритет—

Опубликовано 23.03.81,. Бюллетень № 11

Дата опубликования описания 27.03.81 (53) УДК 621.394..14 (088.8) ао лелем изебретеиий

_#_ етнрмтий

Ю. И. Морозов, В. М. Контарович и В. С. Жолуде (72) Авторы изобретения (71) 3аявктель (54) УСТРОЛСТВО ДЛЯ ВЫДЕЛЕНИЯ

ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ

Изобретение относится к радиотехнике и может использоваться в аппаратуре радиоразведкии.

Известно устройство для выделения фазоманипулированных сигналов, содержащее два канала обработки сигналов, каждый из которых состоит из последовательно соединенных сумматора, порогового блока и амплитудного детектора, причем к входам сумматора каждого канала обработки сигналов подключен вход регенератора через фазоинвертор и когерентный гетеродин, а выходы амплитудных детекторов обоих каналов обработки сигналов через последовательно соедийенные вычитающий блок, интегратор, решающий блок и линию задержки подключены к входам элемента И, а также формирователь выходных сигналов (1).

Однако в известном устройстве отеутствует блочная синхронизация, что приводит к возрастанию приема ложной информации.

Цель изобретения — повышение досто,верности приема информации.

Цель достигается тем, что в устройство для выделения фазоманипулированных сигналов, содержащее два канала обработки сигналов, каждый из которых состоит из

2 последовательно соединенных сумматора, порогового блока и амплитудного детектора, причем к входам сумматора каждого канала обработки сигналов подключен выход регенератора через фазоинвертор и когерентный гетеродин, а выходы амплитудных детекторов обоих каналов обработки сигналов через последовательно соединенные вычитающий блок, интегратор, решающий блок и линию задержки подключены к входам элемента И,,а также формирователь выходных сигналов, 10 введены дешифратор и в каждый канал обработки сигналов последовательно соединенные блок перестройки порога и дополнительный сумматор, при этом дополнительный выход решающего блока подключен к первому входу дешифратора, к второму входу которого и к входам блоков перестройки порога обоих каналов обработки сигналов подключен выход элемента И, а выход дешифратора подключен к входу формирователя выходного сигнала, причем к другому входу дополнительного сумматора одного из каналов обработки сигналов подключен выход амплитудного детектора другого канала обработки сигналов, а выход дополнительного сумматора подключен к управ81

3 ляющему входу порогового блока соответствующего канала.

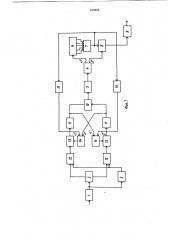

На фиг. 1 приведена структурная электрическая схема предлагаемого устройства; на фиг. 2 — эпюры напряжений, поясняющие его работу.

Устройство для выделения фазоманипулированных сигналов содержит регенератор 1, фазоинвертор 2, интегратор 3, решающий блок 4, когерентный гетеродин 5, линию 6 задержки, элемент И 7, дешифратор 8, формирователь 9 выходных сигналов, вычитающий блок 10 и два канала обработки сигналов, каждый из которых состоит из амплитудного детектора 11, сумматора 12, порогового блока 13, дополнительного сумматора 14 и блока 15 перестройки порога.

Устройство для выделения фазоманипулированных сигналов работает следующим образом.

Информация содержится в короткой команде, состоящей из набора единиц и нулей.

Объем памяти дешифратор а 8 ограничен объемом команды. Каждая единица представляется сигналом известной формы, а нуль — сигналом противоположным ему.

С выхода каналов обработки сигнала, пройдя через вычитающий блок 10 и интегратор 3, сигнал поступает на решающий блок 4.

С выхода решающего блока 4 в дешифратор 8 записываются единицы и нули в зависимости от того, какое (положительное или отрицательное) напряжение существует на выходе интегратора 3 в момент отсчета, и если это напряжение по абсолютному значению превышает пороговое U 1, (фиг. 2 а,б).

С выхода решающего блока 4 импульсы одинаковой полярности поступают на линию 6 задержки (фиг. 2 в). Выходы линии 6 задержки расположены таким образом, что сигнал задерживается на То, 2То, ЗТо, ..., К То, где То — время передачи одного элемента сигнала.

Допустим, что объем дешифратора 8 рассчитан на запись команды, состоящей из М-символов (единиц и нулей). Также допустим, что в дешифратор 8 уже записана (за счет шумовых сигналов или их комбинаций) информация, состоящая из М-символов.

Тогда любой (единица или нуль) поступающий в дешифратор 8 для записи очередной символ стирает первый из М уже записанных символов и записывается сам по

М-ым номерам (фиг. 2в и г). Считывается информация 1011 (фиг. 2 г).

Импульсный сигнал поступает на два блока 15. Блоки 15 преобразуют длительность импульса с выхода элемента И 7 в напряжение. Блок 15 срабатывает, когда б

5925

Зо

4 длительность импульсов совпадения с элемента И 7 больше порогового уровня и импульсы поступают на второй вход дополнительного сумматора 14.

Таким образом, «ложная информация», образующаяся в результате действия помехи и сигналов, в формирователь 9 не проходит.

Дешифратор 8 применяется с целью уменьшения числа ложных импульсных групп.

Под выражением «ложная информация» понимается любая комбинация единиц и нулей, образующая на выходе интегратора 3 и произвольно (с учетом интервала дискретизации и интегрирования То) расположенная на оси времени. Такой «ложной информа- цией» могут быть первые четыре импульса (фиг. 2б) и вообще любые М импульсов, поступающие на дешифратор 8 с момента начала его работы.

Формула изобретения

Устройство для выделения фазоманипулированных сигналов, содержащее два канала обработки сигналов, каждый из которых состоит из последовательно соединенных сумматора, порогового блока и амплитудного детектора, причем к входам сумматора каждого канала обработки сигналов подключен выход регенератора через фазоинвертор и когерентный гетеродин, а выходы амплитудных детекторов обоих каналов обработки сигналов через последовательно соединенные вычитающий блок, интегратор, решающий блок и линию задержки подключены к входам элемента И, а также формирователь выходных сигналов, отличающееся тем, что, с целью повышения достоверности приема информации, введены дешифратор и в каждый канал обработки сигналов последовательно соединенные блок перестройки порога и дополнительный сумматор, при этом дополнительный выход решающего блока подключен к первому входу дешифратора, к второму входу которого и к входам блоков перестройки порога обоих каналов обработки сигналов подключен выход элемента И, а выход дешифратора подключен к входу формирователя - выходного сигнала, причем к другому входу дополнительного сумматора одного из каналов обработки сигналов подключен выход амплитудного детектора другого канала обработки сигналов, а выход дополнительного сумматора подключен к управляющему входу порогового блока соответствующего канала.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

¹ 320939, кл. Н 04 В 1/10, 1972 (прототип).

815925

Составитель А. Сагадиев

Редактор Л. Кеви,Техред А. Бойкас Корректор Г. Назарова

Заказ 746/90 Тираж 698 Подписное

ВНИИПИ Государственного комитета СССР по делам Изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4