Устройство обнаружения периодическогосигнала

Иллюстрации

Показать всеРеферат

ОП ИСАНИ Е

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических республик

Н 04 L 7/02

Гееударстееииый комитет

CCCP ео делам иаооретеиий и открытий

Опубликовано 23.03.81. Бюллетень № 11

Дата опубликования описания 28.03.81 (53) УДК 621.394..662 (088.8) 1

) (12) Авторы изобретения

Л; Е. Варакин и И. В. Трубина

Всесоюзный заочный электротехнический инстит (7l) Заявитель (54) УСТРОИСТВО ОБНАРУЖЕНИЯ ПЕРИОДИЧЕСКОГО

СИГНАЛА

Изобретение относится к технике связи и может использоваться в приемных устройствах различных радиотехнических систем для синхронизации по задержке.

Известно устройство обнаружения периодического сигнала, содержащее преобразователь m-последовательности, схему синхронизации по задержке, генератор опорной

m-последовательности, восстановитель исходной фазы m-последовательности, коррелятор с решающей схемой (1).

Однако известное устройство имеет малде быстродействие.

Наиболее близким к предлагаемому .по технической сущности является устройство обнаружения периодического сигнала, содержащее генератор тактовых импульсов, выход которого соединен с управляющим входом блока формирования синхросигналов, формирователь кодов, блок памяти и анализатор кодов (2).

Однако для обнаружения периодического сигнала известным устройством требуется значительная затрата времени.

Цель изобретения — уменьшение времени обнаружения периодического сигнала.

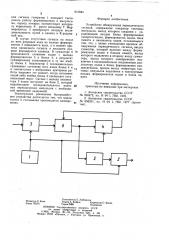

Цель достигается тем, что в известное устройство введен сумматор, который включен между формирователем кодов и блоком памяти, выход которого подключен к второму входу сумматора, выход которого одновременно подключен к последовательно соединенным анализатору кодов и блоку формирования синхросигналов, причем выход генератора тактовых импульсов подключен к тактируемым входам формирователя кодов и блока памяти.

10 На чертеже представлена структурная электрическая схема предлагаемого устройства.

Устройство обнаружения периодического сигнала содержит генератор 1 тактовых импульсов, блок 2 формирования синхросигналов, формирователь 3 кодов, блок 4 памяти, анализатор 5 кодов и сумматор 6.

Устройство работает следующим образом.

Входной сигнал, представляющий собой смесь полезных импульсов с периодом повторения Т и импульсов помехи и имеющий вид случайной последовательности нулей и единиц, поступает на вход формирователя 3 кодов. С момента начала накопле815944

Формула изобретения

Составитель Е. Любимова

Техред А. Бойкас Корректор О. Билак

Тираж 698 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4

Редактор Л. Кеви

Заказ 762/91

3 ния сигнала генератор 1 начинает тактировать работу формирователя 3 импульсами, период которых соответствует интервалу корреляции С, много меньшему Т. Фармирователь 3 преобразует .входную последовательность нулей и единиц в К-разрядный код.

В случае отсутствия сигнала на входе во всех разрядах кода на выходе формирователя 3 появляются нули, а в момент прихода единичного сигнала в младшем разряде формируется единица. В сумматоре 6 производится сложение кодов с выхода формирователя 3 и блока 4, а результат суммирования записывается в ту же ячейку блока 4. Анализатор 5 последовательно сравнивает состояние всех ячеек блока 4 и 15 в соответствии с выбранным критерием работы выделяет тот момент, когда состояние какой-либо ячейки блока 4 превышает установленный порог. Сигнал с выхода анализа- тора 5 кодов поступает на блок 2, который вырабатывает последовательность полез- 20 ных периодических импульсов с необходимой временной задержкой.

Значительное увеличение быстродействия устройства достигается тем, что циклы записи и считывания производятся одновременно.

Устройство обнаружения периодического сигнала, содержащее генератор тактовых импульсов, выход которого соединен с управляющим входом блока формирования синхросигналов, формирователь кодов, блок памяти и анализатор кодов, отличающееся тем, что, с целью уменьшения времени обнаружения периодического сигнала, введен сумматор, который включен между формирователем кодов и блоком памяти, выход которого подключен к второму входу сумматора, выход которого одновременно подключен к последовательно соединенным анализатору кодов и блоку формирования синхросигналов, причем выход генератора тактовых импульсов подключен к тактируемым входам формирователя кодов и блока памяти.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 530472, кл. Н 04 1. 7/02, 1976.

2; Авторское свидетельство СССР № 656231, кл. Н 04 1 7/02, 1977 (прототип).