Приемник тональных сигналов

Иллюстрации

Показать всеРеферат

Союз Советскик

Социапистичесиих

Республик (n>815971

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (223 Заявлеиб 1512.77,(21) 2555207/18-09 с присоединением заявки ¹â€” (51)М. Кл.

Н 04 Q 3/04

Государствеммый коммтет

СССР мо делам мзобретеммй м открытмм (23) Приоритет

Опубликовано 30381, Бюллетень № 11 (5Ç) УДК 621. 395. .632.(088.8) Дата опубликования описания 10. 04 . 81 бюро по проектированию счетных машин и Опытный завод (54 ) ПРИЕМНИК ТОНАЛЬН61Х СИГНАЛОВ

Изобретение относится к электросвязи.

Известен приемник тональных сигналов, содержащий последовательно соединенные согласующий блок и фор-. мирователь импульсов, а также исполнительный блок (1 .

Однако в данном приемнике недо.статочная помехозащищенность.

Цель изобретения - повышение помехозащищенности.

Цель достигается тем, что в приемник тональных сигналов, содержащий последовательно соединенные согласующий блок и формирователь импульсов, 15 а также исполнительный блок, введены реверсивный счетчик, дешифратор нулевого состояния счетчика, дешифраторы минимальной и максимальной длительности сигнала, элемент запрета 20 и последовательно соединенные блок памяти и блок управления, при этом выход формирователя импульсов подключен к первому входу реверсивного счетчика и к первым входам дешифраторов 25. минимальной и максимальной длительности сигнала, выходы реверсивного сигнала подключены к вторым входам дешифраторов минимальной и максимальной длительности сигнала и к входу 30 дешифратора нулевого состояния счетчика, выход которого подключен к входу блока памяти и к входу элемента запрета, на другой вход которого подана эталонная частота, при этом выход элемента запрета подключен к второму входу реверсивного счетчика, выходы дешифраторов минимальной и максимальной длительности сигнала подключены к другим входам блока памяти, а выход блока управления подключен к запрещающему входу формирователя импульсов и к входу исполнительного блока.

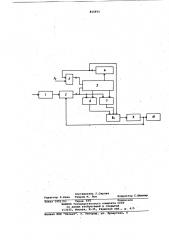

На чертеже изображена структурная электрическая схема предлагаемого приемника.

Приемник тональных сигналов содержит согласующий блок. 1, формирователь 2 импульсов, реверсивный счетчик 3, дешифратор 4 нулевого состояния счетчика, элемент 5 запрета, дешифраторы 6 и 7 минимальной и максимальной длительности сигнала, блбк

8 памяти, блок 9 управления, исполнительный блок 10, Устройство работает следующим Об- разом.

При отсутствии входного сигнала в том случае, если реверсивный счетчик

815971

3 находится в нулевом состоянии, на входе дешифратора 4 нулевого состояния сч учика появляется сигнал логической "1", который. поступает на инверсный вход элемента 5 запрета и запрещает поступление эталонной частоты fe на вычитающий вход реверсивного счетчика 3. В том случае, если состояние реверсивного счетчика 3 отлично от нуля, на выходе дешифратора

4 нулевого состояния счетчика появляется сигнал логического "0", который разрешает поступление эталонной частоты через элемент 5 запрета на вычитающий вход реверсивного счетчика 3 до тех пор, пока реверсивный счетчик 3 не примет состояние, рав- 15 ное нулю.

Входная посылка длительностью частотой заполнения f через согласующий. блок 1 поступает на формирователь 2 импульсов, где частота запол- Щ нения преобразуется. в посыпку импульсов f и, после чего поступает на суммирующий вход реверсивного счетчика

3 и на дополнительные входы дешифраторов б и 7 минимальной и максимальной длительности сигнала для блокировки обратного счета (обратный счет— состояние, при котором на реверсивный счетчик 3 поступают только импульсы на вычитающий вход частоты f ). Поступивший на суммирующий вход импульс изменяет состояние реверсивного счетчика 3 (его состояние становится отличным от нуля), поэтому дешифратор 4 нулевого состояния счетчика снимает блокировку (на элементе 5 запрета) с поступления эталонной частоты на вычитающий вход и при условии, что f больше f3. Реверсивный счетчик 3 йачинает считать текущую разность между Гз и Гз до окончания .4р воздействия входной посылки (f э равнб нулю), после чего из дешифрован-. ного реверсивным счетчиком 3 резуль тата начинается последовательное вычитание эталонной частоты f>. Причем если за время воздействия входной посылки текущая разность между f+ и достигает числа, зафиксированного в дешифраторе б минимальной длительности сигнала, но не достигает числа зафиксированного в дешифраторе 7 максимальной длительности сигнала, состояние реверсивного счетчика 3 запоминается в блоке 8 памяти и блок 9 управления выдает команду о принятии полезного сигнала в исполнительный 55 блок 10. В том случае, если текущая разность частот не достигает числа, зафиксированного в дешифраторе б минимальной длительности сигнала, принимаемый сигнал - помех, команда на исполнительный блок 10 не следует, реверсивный счетчик 3 (после окончания воздействия входной посылки) по вычитающему входу эталонной частотой приводится в нулевое. состояние. Если текущая разность частот достигает числа, зафиксированного дешифратором 7 максимальной длительности сигнала, то принимаемый сигнал тоже помеха, команда на исполнительный блок 10 не поступает, а блок 9 управления выдает команду на запрещающий вход формирователя 2 импульсов на время, пока реверсивный счетчик 3 не очистится под воздействием эталонной частоты.

Формула изобретения

Приемник тональных сигналов, содержащий последовательно соединенные согласующий блок и формирователь импульсов, а" также .исполнительный блок, отличающийся тем, что, с целью повышения помехозащищенности, введены реверсивный счетчик, дешифратор нулевого состояния счетчика, дешифраторы минимальнбй и максимальной длительности сигнала, элемент запрета и последовательно соединенные блок памяти и блок управления, при этом выход формирователя импульсов подключен к первому входу реверсивного сче- . тчика и к первым- входам дешифраторов минимальной и максимальной длительности сигнала, выходы реверсивного счетчика подключены к вторым входам дешифраторов минимальной и максимальной длительности сигнала и к входу дешифратора нулевого состояния счетчика, выход которого подключен к входу блока памяти и к.входу элемента запрета, на другой вход которого подана эталонная частота, при этом выход элемента запрета подключен к второму входу реверсивного счетчика, а выходы дешифраторов минимальной и максимальной.длительности сигнала подключены к другим входам блока памяти, а выход блока управления подключен к запрещающему входу формирователя импульсов и к входу исполнительного блока.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 437242, кл. H 04 .М 3/50, 1973 (прототип).

815971

Составитель Г.Серова

Редактор Л.Кеви Техред М. Поя

Корректор С.Шекмар

Заказ 1051/93 Тираж 69 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушсиая наб., д. 4/5.

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4