Преобразователь сдвига фаз вцифровой код

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

«i> 8176ОЗ

Ф

С (61) Дополнительное и авт. свид-ey—

k (22) Заявлено 17. 12. 74 (21) 2086180/18-21 8 1) М ) л

G 01 R 25/00 с присоединением заявки HP (23) Приоритет—

Государственный комитет

СССР ао дедам изобретений н открытий

Опубликовано 30.0381. Бюллетень HP 12

Дата опубликования описания 300331 (5Ç) УД1 621. 317. .373(088.8) (72) Авторы изобретения

A.Ñ.Áóäàíoâ, A.A.Ãàâðèëîâ и В.П.Максимов (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ СДВИГА ФАЗ В ЦИФРОВОН

КОД

Изобретение относится к измерению электрических величин и предназначено для преобразования фазового сднига синусоидального сигнала в цифровой код.

Известен преобразователь сдвига фаз в цифровой код, содержащий отсчетное устройство, распределитель, электронные ключи, фазовращатели и. фазочувствительный детектор (1).

Недостатком известного устройства янляется недостаточйое быстродействие и точность.

Известное устройство для измере-. ния сдвига фаз, в состав которого входит преобразователь сдвига фаз в цифровой код,состоящее из смесителя, ограничителя, счетчика, фазочунствительного элемента, генератора импульсов, делителей частоты и цифрового отсчетного устройства j2 ).

Недостатками устройства является низкая, разрЕшающая способность и точность за счет BJLHHHHH B Hx FBp» монических составляющих в сигналах делителей частоты, а также последовательный ввод импульсов в делители частоты, что ограничивает его быстродействие.

Цель изобретения — повышение точности и быстродействия.

Цель изобретения достигается тем, что преобразователь сдвига фаэ в цифровой код, содержащий генератор импульсов, первый и второй ныходы которого соединены соответственно со входами делителей частоты, снабжен блоком суммирования, синхронным детектором, первым и вторым формирователями, управляемым генератором импульсов, блоком управления знаком, реверсивным счетчиком, блоком вентилей, первым и вторым преобразовате15 лями код-напряженйе, причем первый выход перного делителя частоты через первый формирователь соединен с первым входом блока вентилей, а второй его выход присоединен к входу

20 первого преобразователя код-напряжение, первый выход второго делителя частоты через второй формирователь соединен с первым входом синхронного детектора, а второй его выход через

2 .второй преобразователь код-напряжение подсоединен к входу сумматора, выход которого соединен со вторым входом синхронного детектора, выход которого соединен через блок управ30 ления знаком и управляемый генератор

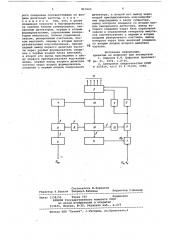

817603 импульсов соответственно с первым и вторым входами реверсивного счетчика, выход которого через блок вентилей соединен со вторым входом второго де лителя частоты, На чертеже приведена блок-схема преобразователя сдвига Фаз в цифро5 ,вой код.

Преобразователь сдвига фаэ в циФровой код содержит блок 1 суммирования, первый преобразователь 2 кода в синусоидальный сигнал, синхронный детектор 3, первый формирователь 4, управляемый генератор 5 импульсов, реверсивный счетчик 6, блок 7 управления знаком, генератор 8 импульсов, первый и второй делители 9 и 10 частоты, второй преобразователь 11 коднапряжение, второй формирователь 12 и блок .13 вентилей.

Работает устройство следующим образом.

Входной синусоидальный сигнал 0 неизвестной Фазы fy подается на один из входов блока 1 суммирования, на второй вход которого подается компенсирующий сигнал Uz с выхода пре- 2g образователя 2 кода в напряжение.

Напряжение с выхода блока 1 суммирования поступает на вход синхронного детектора 3. На второй вход синхронного детектора 3 поступает через

Формирователь 12 напряжение, фаза первой гармоники которого сдвинута

Ж на угол — относительно фазы на2 пряжения 0 . Постоянная составляющая напряжения на выходе синхронного детектора 3, пропорциональная разнос ти фаз между напряжениями 0 и 0 преобразуется в пропорциональную частоту импульсов управляемым генератором 5 и в логические сигналы для управления знаком счета реверсивного счетчика 6 в блок 7 управления знаком. Реверсивный счетчик 6 в зависимости от знака разности фаэ между напряжениями 0 и 02 суммирует либо 45 вычитает импульсы управляемого генератора 5.

Импульсы с генератора 8 импульсов высокой частоты F постоянно суммируются в делителях 9 и 10 частоты, выходные частоты последних триггеров в которых равны частоте f входного напряжения. Код делителя 9 частоты поступает на вход функционального преобразователя 2 кода в синусоидальное напряжение и на вход формирователя 4, который формирует импульсы частоты в момент изменения состояния всех триггеров делителя 9 частоты иэ логической единицы в логический нуль. Код, записанный в реверсивном 60 счетчике 6, через блок 13 вентилей по импульсу с формирователя 4 поступает на установочные входы делителя

10 частоты, устанавливая в последнем число, равное числу М в реверсивном 65 счетчике 6, тем самым сдвигается по фазе постоянно изменяющейся во времени код делителя 10 частоты относительно постоянно изменяющегося кода триггерного делителя 9 на величину, пропорциональную числу И в реверсивном счетчике 6.

Таким образом, синусоидальное напряжение с преобразователя 11, подключенного к выходам делителя 10 частоты, сдвинуто по фазе относительно синусоидального напряжения с выхода преобразователя 2 на величину, пропорциональную числу М, записанному в реверсивном счетчике 6.

Реверсивный счетчик 6 суммирует. либо вычитает импульсы с управляемого генератора 5 до тех пор, пока напряжение Uz с выхода функционального преобразователя 2 не станет в противофазе с входным напряжением 0 при этом постоянная составляющая напряжения на выходе синхронного детектора 3 равна нулю и поступление импульсов с управляемого генератора

5 на вход реверсивного счетчика 6 прекращается. Код в реверсивном счетчике 6 при равенстве нулю постоянной составляющей на выходе синхронного детектора 3 равен сдвигу фаэ между входным напряжением 0 и опорным 0 в .

Любое изменение фазы входного сигнала U вызывает появление постоянной составляющей на выходе синхронного детектора 3, появление импульсов на входе реверсивного счетчика 6, изменение кода в нем, сдвиг во времени постоянно изменяющегося кода делителя 10 частоты относительно кода делителя 9 частоты и, соответственно, изменение фазы компенсирующего напряжения Uz до тех пор, пока код в реверсивном счетчике 6 не будет соответствовать новому значению разности фаэ между входным 0 и опорным 0„„напряжениями.

Последовательное включение сумматора с синхронным детектором позволяет устранить влияние высших гармонических составляющих на точность преобразования фазового сдвига в цифровой код. Повышение быстродействия обеспечивается параллельным вводом числа из реверсивного счетчика по сигналу первого делителя частоты. Применение управляемого генератора обеспечивает линейность и увеличивает диапазон допустимых скоростей изменения фазы входного сигнала.

Формула изобретения

Преобразователь сдвига фаз в цифровой код, содержащий генератор импульсов, первый и второй выходы кото817603

Составитель М.Барашков

Редактор Н.Кешеля ТехредА.Бабинец Корректор С.Шекмар

Заказ 1338/59 Тираж. 732 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП "Патент", г.ужгород, ул.Проектная,4 рого соединены соответственно со вхо-, дами делителей частоты, о т л и— ч а ю щ и и .с я тем, что, с целью повышения точности и быстродействия, он снабжен блоком суммирования, синхронным детектором, первым и вторым формирователями, управляемым генератором импульсов, блоком управления знаком, реверсивным счетчиком, блоком вентилей, первым и вторым преобразователями код-напряжение, причем первый выхоц первого делителя частоты через первый формирователь соединен с первым входом блока вентилей, а второй его выход присоединен к входу первого преобразователя код-напряжение, первый выход второго делителя 15 частоты через второй формирователь соединен с первым входом синхронного детектора, а второй его выход через второй преобразователь код-напряже-, ние подсоединен к входу сумматора, выход которого соединен со вторым входом синхронного детектора, выход которого соединен через блок управления знаком и управляемый генератор импульсов соответственно с первым и вторым входами реверсивного счетчика, выход которого через блок вентилей соединен со вторым входом второго делителя частоты.

Источники информации, принятые во внимание при экспертизе

1. Смирнов П.Т. Цифровые гразометры. Л., 1974, с.8-10.

2. Авторское свидетельство СССР

Р 245914, кл.G 01 и 25/00, 1968.