Пикопрограммное устройство управления

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик оч81771ф

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. сеид-ву— (22) Заявлено 15. 05. 79 (21) 27б5918/18-24 (53)М. Кл. с присоединением заявки ¹â€”

G F 9/46

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет—

Опубликовано 3.0.0381. Бюллетень № 12

{5З) УДК 688. 325 (088.8) Дата опубликования описания 300381 (54) ПИКОПРОГРАИМНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ

Изобретение относится к вычислительной технике и может быть использовайо в устройствах управления ЭВИ.

Известны микропрограммные устройства управления, реализующие принцип пикопрограммирования, который представляет собой уровень микропрограммного управления, допускающий зада- . ние временной последовательности управляющих сигналов. Такое устройство содержит блок памяти, регистр микрокоманд (информационный регистр), дешифраторы, элементы И,ИЛИ j1),.

Наиболее близким по технической сущности к предлагаемому является 15 микропрограммное устройство управ.ления, содержащее и элементов ИЛИ первой группы, генератор тактовых импульсов, блок выделения тактовых сигналов,.адресный элемент И, ре- 20. гистр адреса, дешифратор адреса, информационный регистр 23.

Недостатком известных устройств является низкая экономичность, которая обусловлена большим объемом бло- 2з ка памяти.

Укаэанное устройство реализует двухтактное микропрограммирование, являющееся частным случаем пикопро- .граммирования. При этом любая микро 30

1 команда представляет собой серию уп равляющих сигналов микроопераций, которые выполняются в течение двух тактов.

Цель изобретения — повышение коэффициента использования оборудования.

Указанная цель достигается тем, что пикопрограммное устройстВо управления, содержащее генератор тактовых импульсов, выход которого соединен через блок выделения тактовых сигналов.с первым входом адресного элемента И, выход которого через регистр адреса соединен с информационным входом первого дешифратора адреса, выход которого через первый блок памяти соединен с информационным входом первого информационного регистра, управляющий выход каждого из п операционных полей которого соединен с первым входом соответствующего управляющего дешифратора, группа выходов каждого управляющего дешифратора соединена- с группой входов соответствующего элемента ИЛИ первой группы, выход Каждого элемента ИЛИ первой группы соединен с управляющим входом соответствующего дешифратора кода операции, выхбд каждого дешифратора

817714

Йода операции является выходом устройства, управляющий вход первого дешифратора адреса соединен с выходом блока выделения тактовых сигналов, содержит адресный элемент

ИЛИ, вторую группу из и .элементов

ИЛИ, и управляющих элементов И, триггер управления, второй дешифратор адреса, второй блок памяти, второй информационный регистр, причем выход каждого из п операционных полей второго информационного регистра соединен с первым входом соответствующего управляющего элемента И, второй вход каждого управляющего элемента И соединен с нулевым выходом триг,гера управления, выход каждого уйра- 15 вляющего элемента И соединен с первым входом соответствующего элемента ИЛИ второй группы, второй вход каждого элемента ИЛИ второй группы соединен с информационным выходом 20 соответствующего операционного поля первого информационного регистра,выход каждого элемента ИЛИ второй группы соединен с информационным входом соответствующего дешифратора кода операции, выходы адресных по-. лей первого и второго информационных регистров соединены соответственно с первым и вторым входами адресного элемента ИЛИ, выход которого соединен со вторъм входом адресного элемента И,. информационный и управляющий входы второго дешифратора адреса соединены соответственно с выходами регистра адреса и,блока выделения .тактовых сигналов, единичный и нулевой входы триггера управления соединены соответственно с выходами . первого и второго дешифраторов адреса, единичный выход триггера управления соединен с третьими входами 40 каждого управляющего дешифратора, нулевой выход триггера управления соединен со входами всех элементов ИЛИ первой группы, выход блока выделения тактовых сигналов соединен е третьи- 45 ми входами всех управляющих элементов И, Сущность изобретения состоит в повыаении экономичности устройства за счет задания однотактных и многотак 50 тных. (пико) микрокоманд и разных блоках памяти. При этом удается достичь оптимальной,упаковки информации.

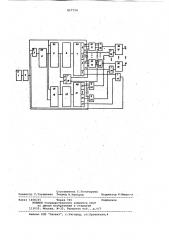

На Чертеже приведена функциональ-. ная Схема пнкопрограммйого устройства .управления. 55

Пикопрограммное устройство управления содержит генератор 1 тактовых импульсов, блом 2 выделения тактовых сигналов, адресный элемент И 3, регистр 4 адреса, первый дешифратор 5 40 адреса, первый блок б памяти, первый информационный регистр 7, содержащий и полей 8., адресное поле 9; каждое из полей 8 имеет управляющий выход

10 и информационный выход 11, УпРав- б5

4 ляющие дешифраторы 12, первая группа элементов ИЛИ 13, вторая группа элементов ИЛИ 14, дешифраторы 15 кодов операцик, выходы устройства 1б, адресный элемент ИЛИ 17, второй дешифратор 18 адреса, управляющий триггер

19, второй блок 20 памяти, второй информационный регистр 21 содержащий и информационных полей 22 н адресное поле 23 и управляющие элементы И 24.

В первом блоке б памяти записаны пикокоманды, которые могут считываться в течение S микротактов, вырабатываемых блоков 2 в каждом рабочем такте устройства.

Во втором блоке 20 памяти записаны однотактные микрокоманды, которые считываются в одном микротакте.

Пикопрограммное устройство управления работает следующим образом.

Каждый рабочий такт устройства состоит из S микротактов (при реализации S-тактного пикопрограммирования) .

В исходном состоянии все элементы памяти находятся в нулевом состоянии, в регистр 4 записан адрес очередной микрокоманды микропрограммы.

По первому импульсу микротакта, который поступает с выхода блока 2 на управляющие входы дешифраторов 5 и 18, возбуждается один из выходов дешифратора 5 или 18.

Если реализуемая микрокоманде является многотактной (пикокомандой), то возбуждается выход дешифратора 5.

При этом триггер 19 устанавливается в единичное состояние, а в регистр 7 блока б памяти считывается код микрокоманды.

Код такта, в котором должна считываться операционная информация с выхода 11, поступает с выхода 10 на дешифратор 12. Операционные сигна- лы поступают с выхода 11 через элемент ИЛИ 14 на вход соотьетствующего дешифратора 15 °

С приходом на второй вход дешиф-ратора 12 сигнала микроконтакта, код которого задан c .âûõoäà 10, срабатывает дешифратор 12, который через элемент ИЛИ 13 открывает дешифратор 15. На выходе дешифратора 15 появляется сигнал соответствующей микрооперацин. Аналогично в соответствующем микроконтакте считывание информации с каждого из выходов 11 полей 8 регистра 7 °

Кроме того, адрес очередной микрокоманды с выхода поля 9 через элемент ИЛИ 17 и элемент И 3 в первом микротакте записывается в регистр 4.

Если очередная микрокоманда является однотактной, то возбуждается . один из выходов дешифратора 18. При этом триггер 19 устанавливается в нулевое состояние. Иимрокоманда считывается нз блока 20 памяти в регистр

817714

21.С поля 23 считывается через элементй ИЛИ 17 и элемент ИЗ в регистр

4 адрес очередной микрокаманды.

С поля 22 сигналы поступают через элементы И 24, открываемые сигналами соответствующего микротакта с выхода блока 2,через элементы ИЛИ 14 . на дешифратор 15,.который сраба тывает по разрешающим сигналам, которые поступают с нулевого выхода триггера 19 через элементы ИЛИ 13.

После этого с приходом очередного сигнала первого микротакта устройство функционирует аналогично описанному °

Предлагаемое устройство более экономично по сравнению с известным за счет уменьшения объема блоков па-, мяти. Причем повышение экономичности данного устройства существенно повышается при увеличении тактности."

Формула изобретения

Пикопрограммное устройство управления, содержащее генератор тактовых 25 импульсов, выход которого соединен через блок выделения тактовых сигналов с первым входом адресноГо эле мента К, выход которого через регистр адреса соединен с информационным вхо- gg дом.первого дешифратора адреса, выход которого через первый блок памяти соединен с информационным входам первого информационного регистра, управляющий.выход каждого из и операци.онных полей которого соединен с первым входом соответствующего управляющего дешифратора, группа выходов кащдого управляющего дешифратора соединена с.группой входов соответству- кицего элемента ИЛИ первой группы, 40 выход каждого элемента ИЛИ первой группы соединен с управляющим входом соответствующего дешифратора кода операции, выход каждого дешифратора кода операции является выходом уст.-- 45 ройства, управляющий. вход первого .дешифратора адреса соединен с выходом блока выделенйя тактовых сигналов, отличающееся тея, что, с целью повышения коэффициента использования оборудования, оно содер" жит адресный элемент ИЛИ, вторую группу из и элементов ИЛИ, и управля.ющих элементов И, триггер управления, второй дешифратор адреса, второй блок памяти, второй информационный регистр, причем выход каждого из и операционных полей второго информационного регистра соединен с первым входом соответствующего управляющего элемента .И, второй вход каждого управляющего элемента И соединен с нулевым выходом триггера управления, выход каждого управляющего элемента

И соединен с первым входом соответствующего элемента ИЛИ второй группы, второй вход каждого элемента ИЛИ второй группы соединен с информационным выходом соответствующего операционного поля первого информационного регистра, выход каждого элемента ИЛИ второй группы соединен с информацион .ным входом соответствующего дешифратора кода операции, выходы адресных полей первого и второго ийформационных регистров соединены соответственно с первым и вторым входами адресного элемента ИЛИ,выход которого соединен со вторым входом адресного эле" мента И, информационный и управляющий входы второго дешифратора адреса соединены соответственно с выходами регистра адреса и блока выделения тактовых сигналов, единичный и нулевойз входы триггера управления соединены соответственно с выходами первого и второго дешифраторов адреса, единичный выход триггера управления соединен с третьими входами каждого . управлякицего дешифратора, нулевой выход триггера управления соединен со входами всех элементов ИЛИ первой группы, выход блока выделения тактовых сигналов соединен с третьими входами всех управляющих элементов И.

Источники информации, принятые во. внимание при экспертизе

1. Авторское свидетельство СССР

9 331387, кл. 6 06 F ..9/16, 1972.

2 ° Авторское свидетельство СССР

Р 602947, кл. G 06 F 9/16, 1978 (прототип).

817714

Филиал ППП "Патент", r.óæãîðoä,.óë.Ïðoåêòèàÿ,4

Составитель Г.Пономарева

Редактор С.Тараненко Техред H.Ìàéîðîø

Заказ 14б8/65 Тираж 745

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Корректор Н.Швыдкъя

Подписное