Устройство для решения интеграль-ных уравнений

Иллюстрации

Показать всеРеферат

ОПРОС изОБpETEnHЙ 817726

Союз Советских

Социалистических

Республик

К АВТОИ:КОМУ СВИДЕТЕЛЬСТВУ (63) Дополнительное к авт. свид-ву— (22) Заявлено 11, 04. 79 (23) 2771988/18-24 (51)М. Кл.э

G 06 F 15/32 с присоединением заявки Ио

Гоеударстаеииый комитет

СЕСЕ ио делам изооретеиий и. открытий (23) Приоритет—

Опубликовано 3003,81. Бюллетень Но 12 (53) УДК 681. 323 (088.8) Дата опубликования описания 300331 (72» Авторы изобретения

Г

В.П.Боюн, Л.Г.Козлов и В.Г.Тракай .! .-,, 1

Ордена Ленина институт кибернетики АН Украинской. CCP.. (71} Заявитель (54) УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ИНТЕГРАЛЬНЫХ

УРАВНЕНИЙ

2 t

4.Д,+ (Х ) =УХ(Х.)+йУ, (Х.) ь,=,2, и„,„(;)=% %.(К„(Х„.)), где q - основание системы счисления; р - разрядность представления чисел в устройстве (2).

Недостатбк известного устройстванизкое быстродействие, так как число итераций, которое наобходимо выполнить, чтобы получить .решение интегрального уравнения, пропорционально

qp, и при р>10 Оно достигает большой величины, что ведет к резкому увеличению времени счета.

Цель изобретения — повышение быстродействия устройства.

Пбставленная цель достигается тем, что.в устройство, содержащее группу гейераторов функций, входы которых подключены к первому выходу блока управления, первую группу коммутатоИзобретение относится к вычислительной технике и предназначено для решения интегральных уравнений Фредгольма второго рода.

Известно устройство для решения интегральных уравнений Фредгольма, .содержащее блоки переменных коэффициентов, интеграторы, емкостное запоминающее устройство, переключатель, 1О шаговый искатель. Устройство реали-. зует метод простой итерации решения интегральных уравнений при дискретной форме аппроксимации ядра P1) .

Однако в данном устройстве низкая точность, поскольку использование аналоговых блоков не позволяет получить необходимую точность решения интегральных уравнений.

Наиболее близким к предлагаемому является устройство для решения интегральных уравнений, содержащее группу генераторов функции, группу первых коммутаторов, группу сумматоров, группу узлов выделения знака, группу реверсивных счетчиков, второй коммутатор., первый счетчик и блок управления. В устройстве реализуется модифицированный метод последовательных приближений решения интегральных уравнений, s котором неизвестная фун- ЗО кция у(х) íà k+1 итерации ищется в виде

Приращени лу„ х,) функции вычисляется по формуле

817726

65 ров, первые входы которых соединены с выходами соответствующих генераторов функций группы, а вторые входы подключены к выходу первого счетчика, группу сумматоров, первые входы которых соединены с выходами соответствующих коммутаторов первой группы, а вторые входы подключены к выходу коммутатора, группу узлов выделения знака, первые входы которых соединены с выходами соответствующих сумматоров группы, а вторые входы подключены ко второму выходу блока управления, группу реверсивных счетчиков, первые входы которых соединены с выходами соответствующих узлов выделения знака группы, группа входов коммутатора подключена к выходам узлов выделения знака группы, а вход коммутатора соединен .с третьим выходом блока управления, введены вторая группа коммутаторов и второй счетчик, причем первый вход второго счетчика соединен с четвертым выходом блока управления, а выход второго счетчика подключен ко входу блока управления, пятый выход которого соединен со вторымн входами реверсивных счетчиков группы, со вторым входом второго счетчика, с входом первого счетчика, и с первыми входами коммутаторов второй группы, вторые входы которых подключены к выходам соответствующих узлов выделения знака группы, а выходы коммутаторов второй группы соединены с третьими входами соответствующих сумматоров группы.

Все элементы устройства, кроме коммутатора, блока управления, первого и второго счетчиков, объединены в и идентичных строк (n- число точек, в которых определяется искомая функция у (х).

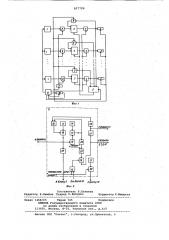

На фиг.1 изображена блок-схема предлагаемого устройства; на фиг.2 блок-схема блока управления.

Устройствс содержит группу генераторов 1 функций, первую группу коммутаторов 2, группу сумматоров 3, группу узлов 4 выделения знака, груп пу реверсивиых счетчиков 5, коммута Iop 6, первый счетчик 7, блок 8 управления, вторую группу коммутаторов

9 и второй счетчик 10. Блок 8 управления (фиг.2) состоит иэ генератора

11 импульсов, триггеров 12 и 13, регистров 14 и. 15 порядка и разрядности, счетчика 16,схемы сравнения .17, элементов И 18,19 и 20, элементов

21-24 задержки и элемента ИЛИ 25.

В устройстве также реализуется .модифицированный .метод последователь.ных приближений, однако приращение функции вычисляется по следующей формуле где р разрядность представления чисел в устройстве.

Приращение искомой функции изменяется от величины старшего разряда на первой итерации до величины младшего разряда q на последней.

Количество итераций ограничено величиной разрядности p, которая может задаваться в широких пределах в зависимости от требуемой точности решеfQ ния

Предлагаемое устройство работает следующим образом.

Перед началом работы начальное

15 приближение функции у (x ) =" 0

О 1 заносится в реверсивные счетчики 5, а соответствующее ему значение невязок Е (х„.} = f(х ) - в сумматоры

3. В первый счетчик 7 заносится ве"

20 личина m, которая определяется из соотношения А h = q",,а во второй счетчик 10 — значение разрядности р в дополнительном коде. При выполнении очередной k-ой итерации сигнал

25 о начале итерации поступает с блока

8 управления на вторые входы реверсивных счетчмков 5, где происходит сдвиг содержащейся в них информации на один разряд в сторону старшего

Зо разряда, на вход первого счетчика 7, при этом добавляется единица к его содержимому и на первые входы коммутаторов. 9, настраивая их для пере- дачи знака соответствующей невязки в k-ый разряд сумматоров 3. По ко-. манде с .блока 8 узлы 4 выделяют знаки невязок E„gx ),которые поступают на первые входы соответствующих реверсивных счетчиков 5, что равносильно подаче в них приращений а у {х;).

40 В счетчиках 5 приращения функции суммируются со значениями функции, по- . лученными на предыдущей итерации.

Знаки невязок поступают также на первые входы коммутатора 6 и через соответствующие коммутаторы 9 в k-е разряды соответствующих сумматоров, что равносильно подаче туда приращений у (х; ) . По .сигналу с блока 8 генераторы 1 функций выдают параллельно по разрядам значения ядер k(x„s), которые через первые коммутаторы 2, где осуществляется сдвиг из на m+p разрядов в сторону младшего разряда, поступают на первые входы соответствующих сумматоров 3. Одновременно с выхода коммутатора 6 на вторые входы сумматоров 3 поступают последовательно знаки невязок Е„ „(х„). В сумматорах 3 происходит вйчисление приращений невязок и суммирование их со значениями невязок Е х „), полученными на предыдущей итерации, т.е.

817726Формула изобретения

Устройство для решения интегральных уравнений, содержащее группу генераторов функций, входы которых под- ключены к первому выходу блока управления, первую группу коммутаторов, первые входы которых соединены с вы-. ходами соответствующих генераторов функций группы, а вторые входы подключены к выходу первого счетчика, 15 группу сумматоров, первые входы которых соединены с выходами соответствующих коммутаторов первой группы, а вторые входы подключены к выходу коммутатора, группу узлов выделения

2О знака, первые входы которых соединены с выходами соответствующих сумматоров, группы,а вторые входы подключены ко второму выходу блока управления, группу реверсивных счетчиков,первые входы которых соединены с выходами соответствующих узлов выделения знака группы, группа входов коммутатора подключена к выходам узлов выделения знака группы, а вход коммутатора соединен с третьим выходом блока упЗО равления, о т л и ч а ю щ е е с я тем, что, с целью повышения быстро- действия, в него введены вторая группа коммутаторов и второй счетчик, причем первый вход второго

35 счетчика соединен с четвертым выходом блока управления, а выход второго счетчика подключен ко входу блока управления, пятый выход которого соединен со вторыми входами реверсивных

4О счетчиков группы, со вторым входом второго счетчика,с входом первого счетчи, ка и с первыми входами коммутаторов второй группы, вторые входы которых подключены к выходам соответствующих узлов выделения знака группы, а выходы коммутаторов второй группы соединены с третьими входами соотI ветствующих сумматоров группы.

Источники информации, принятые во внимание при экспертизе

1. Верлань A.Ô. Иетоды решения интегральных уравнений на аналоговых вычи лительных машинах. K., "Наукова думка", 1972, с.161,163, рис.111, .112;

55 2. Авторское свиде, льство СССР по заявке Р 2599160/18-24, кл.6 06 Х 1/02, 1978 (прототип).

После окончания k-ой итерации в реверсивных счетчиках 5 содержатся значения функции y (x ), а на выходах сумматоров 3 — значения соответствующих невязок Е,(x ). ПосЛедующие итерации выполняются аналоГично.После выполнения р-ой, последней итерации, сигнал переполнения второго счетчика 10 поступает в блок 8 управления, который выдает команду на окончание работы.

Блок 8 управления работает следующим образом.

Сигнал "Начальная устайовка", поступающий на элемент И 20, осуществ-ляет передачу дополнительного кода величины разрядности р с регистра 15 на первый вход второго счетчика 10 и устанавливает триггер 13 в состояние, открывающее элемент И 19, подготавливая схему к работе.

Сигнал "Запуск" (начало. первой итерации) через элементы ИЛИ 25, И 19 поступает на вторые входы реверсивных счетчиков 5, вход первого счетчика 7, первые входы коммутаторов 9 и второй вход счетчика 10. Через элемент 21 задержки задержанный сигнал, поступает на вторые входы узлов 4 выделения знака и через элемент 22 задержки на триггер 12, который открывает элемент И 18. Сигналы от генератора 11 импульсов поступают .на входы генераторов 1 функций, счетчик

16 .и через. элемент 23 задержки на второй вход коммутатора 6 до тех пор, пока схема 17 сравнения, которая сравнивает величину порядка и, содер-: жащуюся в регистре 14, с количеством поступивших на счетчик 16 импульсов, не выдает сигнал на триггер 12, который закрывает элемент И 18, тем самым заканчивая итерацию. Сигнал со схемы 17 сравнения через элемент задержки 24 поступает на элемент ИЛИ 25, начиная следующую итерацию, и т.д. После выполнения р-ой, последней, итерации сигнал переполнения второго счетчика 10 поступает на триг гер 13, который .запирает элемент И 19 останавливая. работу блока управления и всего устройства.

Иногообраэие практических задач, описываемых интегральньеаи уравнениями, определяет актуальность предлагаемого устройства. Оно может работать как самостоятельное вычислительное устройство, так и в комплексе с универсальной цифровой вычислительной машиной. Устройство может найти широкое применение в научных исследованиях, в злектро-и радиотехнической промышленности, строительной механике и оборонной промышленности страны.

817726 .

Фиг, f

Составитель Н.Палеева

Редактор К.Лембак Техред Н.вабУРКа Корректор Н.Швыдкая

В »

Заказ 1468/65 Тираж 745 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035 Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП "Патент", r.Óæãoðîä, ул.Проектная, 4