Устройство для деления частоты пов-торения импульсов

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

<1ц 1

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 23.05.79 (21) 2769212/18-21 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл.

Н 02 К 23/00

Гасударственный комитет

СССР (53) УДК 621.374 (088.8) Опубликовано 30.03.81. Бюллетень № 12

Дата опубликования описания 31.03.81 па делам изобретений и открытий (72) Авторы изобретения

Д. В. Молчанов, А. М. Райнес и П. А. Ефимов ба,.; . (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ЧАСТОТЫ

ПОВТОРЕНИЯ ИМПУЛЬСОВ

Изобретение относится к импульсной технике и может быть использовано в цифровых си нтеза тор ах ч астоты.

Известен делитель частоты, содержащий соединенные последовательно основной и дополнительные делители частоты с переменным коэффициентом деления, выходы которых подключены ко входам суммирующего блока, разрядные коммутаторы, причем выходы суммирующего блока через разрядные коммутаторы подключены к входам основного делителя частоты (1). то

Недостатком известного делителя является неравномерность распределения импульсов во временном интервале, что приводит к возникновению паразитных спектральных составляющих в сигнале и это в свою очередь ограничивает применение по- 15 добных делителей в синтезаторах частот.

Наиболее близким по технической сущности к предлагаемому является устройство для деления частоты повторения импульсов на коэффициенты деления, представленные неправильной двоичной дробью с точностью до заданного двоичного знака после запятой, содержащее делитель частоты, схему запрета и цифровой интегратор, состоящий из

2 регистра подынтегральной функции и сумматора, параллельные входы ввода кода которого соединены с параллельными выходами выдачи кода регистра подынтегральной функции, причем выход делителя частоты соединен со входом приращения независимой переменной цифрового интегратора, выход которого соединен со входом запрещения схемы запрета, управляемый вход которой соединен со входом устройства, а выход — с входом делителя частоты (2).

Недостатком известного устройства является неравномерность распределения выходных импульсов во временном интервале.

Причем неравномерность расстановки выходных импульсов составляет период входной частоты. А уровень паразитных спектральных составляющих грубо определяется отношением между периодами входной и выходной частоты.

Цель изобретения — повышение равномерности следования выходных импульсов при той же разрядности делителя частоты и цифрового интегратора.

Эта цель достигается тем, что в устройство для деления частоты повторения импульсов, содержащее цифровой интегратор, 817891

4. состоящий из регистра подынте грал ьной функции и сумматора, информационные входы которого соединены с информационными выходами регистра подынтегральной функции,и делитель частоты, выход которого подключен ко входу приращения независи-. мой переменной цифрового интегратора, введены два соединенных последовательно и включенных между входом устройства и входом делителя частоты блока сдвига и два триггера, выход каждого из которых соединен с разрешаюшим входом одного из блоков сдвига, причем счетный вход первого триггера соединен с выходом делителя частоты и выходной шиной устройства, вход установки в нуль — с выходом старшего разряда регистра подынтегральной функции, счетный вход второго триггера подключен к выходу сумматора цифрового интегратора.

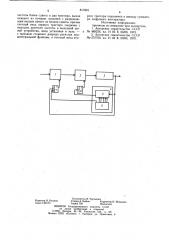

На чертеже приведена структурная электрическая схема предлагаемого устройства для деления частоты повторения импульсов.

Устройство содержит соединенные последовательно два блока 1 и 2 сдвига, делитель 3 частоты, цифровой интегратор 4, состоящий из сумматора 5 и регистра 6 подынтегральной функции. Причем выходная шина подключена к выходу делителя 3 частоты и ко входу сумматора 5 цифрового интегратора 4, к которой подключен также счетный вход первого триггера 7, вход установки в нуль которого подключен к старшему разряду регистра 6 подынтегральной функции. Причем выходная шина подключена к выходу делителя 3 частоты и ко входу сумматора 5 цифрового интегратора 4, к которой подключен также счетный вход пер1 вого триггера 7, вход установки в нуль которого подключен к старшему разряду регистра 6 подынтегральной функции цифрового интегратора 4. Счетный вход второго триггера 8 соединен с выходом сумматора 5 цифрового интегратора 4. Выходы каждого из триггеров 7 и 8 подсоединены к разрешающим входам одного из блоков 1 и 2 сдвига.

Устройство работает следующим образом, В регистр 6 подынтегральной функции цифрового интегратора 4 вводится код, соответствующий дробной части коэффициента деления, а коэффициент деления делителя 3 частоты устанавливают равным целой части коэффициента деления. Работа устройства разбивается на два режима: первый, когда дробная часть коэффициента деления меньше 6,5, и второй — больше или равна 0,5.

При работе в первом режиме блок 1 сдвига работает в качестве повторителя входной последовательности. Управление этим блоком осуществляется через триггер 7 от старшего разряда регистра 6 подынтегральной функции. Если дробная часть коэффициента деления меньше 0,5, в старшем разряде регистра подынтегральной функции записан логический «О», который, поступая на вход обнуления триггера 7, запрещает

его работу в счетном режиме.

Импульсная последовательность, подлежащая делению, подается через блок 1 сдвига и блок 2 сдвига, который в исходном

5 состоянии работает так же, как повторитель.

Каждый импульс, поступающий с выхода делителя 3 частоты на вход приращения независимой переменной цифрового интегратора 4, управляет суммированием содержимого регистра 6 подынтегральной функ О ции с остатком от предыдущего суммирования, находящегося в сумматоре 5.

Импульс приращения интеграла, поступая на триггер 8, изменяет его состояние, что в свою очередь вызывает сдвиг входной последовательности на 180 .

Тем самым достигается деление на число N -+- -. Таким образом, деление происходит наЪ и N + —, т. е. выходные импуль1 сы расставлены равномерно.

В втором режиме (когда дробная часть коэффициента деления больше 0,5) в старшем разряде регистра 6 — логическая «1», которая разрешает переключение триггера 7.

Сдвиг в блоке 1 происходит по каждому выходному импульсу делителя 3. Блок 2 5 сдвига работает как и в первом режиме.

Таким образом, в этом режиме деление происходит на N + — и N + 1, т. е. неравно1 мерность следования выходных импульсов составляет 0,5 периода входной частоты, и, следовательно, уровень модуляции вы30 ходного сигнала уменьшается вдвое.

Технический эффект от использования предлагаемого устройства заключается в повышении равномерности следования выходных импульсов, что, в свою очередь, приводит к уменьшению вдвое уровня побочных спектральных составляющих выходного сигнала.

При использовании такого делителя в качестве формирователя гетеродинной частоты приемника увеличивается его помехоустойчивость.

Формула изобретения

Устройство для деления частоты повторения импульсов, содержащее цифровой интегратор, состоящий из регистра подынтегральной функции и сумматора, информационные входы которого соединены с информационными выходами. регистра подынтегральной функции, и делитель частоты, выход которого подключен ко входу приращения независимой переменной цифрового интегратора, отличающееся тем, что, с целью повышения равномерности следования выходных импульсов, в него введены два соединенных последовательно и включенных между входом устройства и входом делителя

817891

Составитель В. Чернышев

Техред А. Бойкас Корректор Н. Швыдкая

Тираж 730 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4

Редактор Н. Кешеля

Заказ 146! /74 частоты блока сдвига и два триггера, выход каждого из которых соединен с разрешаю-! цим входом одного из блоков сдвига, причем счетный вход первого триггера соединен с выходом делителя частоты и выходной шиной устройства, вход установки в нуль — 5 с выходом старшего разряда регистра подынтегральной функции, а счетный вход второго триггера подключен к выходу сумматора цифрового интегратора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 489226, кл. Н 03 К 23/00, 1973.

2. Авторское свидетельство СССР № 372700, кл. Н 03 К 23/00, 1970.