Устройство для управления инвертором

Иллюстрации

Показать всеРеферат

Социалист.ических

ИЗО6РЕТЕН ИЯ ())) 817981

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 29.05.79 (21) 2772516/24-07 (51) М. Кл. с присоединением заявки №вЂ”

Н 02 P 13/18

Гасударственный комитет

СССР (23) Приоритет— до делам изобретений и открытий (53) УДК 621.316..727 (088.8) Опубликовано 30.03.81. Бюллетень № 12

Дата опубликования описания 05.04.81 институт (54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ИНВЕРТОРОМ

Изобретение относится к электротехнике и может быть использовано в электроприводах с асинхронными двигателями.

Известна цифровая система управления преобразователем, содержащая нуль-орган, счетчики импульсов, умножитель частоты и элемент И (1).

Недостатки указанной схемы — дискретность частоты выходного напряжения, невозможность получения широтно-импульсной модуляции выходного напряжения, например по синусоидальному закону, сложность технической реализации.

Наиболее близким к предлагаемому является устройство для управления преобразователем постоянного напряжения в синусоидальное, содержащее задающий генератор, двоичный счетчик, линейный дешифратор, логические элементы И вЂ” НЕ, ИЛИ вЂ” HE, трансформаторные усилители, усилители мощности, тактовый генератор и ждущие мультивибраторы (2).

Недостатки известного устройства состоят в сложности настройки ждущих мультивибраторов на заданную задержку импульсов, невозможности использования схемы в многофаз ном инверторе, где требуется строго определенный сдвиг фаз, а также невозможности изменения формы тока нагрузки при перестройке частоты.

Цель изобретения — увеличение точности регулирования при многофазном исполнении.

Указанная цель достигается тем, что устройство снабжено включенным на выходе двоичного счетчика дополнительным дешифратором с первым коммутатором на выходе, блоком формирования кодов, со вторым коммутатором на выходе, подключенным к выходам коммутаторов элементом совпадения, включенными в каждом канале и на выходе каждого элемента И вЂ” НЕ триггерами со счетным входом, подключенным к выходу двоичного счетчика в каждой фазе регистром углов управления, который подключен первым выходом ко входу соответствующего элемента И вЂ” НЕ, вторые выходы регистров углов управления подключены ко входам первого коммутатора, причем выход линейного дешифратора подключен ко входу второго коммутатора, выход элемента совпадения и

817981

15

Формула изобретения выход дополнительного дешифратора подключены ко входу каждого элемента И вЂ” НЕ.

Кроме того, с целью исключения асимметрии выходного сигнала, в него введены запоминающие триггеры, каждый из которых подключен к выходу соответствующего триггера со счетным входом, причем входы разрешения записи запоминающих триггеров соединены между собой и с выходом двоичного счетчика.

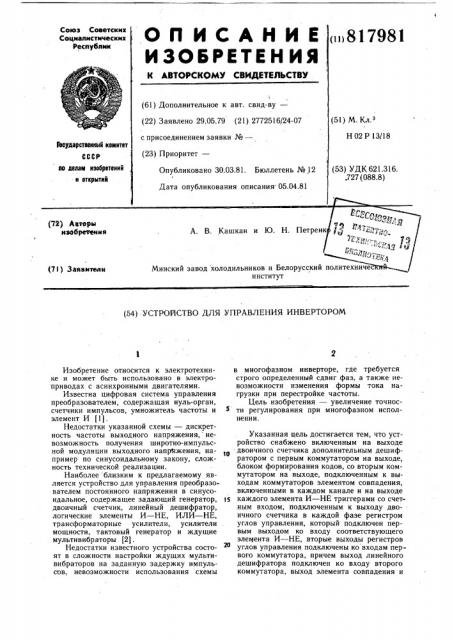

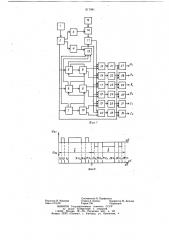

На фиг. 1 показана блок-схема предлагаемого устройства; на фиг. 2 — временная диаграмма выходных сигналов для одной фазы работы устройства.

Устройство содержит генератор 1, двоичный счетчик 2, линейные дешифраторы 3 и 4, реверсивные двоично-десятичные счетчики 5 — 7, двоичные счетчики 8 — 10, элементы 11 совпадения, блок 12 установки и формирования кодов, коммутаторы 13 и 14, элементы 15 — 20 И вЂ” НЕ, триггеры 21 — 26 со счетным входом и триггеры 27 — 32 запоминающие.

Устройство работает следующим образом.

С генератора 1 частота поступает на счетчик 2, Код счетчика 2 с помощью линейных дешифраторов 3 и 4 управляет коммутаторами 13 и 14. С выхода счетчика сигнал поступает на регистры углов управления.

Каждый регистр состоит из реверсивного двоич но-десятичного счетчика 5 — 7 и двоичного счетчика 8 — 10. Число регистров зависит от числа фаз. Все регистры засинхронизированы между собой на угол сдвига фаз, и считают до 2л,. Двоичные счетчики считают до четырех, а двоично-десятичные реверсивные счетчики от 0 до gg2 и обратно.

Коды реверсивных двоично-десятичных счетчиков 5 — 7 через коммутатор 13 поочередно соединяются с элементом 11 совпадения. На другие входы элемента ll совпадения поочередно через коммутатор 14 подсоединяются коды блока 12 установки и формирования кодов углов начала и конца импульсов модуляции. Число задаваемых углов зависит от числа импульсов широтноимпульсной модуляции в одном периоде выходного сигнала. С элемента 11 совпадения, линейного дешифратора 4 и последних триггеров счетчиков 8 — 10 сигнал приходит на элементы 15 — 20 И вЂ” НЕ. Здесь происходит распределение сигналов начала и конца импульсов модуляции по фазам полярности. С элементов 1,5 — 20 И вЂ” НЕ сигналы поступают на счетные входы триггеров 21 — 26. Выходы этих триггеров соединены со входами запоминающих триггеров

27 — 32, разрешение записи на которые осу20

Зо

50 ществляется единым импульсом с выхода двоичного счетчика 2.

На фиг. 2 показана временная диаграмма выходных сигналов устройства, в зависимости от заданных на блоке установки и формирования кодов значений углов управления широт импульсной модуляции. В верхней части диаграммы показана зависимость напряжения выхода 11вих от текущего значения фазового угла

Х1, Х И Хз.

Предлагаемое устройство позволяет в широких пределах изменять частоту и закон широтно-импульсной модуляции.

1. Устройство для управления инвертором, содержащее задающий генератор, выходом подключенный ко входу двоичного счетчика, выходом подключенного ко входу линейного дешифратора, элементы И вЂ” НЕ по числу каналов, отличающееся тем, что, с целью увеличения точности регулирования при многофазном исполнении, оно снабжено включенным на выходе двоичного счетчика дополнительным дешифратором с первым коммутатором на выходе, блоком формирования кодов, со вторым коммутатором на выходе, подключенным к выходам коммутаторов элементом совпадения, включенным на выходе каждого элемента И вЂ” НЕ триггером со счетным входом, подключенным к выходу двоичного счетчика, в каждой фазе регистром углов управления, подключенным первым выходом к соответствующему элементу И вЂ” НЕ, вторые выходы регистров углов управления подключены ко входам первого коммутатора, причем выход линейного дешифратора подключен ко входу второго коммутатора, выход элемента совпадения и выход дополнительного дешифратора подключены ко входам каждого элемента И вЂ” НЕ.

2. Устройство по п. 1, отличающееся тем, что, с целью исключения асимметрии выходного сигнала, оно снабжено двумя запоминающими триггерами, каждый из которых подключен к выходу соответствующего триггера со счетным входом, входы разрешения записи запоминающих триггеров соединены между собой и подключены к выходу двоичного счетчика.

Источники информации, принятые во внимание при экспертизе

1. Патент BHP № 164169, кл. Н 03 К 6/13, 1974:

2. Авторское свидетельство СССР № 517123, кл. Н 02 М 7/44, 1975.

817981

Риа. /

3 t

Я фиг. 2 гу/

Составитель О. Парфенова

Редактор И.Михеева Техред А. Бойкас Корректор М. Демчик

Заказ 1014/78 Тираж 730 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент>, г. Ужгород, ул. Проектная, 4