Устройство для задержки импульсов

Иллюстрации

Показать всеРеферат

О П И С А Н И Е 817992

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Респубики

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6 I ) Дополнительное к авт. свид-ву (22) Заявлено 21.05.79 (21) 2769074/18-21 с присоединением заявки М, (23) Приоритет (51)M. Кл.

Н 03 К 5/13

Гооударотввииый комитет

СССР (53 ) УД К 621.374. .5 (088.8) по делам иэооретеиий и открытий

Опубликовано 30.03,81. Бюллетень ¹12

Дата опубликования описания 30.03.81 (72), Авторы изобретения

8АЯ

ПйЖ1П., -1

БИБЛИ

С. В; Солецкий, А. М. Воловик и Ю. Д. Ивасенко (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ ИМПУЛЬСОВ

Изобретение относится к автоматике и вычислительной технике и может быть применено в вычислительных устройствах различного назначения, где необходимо получение задержки последовательностей импульсов.

Известно устройство для задержки импульсов, содержащее входную шину, которая подключена ко входу первого элемента задержки и через инвертор ко входу второго элемента задержки, триггер на двух элементах И вЂ” НЕ, единичный вход триггера соединен с выходом второго элемента задержки через последовательно соединенные дифференцирующую цепочку и инввртор, а нулевой вход триггера соединен с выходом первого элемента задержки через последовательно соединенные дифференцирующую цепочку и инвертор (1).

Наличие в устройстве дифференцирующих цепей, приводит к низкой помехозащищенности, а также усложняет гибридно-пленочную технологию изготовления;

Известно устройство для задержки импульсов, содержащее инвертор, два триггера, два элемента И вЂ” НЕ, причем единичный выход первого триггера подключен к первому входу пер вого элемента И вЂ” НЕ, выход которого .соединен нулевым входом второго триггера, а единичный выход второго триггера подключен к выходу второго элемента И вЂ” НЕ, первый вход . которого соединен с нулевым выходом первого триггера,,инвертор соединен с входной шиной, а выход инвертора подключен к первому элементу задержки. Кроме того, содержит второй элемент задержки, вход которого соединен с входной шиной, а выход подключен к нулевому входу первого триггера, единичный вход которого подключен к выходу первого элемента задержки (2).

Наряду с положительными качествами (малым числом элементов, достаточно широкими функциональными возможностями, высокой помехозащищенностью) это у..тройство имеет серьезные недостатки. Оно содержит два элемента задержки, которые могут быть выполнены в виде одновибратара и являются нетехнологичными для гибридно-пленочной технологии, так как содержат конденсаторы. Другим недостатком известного технического рего

Перед подачей положительных импульсов на вход устройства на выходе удвоителя 1 часlîòû присутствуют единичный высокий потенциал (фиг. 2, диаграмма 1). щения,йвляется сложная настройка устройства, так как для одинаковой задержки переднего и заднего фронтов входного сигнала требуется выполнить условие 1 зад = 1ээад. (где т эад. — время задержки первого элемента задержки, а г зад. — время второго элемента задержки). Настройка первого и второго элемента задержки на одинаковое время задержки является очень трудоемкой операцией: она занимает 83% времени настройки всего устройства для задержки импульсов.

Цель изобретения — повышение технологичности устройства и упрощение его настройки.

Поставленная цель достигается тем, что в устройство для задержки импульсов, содержа15 щее элемент задержки, первый инвертор, два триггера, причем единичный выход первого . триггера подключен к первому нулевому входу второго триггера, второй нулевой вход которого соединен с единичным входом первого триггера, нулевой вход первого триггера подключен к первому единичному входу второго триггера, второй единичный вход которого соединен с нулевым выходом первого триггера, первый инвертор соединен с входной шиной, элемент задержки, введены удвоитель частоты, второй инвертор, два элемента И вЂ” НЕ, причем входная шина подключена ко входу удвоителя частоты и первому входу первого элемента И вЂ” НЕ, второй вход которого подключен ко второму входу второго элемента

И вЂ” НЕ и к выходу второго инвертора, вход которого соединен с выходом элемента задержки„вход которого подключен к выходу удвоителя частоты, а второй вход второго элемента И вЂ” НЕ * подключен к выходу первого ин- з5 вертора, выход второго элемента И-HE подключен к нулевому входу первого триггера, единичный вход которого соединен с выходом первого элемента И вЂ” НЕ.

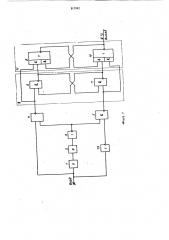

На фиг. 1 представлена функциональная схе- 4р ма устройства для задержки импульсов; на фиг. 2 — временные диаграммы его работы.

Устройство для задержки импульсов содержит удвоитель 1 частоты, выход которого подключен к элементу 2 задержки и через

45 второй инвертор 3 к первому элементу 4

И вЂ” НЕ и второму элементу 5 И вЂ” НЕ, элементы б И вЂ” НЕ и 7 И вЂ” НЕ образуют триггер 8, элементы 9 и 10 И вЂ” ИЛИ вЂ” НЕ образуют триггер 11, выход которого соединен с выходом

12 устройства для задержки импульсов, пер.вый инвертор 13.

Работа устройства осуществляется следующим образом.

На выходе элемента 2 задержки присутствует высокий уровень напряжения, а на выходе второго инвертора 3 — низкий потенциал (диаграммы 2 и 3). Низкий потенциал с выхода второго инвертора 3 приводит к образованию высоких потенциалов на выходах первого 4 и второго 5 элементов И вЂ” НЕ (диаграммы 4 и 5). Допустим, что перед подачей импульсов оба триггера находятся в состоянии

"0". При этом на выходе элемента 6 И вЂ” НЕ находится низкий потенциал (диаграмма 6), а на выходе элемента 7 И вЂ” НЕ находится викокий потенциал (диаграмма 7). На обоих нулевых входах первого элемента И схемы 9

И вЂ” ИЛИ вЂ” НЕ (диаграмма 9) присутствуют высокие потенциалы, следовательно, на его выходе будет низкий потенциал, а на выходе элемента

10 И вЂ” ИЛИ вЂ” НЕ (диаграмма 10) будет высокий потенциал, так как на втором единичном входе первого элемента И элемента 10 И вЂ” ИЛИ вЂ” НЕ— низкий потенциал и на входе второго элемента

И элемента 10 И вЂ” ИЛИ вЂ” НŠ— низкий потенциал. Таким образом, триггер 11 в нулевом состоянии, Высокий потенциал с выхода элемента 10 И вЂ” ИЛИ вЂ” НЕ поступает на вход второго элемента И элемента 9 И вЂ” ИЛИ вЂ” НЕ и подтверждает низкий потенциал на выходе 12 устройства.

В момент t появления первого входного импульса на выходе удвоителя 1 частоты формируется низкий потенциал, после чего формируется низкий уровень напряжения на выходе элемента 2 задержки. Этот сигнал образует высокий уровень напряжения на выходе второго инвертора 3, после этого к обоим входам элемента 4 И вЂ” НЕ приложены высокие уровни напряжения и на его выходе формируется низкий потенциал, который перебрасывает триггер

8 в единичное состояние, На выходе элемента

6 И вЂ” НŠ— высокий потенциал, а на выходе элемента 7 И вЂ” НŠ— низкий потенциал. Триггер 11 не меняет своего нулевого состояния, так как к первому входу первого элемента

И элемента 9 И вЂ” ИЛИ вЂ” НЕ приложен низкий потенциал. Других изменений выходных потенциалов. элементов устройства в момент t< не происходит.

По окончании периода задержки элемента

2 задержки(момент т )на его выходе появляется высокий уровень напряжения, после чего к второму входу первого элемента 4 И вЂ” НЕ и к первому входу второго элемента 5 И вЂ” НЕ приложены низкие потенциалы с инвертора 3, управляемого схемой задержания. Таким образом, на выходе первого 4 и второго 5 weментов И вЂ” НЕ будут высокие потенциалы. Второй триггер 11 перебросится иэ нулевого в единичное состояние, так как на обоих входах первого элемента И элемента 9 И вЂ” ИЛИ вЂ” НЕ находится высокий потенциалы. Таким о6ра.зом, на выходе первого элемента 9 И вЂ” ИЛИ вЂ” НЕ будет низкий потенциал, а на выходе второго элемента 10 И вЂ” ИЛИ вЂ” НЕ и на выходе устройства 12 — высокий потенциал, Других изменений выходных потенциалов элементов устройства в, момент tq не произойдет до момента tq окончания входного импульса.

В момент t на выходе.удвоителя 1 частоты формируется низкий потенциал, после чего формируется низкий уровень напряжения на выходе элемента 2 задержки. Этот сигнал образует высокий уровень напряжения иа выходе второго инвертора 3. В момент 3 на выходе первого инвертора 13 — низкий потенциал, а на его выходе будет высокий потенциал (диаграмма ,13). Таким образом, к обоим входам второго элемента 5 И вЂ” НЕ приложены высокие уровни напряжения и на его выходе формируется низкий потенциал, который перебрасывает триггер

8 в нулевое, состояние. Триггер 1 1 не меняет своего единичного состояния, так как к вто рому входу второго элемента И элемента 10

И вЂ” ИЛИ вЂ” НЕ приложен низкий потенциал. Других изменений выходных потенциалов элементов устройства в момент tq не происходит.

По окончании периода задержки элемента 2 задержки(момент тДна его выходе появляется высокий уровень напряжения, после чего ко второму входу первого элемента 4 И вЂ” НЕ и первому входу второго элемента 5 И вЂ” НЕ приложены низкие потенциалы. Таким образом, на выходе первого 4 и второго 5 элементов И вЂ” НЕ будут высокие потенциалы. Второй триггер 11 перебросится из единичного в нулевое состояние, так как на обоих входах второго элемента И элемента 10 И вЂ” ИЛИ вЂ” НЕ находятся высокие потенциалы. Таким образом, на выходе 12 устройства будет низкий потенциал.

В момент 4 все выходные сигналы элементов устройства для задержки импульсов совпадают с их исходными состояниями. Далее цикл работы повторяется.

Использование предлагаемого изобретения позволяет повысить технологичность устройства

17992 6 задержки, поскольку отпадает необходимость в изготовлении одногЬ сложного элемента задержки. Другим преимуществом устройства является простота настройки, так как не требуется подбирать одинаковые задержки в элементах задержки (настраивается только один элемент задержки) .

Формула изобретения

Устройство для задержки импульсов, содер- жащее элемент задержки, первый инвертор, два триггера, причем единичный выход первого триггера подключен к первому нулевому входу второго триггера, второй нулевой вход которого соединен с единичным входом перво, го триггера, нулевой вход первого триггера подключен к первому единичному входу второго триггера, второй единичный вход которого соединен с нулевым выходом первого триггера, первый инвертор соединен с входной шиной, элемент задержки, о т л и ч а ю щ е ес я тем, что, с целью повышения технологичности устройства и упрощения настройки, в него введены удвоитель частоты, второй инвертор, два элемента И вЂ” НЕ, причем входная шина подключена ко входу удвоителя частоты и первому входу первого элемента И вЂ” HE, второй

ЗО вход которого подключен ко второму входу второго элемента И вЂ” HE и к выходу второго инвертора, вход которого соединен с выходомэлемента задержки, вход которого подключен к выходу удвоителя частоты, а второй вход второго элемента И вЂ”,НЕ подключен к выходу первого инвертора, выход второго элемента

И вЂ” НЕ подключен к нулевому входу первого триггера, единичный вход которого соединен с выходом первого элемента И вЂ” НЕ.

Источники информации, 40 принятые во внимание при экспертизе

1. Самойлов Л. К. Устройство задержки информации в дискретной технике. М., "Сов. радио", 1973, рис. 4.1.

2. Авторское свидетельство СССР по заяв4s ке У 2573723/18-21 (прототип) .

817992 о у

Составитель И. Радько

Теходе М., Коштура Корректор В. Бутяга

Редактор Н. Кешеля

Тираж 988 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Заказ 1479/79

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4