Амплитудно-импульсный преобразова-тель

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБВЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскки

Социалистмческми

Республик 418005 (6l ) Дополнительное к авт. свид-ву (22) Заявлено 04.05.79 (21) 27б2354/18.21 (51)M. Кл.

Н 03 К 13/20 с присоединением заявки М

Гоеударотиаииый комитет

СССР ио делам изобретеиий и открытий (28) Приоритет

Опубликовано 3003 81. Бюллетень М 12

Дата опубликования описания 30.03.81 (53) УЙК 621374 (088.8) (72) Авторы изобретения

А. Д. Кукушкин и Б. Н. Усов (7I) Заявитель (54) АМПЛИТУДНΠ— ИМПУЛЬСНЫЙ ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к преобразователям сигналов из дискретной формы в аналоговую и может быть использовано в импульсных и цифровых системах автоматического управления в качестве согласующего звена между вычислительными и исполнительными устройствами системы.

Известны амплитудно-импульсные преобразователи с экстраполяцией первого порядка, часто называемые экстрапопяторами, интерполяторами, демодуляторами, запоминающими элетО ментами первого порядка и т,п.(1).

Такие устройства для формирования выходного Сигнала используют входной сигнал и его первую обратную разность и обладают ограниченным быстродействием.

IS

Наиболее близким по технической сущности к предлагаемому являетса амплитудно-импульс. ный преобразователь, который содержит gse последовательно включенные аналоговые заломи. нающие ячейки АЗЯ, два сумматора, интегратор, цва переключателя и формирует выходной сигнал в вице кусочно-линейной функции по алгоритмч экстраполяции (2J..

Основной недостаток устройства состоит в наличии искажений при формировании линейной части сигнала.

Кроме того, время, необходимое для записи сигналов, определяется быстродействием

АЗЯ и ограничивает минимальное значение периода дискретности системы, что ограничивает сверху частотный диапазон входных сигналов, а также предъявляет повышенные требования к быстродействию переключателей.

Бель изобретения — уменьшение нелинейных искажений и расширение рабочего частотного диапазона преобразователя.

Поставленная цель достигается тем, что в амплитудно-импульсный преобразователь, со. держащий две аналоговые запоминающие ячей ки, вход первой из которых соединен со входными клеммами через контакты одного переключателя, а вход второй через контакты второго переключателя подключен к выходу первой аналоговой запоминающей ячейки, и интегратор, включенный между выходом первого и входом второго сумматоров, другие входы которых подклюяены к выходу первой анало818005 4 через контакты переключателя 9, и именно та, в которой хранится значение предыдущего входного сигнала, а на второй вход сумматора с выхода ячейки 1 поступает значение текущего сигнала, выходной сигнал сумматора будет пропорционален их разности, так как ячейки являются инвертирующими. Коэффициент передачи сумматора 4 равен К Тэ. С выхода сумматора 4 сигнал поступает на вход интегратора 5, гце преобразуется в линейно-изменяющийся сигнал.

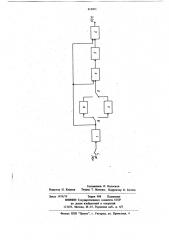

25 говой запоминающей ячейки, введены дополнительная запоминающая ячейка и третий переключатель, при этом вход дополнительной запоминающей ячейки соединен с выходом первой аналоговой запоминающей ячейки через вторую пару контактов второго переключателя, а выходы второй аналоговой и дополнительной запоминающих ячеек соединены со входом первого сумматора через контакты третьего переключателя., На чертеже представлена функциональная схема предлагаемого амплитудно-импульсного преобразователя с экстраполяцией первого порядка.

Амплитудно-импульсный преобразователь содержит три аналоговые запоминающие ячейки

АЗЯ, 1 — 3, сумматор 4, интегратор 5, сумматор 6, три переключателя 7 — 9.

Выход сумматора 6 является выходом устройства. Вход ячейки 1 через контакты переключателя 7 подключен ко входным зажимам . устройства, входы ячеек 2 и 3 подключены к выходу ячейки 1 через контакты переключателя 8, а выходы этих ячеек через контакты переключателя 9 соединены со входом сумматора 4. Другой вход сумматора 4 соединен с выходом ячейки 1. Выход сумматора 4 соединен со входом интегратора 5, выход которого подключен к одному входу сумматора 6. Второй вход сумматора 6 соединен с выходом ячейки 1.

Переключатели срабатывают одновременно.

Переключатель 7 подключает вход ячейки 1 ко входным зажимам на время, необходимое для записи значения входного сигнала. Переключатель 8 подключает к выходу ячейки 1 вход одной из ячеек 2 или 3 (например, 2) на время, равное Тр, а переключатель 9 подключает выход другой из этих ячеек (например 3), в которой уже записано предыдущее значение входного сигнала, ко входу сумматора 4 тоже на время Те.

В следующем такте переключатели вновь срабатывают. Переключатель 8 подключает вход ячейки 3 к выходу ячейки 1, а переключатель

9 — выход ячейки 2 ко входу сумматора 4.

Таким образом, время записи информации в ячейки 2 и 3 увеличивается до значения, равного Тр, а время, в течение которого выходной сигнал сумматора 4 не будет соответствовать расчетному значению, уменьшается в два раза.

Нетрудно показать, что верхняя граница частотного диапазона входного сигнала при этом увеличивается в два раза.

Ко входу сумматора 4 и каждом такте на время Те подключается одна из ячеек 2 и 3

Выходной сигнал интегратора и входной сигнал суммируются на выходном сумматоре

6. На выходе получаем сигнал, соответствующий принятому алгоритму.

Таким образом, предлагаемый амплитудноимпульсный преобразователь позволяет по сравнению с известными амплитудно-импульс20 ными преобразователями уменьшить в два раза время действия на верхнюю границу частотного диапазона.

Формула изобретения

Амплитудно-импульсный преобразователь, содержиций две аналоговые запоминающие ячеики, вход первой из которых соединен со входными клеммами через контакты одного переключателя, а вход второй через контакты второго переключателя подключен к выходу первой аналоговой запоминающей ячейки, и интегратор, включенный между выходом пер35 вого и входом второго сумматоров, другие входы которых подключены к выходу первой аналоговой запоминающей ячейки, о т л ич а ю шийся тем, что, с целью уменьшения нелинейных искажений и расширения ра40 бочего частотного диапазона преобразователя, в него введены дополнительная запоминающая ячейка и третий переключатель,.при этом вход дополнительной запоминающей ячейки соединен с выходом первой аналоговой запоминающей

45 ячейки через вторую пару контактов второго переключателя, а выходы второй аналоговой и дополнительной запоминающих ячеек соединены со входом первого сумматора через контакты третьего переключателя.

Источники информации, принятые во внимание при экспертизе

1. Заявка Великобритании No ?40487, кл. Н 03 К 13 01, 1975.

2. Кузин Л. Т..Расчет и проектирование дискретных систем управления. М., Машгиэ.

1962, с. 41.

Составитель Л. Колосков Редактор Н. Кешеля Техред T. Mamma Корректор В, Бутяга

Заказ 1479/79 Тираж 988 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4