Устройство согласования ттл-схемс мдп-интегральными схемами

Иллюстрации

Показать всеРеферат

„,>818015

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К .АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советски к

Социалистических

Республик (61) Дополнительное к авт. свид-ву— (22) Заявлено 09.04.79 (21) 2747789/18-21 с присоединением заявки №вЂ” (23) Приоритет— (51) М. К .

Н 03 К 19/09

Государственный комитет

СССР ао делам изобретений и открытий (53) УДК 621.375..083 (088.8) Опубликовано 30.03.81. Бюллетень №12

Дата опубликования описания 05.04.81 (72) Авторы изобретения

В. И. Золотаревский, В. М. Некрасов, В. П. Сидоренко и А. Д. Ткачук (71) Заявитель

) 1 (54) УСТРОЙСТВО СОГЛАСОВАНИЯ ТТЛ СХЕМ

С МДП ИНТЕГРАЛЬНЫМИ СХЕМАМИ

Изобретение относится к автоматике и вычислительной технике и может быть использовано для согласования диодно-транзисторных и транзисторно-транзисторных логических (ДТЛ и ТТЛ) схем и МДП интегральными схемами на дополняющих тран- S зисторах.

Известно устройство согласования ТТЛ схем с МДП интегральными схемами, выполненное на дополняющих МДП-транзисторах, содержащее входной транзистор, первый и второй инверторы (1).

Недостатком такого устройства является невозможность согласования ТТЛ схем с МДП интегральными схемами, напряжение питания которых превышает напряжение питания ТТЛ схем.

Известно также устройство согласования

ТТЛ схем с МДП интегральными схемами,выполненное на дополняющих МДП-трайзисторах и содержащее входной транзистор, первый, второй и третий инверторы, причем затвор и-канального транзистора третьего 2о инвертора соединен с выходом первого инвертора, а затвор п-канального транзистора второго инвертора — с входом устройства (21.

Недостатком известного устройства является невозможность использования для согласования ТТЛ схем с МДП интегральными схемами на дополняющих транзисторах, питающимися от разнополярных источников напряжения, так как при логическом

«О» на входе устройства не будет обеспечиваться режим закрывания и-канальных транзисторов первого и второго инверторов, т.е. узкие функциональные возможности.

Цель изобретения — расширение функциональных возможностей.

Поставленная цель достигается тем, что в устройство, выполненное на дополняющих МДП-транзисторах, содержащее входной транзистор, затвор которого подключен к.шине нулевого потенциала, исток — к шине первого источника положительного напряжения, сток — к затвору р-канального транзистора первого инвертора, включенного между шинами первого источника положительного напряжения и источника отрицательного напряжения, второй и третий инверторы, включенные между шинами второго источника положительного напряжения и источника отрицательного напряжения, зат818015

Формула изобретения

55 вор и-канального транзистора второго инвертора подключен к затвору и-канального транзистора первого инвертора, выход которого подключен к затвору и-канального транзистора третьего инвертора, затворы р-канальных транзисторов второго и третьего инверторов подключены соответственно к выходам третьего и второго инверторов, введены два МДПтранзистора. исток и-канального транзистора подключен к шине источника отрицательного напряжения, затвор подключен к выходу первого инвертора, сток — к затвору и-канального транзйстора первого инвертора и стоку р-канального транзистора, затвор которого подключен к шине нулевого потенциала, а исток — ко входу устройства и стоку входного транзистора.

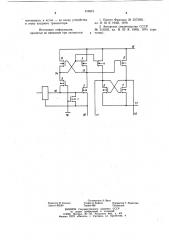

На чертеже представлена принципиальная электрическая схема устройства согласования ТТЛ схем с МДП интегральными схемами, выполненного на дополняющих транзисторах.

Устройство содержит входной транзистор 1, первый инвертор иа транзисторах 2 и 3, второй и третий инверторы на транзисторах 4 — 7, два последовательно соединенных транзистора 8 и 9, вход 10 устройства, первый и второй выходы 11 и 12 устройства, выход 13 первого инвертора, точку 14 соединения двух последовательно соединенных транзисторов, шину 15 источника отрицательного напряжения (-Ei ), шину 16 первого источни ка положительного напряженйя (+E ), шину 17 второго источника положительного напряжения (+ Ез ) 17, шину 18 нулевого потенциала., Входной транзистор 1 предназначен для повышения уровня логической «1» на входе устройства.

Устройство работает следующим образом.

Пусть в исходном состоянии уровень на входе 10 устройства соответствует логической .«1». При этом транзистор 3 закрыт, а транзистор 9 открыт. В точках 13 и 14 установятся значения напряжений, близкие к напряжениям -Е и +Ез соответственно.

Эти напряжения прикладываются к затворам транзисторов 4 и 6, которые находятся соответственно в открытом и закрытом состояниях. Потенциалы на выходах 11 и 12 будут равны -Е и +Ег. За счет действия входного транзистора 1 напряжение на входе 10 устройства устанавливается близким к напряжению питания +Ез, обеспечивает надежное закрывание транзистора 3.

При поступлении на вход 10 устройства логического «О» транзистор 3 открывается, а транзистор 9 закрывается. Транзистор 2

cure открыт и образует с транзистором 3 делитель напряжения, напряжение в точке

13 которого определяется отношением крутизны транзисторов 2 и 3. При правильном выборе крутизны транзисторов 2 и 3 напряжение в точке 13 должно обеспеечивать открывание транзистора 8, что приводит к изменению напряжения в точке 14. Это изменение напряжения передается на затвор транзистора 2 и он закрывается, напряжение в точке 13 увеличивается.

Процесс открывания транзистора 8 и закрывания транзистора 2 протекает лавинообразно до тех пор, пока напряжение в точке 14 не достигнет значения, близкого к - Е .

При этом транзистор 2 закрывается и в точке 13 устанавливается напряжение, близкое к + E> и одновременно закрывается транзистор 4 и открывается транзистор 6. При соответствующем выборе крутизны транзисторов 4-7 на выходах 11 и 12 устанавливаются напряжения, близкие к +Ез и -Е .

Переключение устройства в противоположное состояние происходит аналогичным образом.

Введение двух последовательно соединен А1х транзисторов расширяет функциональнь1е возможности предложенного устройства, так как обеспечивает возможность согласования ТТЛ схем с МДП интегральными схемами на дополняющих транзисторах, питающимися от разнополярных источников напряжения. . Устройство согласования ТТЛ схем с

МДП интегральными схемами, выполненное на дополняющих МДП-транзисторах, содержащее входной транзистор, затвор которого подключен к шине нулевого потенциала, исток — к шине первого источника положительного напряжения, сток — к затвору р-канального транзистора первого инвертора, включенного между шинами первого источника положительного напряжения и источника отрицательного напряжения, второй и третий инверторы, включенные между шинами второго источника положительного напряжения и источника отрицательного напряжения, затвор и-канального транзистора второго инвертора подключен к затвору и-канального транзистора первого инвертора, выход которого подключен к затвору п-канального транзистора третьего инвертора, затворы р-канальных транзисторов второго и третьего инверторов подключены соответственно к выходам третьего и второго инверторов, отличающееся тем, что, с целью расширения функциональных возможностей, в устройство введены два

МДП-транзистора, исток и-канального транзистора подключен к шине источника отрицательного напряжения, затвор подключен к выходу первого инвертора, сток — к затвору п-канального транзистора первого инвертора и стоку р-канального транзистора, затвор которого подключен к шине нулевого

818015

Составитель А. Янов

Редактор Н. Кешеля Техред А. Бойкас Корректор Г. Решетняк

Заказ 1462 80 Тираж 988 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4 потенциала, а исток — ко входу устройства и стоку входного транзистора.

Источники информации, принятые во внимание при экспертизе

1. Патент Франции № 3273921, кл. Н 03 К 19/40, 1978.

2. Авторское свидетельство СССР № 513502, кл. Н 03 К 19/00, 1974 (прототип).