Параллельно-последовательныйаналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Социалисткческик

Республик

819952 (61) Дополнительное к авт. свид-ву— (22) Заявлено 08.12.78 (21) 2693619/18-21 (51) У, К з

Н 03 К 13/03 с присоединением заявки №вЂ”

° Гввуддрстееииый кемнтет

СССР ав делам нзебретеиий и открытий (23) Приоритет— (53) УДК 681.325 (088.8) Опубликовано 07.04.81. Бюллетень №13

Дата опубликования описания 17.04.81 (72) Авторы .изобретеыия

А. И. Воителев и Л. М. Лукьян (71) Заявитель (54) ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫЙ АНАЛОГОЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к импульсной технике, в частности к преобразователям аналоговых сигналов в цифровые с повышенным быстродействием, и предназначено для построения на его основе систем сбора аналоговой информации для управляющих вычислительных комплексов.

Известен преобразователь, содержащий блок сравнения, состоящий из аналоговых компараторов с триггерами-защелками на выходах, каждый из которых; кроме старшего, имеет на выходе элемент несовпадения, при этом первые входы всех компараторов соединены с первым выходом аналогового переключателя и с выходом аналогового ключа, второй вход каждого аналогового компаратора соединен с соответствующим выходом формирователя эталонных уровней, общий стробирующий вход триггеровзащелок соединен с первым выходом блока управления, выход каждого триггера защелки, кроме старшего, соединен с прямым входом соответствующего элемента несовпадения, инверсный вход которого соединен с выходом соседнего старшего триггера-защелки, выход старшего триггера-защелки и выходы всех элементов несовпадения соединены с входами шифратора, выходы которого соединены с первыми входами регистра, вторым и третьим входами соединенного соответственно с вторым и третьим выходами блока управления, четвертый и пятый выходы которого соединены с управляющими входами соответственно аналогового ключа и аналогового переключателя, сигнальный вход аналогового ключа соединен с выходом вычитателя, соединенного входом суммирования с вторым выходом аналогового nepe)o ключателя, сигнальный вход которого соединен с входной шиной, а также цифро- аналоговый преобразователь, входами соединенный с выходами регистра и выходомс входом вычитания вычитателя (1).

Этот преобразователь обладает сравнительно невысоким быстродействием из-за формирования сигнала обратной связи с помощью цифроаналогового преобразователя, выходной сигнал которого начинает изменяться только после записи в регистр кода первого такта преобразования.

Целью изобретения является повышение быстродействия преобразования аналогового сигнала в код.

819952

Достигается это тем, что в параллельнопоследовательный аналого-цифровой преобразователь, содержащий блок сравнения, состоящий из аналоговых компараторов, каждый из которых на выходе имеет триггер-защелку, при этом первые входы всех компараторов соединены с первым выходом аналогового переключателя и с выходом аналогового ключа, второй вход каждого аналогового компаратора соединен с соответствующим выходом формирователя эталонных уровней, общий стробирующий вход триггеров-защелок соединен с первым выходом блока управления, выход каждого триггера-защелки, кроме старшего, соединен с прямым входом соответствующего элемента несовпадения, инверсный вход которого

15 соединен с выходом соседнего старшего триггера-защелки, выход старшего триггера-защелки и выходь1 всех элементов несовпадения соединены с входами шифратора, выходы которого соединены с первыми входами регистра, вторым и третьим входами го

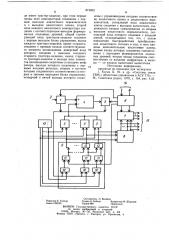

Преобразователь работает следующим образом, Сначала блок 6 формирует сигнал для гашения регистра 7 и одновременно устанавливает такие уровни сигналов, что ключ 3 запирается, аналоговый переключатель 1 устанавливается в такое состояние, когда преобразуемый аналоговый сигнал напряжения постоянного тока с входной шины 2 проходит через этот переключатель, поступая далее на общий вход компараторов

10 блока аналогового сравнения 9. Затем блок 6 формирует стробирующий сигнал, по которому результат сравнения преобразуе50

55 соединенного соответственно с вторым и третьим выходами блока управления, четвертый и пятый выходы которого соединены с управляющими входами соответственно аналогового ключа и аналогового переключателя, сигнальный вход аналогового ключа соединен с выходом вычитателя, соединенного входом суммирования с вторым выходом аналогового переключателя, сигнальный вход которого соединен с входной шиной, введены дополнительные аналоговые ключи, первые входы которых соединены соответственно с выходами формирователя эталонных уровней, вторые входы соединены соответственно с входами шифратора, а выходы — с входом вычитания вычитателя.

На чертеже представлена структурная З5 схема параллельно-последовательного аналого-цифрового преобразователя, содержащего аналоговый переключатель 1; входную шину 2, аналоговый ключ 3, аналоговый вычитатель 4, дополнительные аналоговые ключи 5, блок управления 6, регистр 7, 40 шифратор 8, блок аналогового сравнения 9, содержащий компараторы 10, триггеры-защелки 11 и элементы несовпадения 12, формирователь эталонных уровней 13, шину связи с микропроцессором 14, выходные 45 шины 15.

4 мого сигнала с уровнями, формируемыми блоком 13 и поступающими на вторые входы компараторов 10, запоминается в триггерах-защелках в виде унитарного кода. Запоминаемый в этих триггерах унитарный код результата сравнения преобразуется в позиционный код на выходах элементов несовпадения 12. Преобразование унитарного кода в позиционный заключается в том, что каждый триггер ll, находящийся в единичном состоянии, запрещает по инверсному входу элемента 12 прохождение через его прямой вход единичного сигнала с выхода соседнего младшего триггера 11. Поэтому сигнал логической единицы будет на выходе только того элемента, который соответствует в данном случае наиболее старшему триггеру 11, находящемуся в единичном состоянии.

Сигналы позиционного кода далее преобразуются в двоичный код с помощью шифратора 8 и одновременно подаются на управляющие входы дополнительно введенных аналоговых ключей 5. Один из этих ключей на вход которого поступает сигнал логической единицы, открывается и на вход вычитателя 4 поступает аналоговый сигнал, уровень которого соответствует результату преобразования первого такта. Первый такт преобразования заканчивается записью кода в регистр 7 по сигналу, формируемому блоком 6. Одновременно с этой записью блок 6 изменяет уровни выходных сигналов так, что ключ 3 открывается и переключатель 1 устанавливается в такое состояние, когда преобразуемый сигнал проходит на суммирующий вход вычитателя 4. Затем, после установления сигнала на общем входе компараторов 10, блок 6 вновь формирует сигналы стробирования для триггеров 11.

После этого код результата преобразования с выходов блоков 7 и 8 может быть передан в микропроцессор по сигналу, поступающему с шины 14.

Расмотренный параллельно-последовательный аналого-цифровой преобразователь выгодно отличается от преобразователя прототипа, так как обладает большим быстродействием. Это объясняется тем, что второй такт преобразования начинается без ожидания записи кода первого такта преобразования в регистр и его преобразования в аналоговый сигнал обратной связи. Кроме того, схема преобразователя проще известного, так как формирование сигнала обратной связи выполняется без использования сложного аналогового узла — цифроаналогового преобразователя.

Формула изобретения

Параллельно-последовательный аналогоцифровой преобразователь, содержащий блок сравнения, состоящий из аналоговых компараторов, каждый из которых на выхо819952

Составитель Л. Беляева

Редактор Е. Гончар Техред А. Бойкас Корректор М. Шароши

Заказ 1262/35 Тираж 988 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», r. Ужгород, ул. Проектная, 4 де имеет триггер-защелку, при этом первые входы всех компараторов соединены с первым выходом аналогового переключателя и с выходом аналогового ключа, второй вход каждого аналогового компаратора соединен с соответствующим выходом формирователя эталонных уровней, общий стробирующий вход триггеров-защелок соединен с первым выходом блока управления, выход каждого триггера-защеЛки, кроме старшего, соединен с прямым входом соответствующего элемента несовпадения, инверсный вход 0 которого соединен с выходом соседнего старшего триггера-защелки, выход старшего триггера-защелки и выходы всех элементов несовпадения соединены со входами шифратора, выходы которого соединены с первыми входами регистра, вторым и третьим входами соединенного соответственно со вторым и третьим выходами блока управления, четвертый и пятый выходы которого соедииены с управляющими входами соответственно аналогового ключа и аналогового переключателя, сигнальный вход аналогового ключа соединен с выходом вычитателя, соединенного входом суммирования со вторым выходом аналогового переключателя, сигнальный вход которого соединен с входной шиной, отличающийся тем, что, с целью повышения быстродействия преобразования аналогового сигнала в код, в него введены дополнительные аналоговые ключи, первые входы которых соединены соответственно с выходами формирователя эталонных уровней, вторые входы соединены соответственно со входами шифратора, а выходы — со входом вычитания вычитателя.

Источники информации, принятые во внимание при экспертизе

1. Каган Б. М. и др. «Системы связи

УВМ с объектами управления в АСУ ТП»,—

М., Советское радио, 1978, с. 164, рис. 4.23.