Делитель частоты с дробным автоматическиизменяющимся коэффициентом деления

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскии

Социалистических

Республик п>819966 (61) Дополнительное к авт. свид-ву— (22) Заявлено 01.02.79 (21) 2719255/18-21 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл.з

Н 03 К 23/00

Гооударстееииый комитет (53) УДК 621.374..44 (088.8) Опубликовано 07.04.81. Бюллетень,№ 13

Дата опубликования описания 17.04.8! ао делам изобретеиий и открытий (72) Автор изобретения

А. А. Михайлов (7!) Заявитель (54) ДЕЛИТЕЛЬ ЧАСТОТЫ С ДРОБНЫМ АВТОМА1ИЧЕСКИ" - :.";:

ИЗМЕНЯЮЩИМСЯ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ

Изобретение относится к импульсной технике и может быть использовано в синтезаторах частоты, измерителях частоты и других устройствах для деления частоты периодических импульсов в дробное число раз.

Известен делитель частоты с дробным коэффициентом деления, содержащий две пересчетные схемы, каждая из которых состоит из дешифратора с подключенным к нему счетчиком с одним счетным входом и входом установки нулевого состояния, двух вентилей с двумя раздельными входами и одним выходом, который подключен к одному из входов элементов ИЛИ, и триггер со счетным входом, причем вход установки нулевого состояния одного из счетчиков подключен к счетному входу другого счетчика, вход установки нулевого состояния которого подключен к счетному входу триггера, при этом одни одноименные раздельные входы вентилей объединены между собой и соединены с выходами триггера, а другие одноименные входы вентилей подключены к выходам дешифраторов своих пересчетных схем (1).

Однако отсутствие возможности автоматической установки коэффициента деления, что необходимо в системах автоматического регулирования частоты, является погрешностью устройства.

Известен также делитель частоты с автоматически изменяющимся коэффициентом деления, содержащий счетчик целого числа, разрядные выходы которого подключены к одним входам блока поразрядного совпадения, и реверсивный счетчик це1о лой части коэффициента деления, разрядные выходы которого подключены к другим входам блока поразрядного совпадения (2).

Целью изобретения является повышение точности деления.

Для этого в делитель частоты с дробным автоматически изменяющимся коэффициентом деления, содержащий счетчик целого числа, разрядные выходы которого подключены к одним входам блока поразрядного. совпадения, и реверсивный счетчик целой части коэффициента делечия, разрядные выходы которого подключечы к другим входам блока поразрядного совпадения, введены делитель частоты с переменным коэффициентом деления (ДПКД) с бло2О

55 ком установки целой части знаменателя, регистр числителя с блоком установки целой части числителя, блок разрешения записи, блок установки целой части делителя, многовходовой элемент совпадения и триггер, причем выход блока поразрядного совпадения соединен с входом установки нуля счетчика целого числа н со счетным входом ДПКД, установочные входы которого подключены к выходам блока разрешения записи, а разрядные выходы — к одним из входов многовходового элемента совпадения, выход которого соединен с входом установки нуля ДПКД и с одним из входов триггера, другой вход которого подключен к выходу ДПКД, первый выход — к .входу вычитания реверсивного счетчика целой части делителя, установочные входы которого соединены с выходами блока установки целой части делителя, а второй выход — к входу сложения реверсивного счетчика целой части делителя, к входу разрешения записи блока разрешения записи и к входу запрета многовходового элемента совпадения, при этом выходы регистра числителя соединены с разрядными входами блока разрешения записи и с другими входами многовходового элемента совпадения.

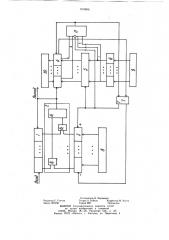

На чертеже представлена структурная электрическая схема делителя частоты с дробным автоматически изменяющимся коэффициентом деления.

Устройство содержит счетчик 1 целого числа, блок 2 поразрядного совпадения, реверсивный счетчик 3 целой части делителя, делитель частоты 4 с переменным коэффициентом . деления (ДПКД), блок 5 разрешения записи, регистр 6 числителя, триггер 7, блоки 8 установки целой части делителя, блок 9 установки целой части числителя, блбк 10 установки целой части знаменателя, многовходовой элемент совпадения 11.

Выходы счетчика 1 целого числа, подключены к входам блока 2 поразрядного совпадения, к вторым входам которого подключены выходы реверсивного счетчика 4, выход блока 2 поразрядного совпадения подключен к входу установки нуля счетчика 1 целого числа и счетному входу ДПКД 4, установочные входы которого через блок 5 разрешения записи соединены с выходами регистра 6 числителя.

Первые входы элемента совпадения 11 подключены к разрядным выходам ДПКД 4, вторые входы — к выходам регистра 6 числителя, а выход элемента совпадения 11 подключен к входу установки нуля ДПКД 4 и к установочному входу триггера 7. Второй установочный вход триггера 7 соединен с выходом ДПКД 4, причем первый выход триггера 7 подключен к входу разрешения записи блока разрешения записи

5 и к входу вычитания реверсивного счетчика 3, а второй выход триггера 7 соеди

1О

25 зо

4 нен с входом сложения реверсивного счетчика 3. К установочным входам реверсивного счетчика 3, ДПКД 4 и регистра числителя 6 подключены соответственно блоки установки 8 целой части делителя, его числителя 9 и знаменателя 10.

Работает делитель частоты следующим образом.

Через блоки установки в счетчик 3, ДПКД 4 регистр числителя 6 введены коды целой части, числителя и знаменателя коэффициента деления.

Рассмотрим работу делителя частоты на примере реализации дробного коэффициента деления.

Пусть требуемый коэффициент деления равен

К=A+, где А — целая часть коэффициента деления; с — числитель дробной части коэффициента деления;  — знаменатель дробной части коэффициента деления.

Эти числа определяют основные параметры устройства. Объем счетчика 1 целого числа должен быть А+ 1. ДПКД 4 должен иметь количество разрядов: и =

= (logo/), а регистр числителя 7 — m=

= (1щг.о ) .

Входные импульсы устройства подаются на вход счетчика 1.

При совпадении показаний счетчика 1 и реверсивного счетчика 3 блок поразрядного совпадения 2 выдает импульс на установку в ноль счетчика 1. Код целой части коэффициента деления заносится в реверсивный счетчик 3 блоком установки 8 целой части коэффициента деления. Делитель частоты с переменным коэффициентом деления 4 составляет деление входных импульсов на коэффициент, определенный блоком 10 установки знаменателя. В регистр

6 числителя заносится числитель дробной части делителя с помощью блока установки числителя 9. Блок 5 разрешения записи осуществляет при подаче на его выход разрешение записи единицы, перезапись состояния регистра 6 в ДПКД 4 через установочные входы. Триггер 7 предназначен для поочередной подачи единицы на входы сложения и вычитания реверсивного счетчика 3 и подачи импульса перезаписи состояния регистра числителя 6 в

ДПКД 4.

При этом импульс осуществляет запрет работы элемента совпадения 11. Элемент совпадения 11 устанавливает ДПКД 4 в нулевое состояние при совпадении показаний регистра числителя 6 и ДПКД 4, Установка триггера 7 в исходное состояние осуществляется с выхода ДПКД 4.

В исходном состоянии в счетчик 1 занесены нули, чеоез блоки установки 8 и 9 в реверсивном счетчике 3 и регистре чис8

5 лителя 5, установлены соответственно целая часть делителя и числитель дробной части. Триггер 7 находится в состоянии, когда разрешена перезапись из регистра числителя 6 в ДПКД 4 и запрещена работа элемента совпадения 11. В блоке 10 установки знаменателя набран код знаменателя, а в ДПКД 4 через блок 5 разрешения записи при установке в регистре б числителя кода числителя записан числитель.

Входные импульсы заполняют счетчик 1 до тех пор пока показания счетчика 1 и показания реверсивного счетчика 3 (в нем записано число А) не совпадут. При этом блок поразрядного совпадения 2 вырабатывает единицу, которая установит счетчик 1 в нулевое состояние. Импульсы установки в нуль счетчика 1 считываются

ДПКД 4 до его заполнения, причем исходным состоянием ДПКД 4 будет Ы. Импульс переполнения ДПКД 4 через P — 4 импульсов перебросит триггер 7 в состояние, запрещающее перезапись из регистра 6 в

ДПКД 4, включит элемент совпадения 11 и к показанию реверсивного счетчика 3 по каналу сложения прибавит единицу. После этого произойдет заполнение счетчика 1 до величины А+ 1 и подсчет импульсов установки в ноль счетчика 1 ДПКД 4 до значения с(.

При совпадении показаний ДПКД 4 и регистра числителя 6 элемент совпадения

11 выдаст импульс на сброс ДПКД 4 в ноль. Далее все процессы повторяются.

Последовательность операций может быть и обратной.

Всего за время пребывания реверсивного счетчика 3 в состоянии А ДПКД 4 просчитывает ф — с импульсов, а за время пребывания реверсивного счетчика 3 в состоянии А+ 1 — с импульсов. Всего на вход устройства за один цикл работы поступает А(ф — с ) + (А+1) А=АД+с импульсов. 1 аким образом коэффициент деления за цикл устройства равен 1- = А+—

„в

19966

Формула изобретения

Делитель частоты с дробным автоматически изменяющимся коэффициентом деления, содержащий счетчик целого числа, разрядные выходы которого подключены к одним входам блока поразрядного совпадения, и реверсивный счетчик целой части коэффициента деления, разрядные выходы которого подключены к другим входам блока поразрядного совпадения, отличающай<о ся тем, что, с целью повышения точности деления, в него введены делитель частоты с переменным коэффициентом деления

ДПКД, с блоком установки целой части знаменателя, регистр числителя с блоком установки целой части числителя, блок разрешения записи, блок установки целой части делителя, многовходовый элемент совпадения и триггер, причем выход блока поразрядного совпадения соединен с входом установки нуля счетчика целого числа и со счетным входом ДПКД, установленные входы которого подключены к выходам блока разрешения записи, а разрядные выходы— к одним из входов многовходового элемента совпадения, выход которого соединен с входом установки нуля ДПКД и с одним из входов триггера, другой вход которого подключен к выходу ДПКД, первый выход к входу вычитания реверсивного счетчика целой части делителя, установочные входы которого соединены с выходами блока усзо тановки целой части делителя, а второй выход — к входу сложения реверсивного счет чика целой части делителя, к входу разрешения записи блока разрешения записи и к входу запрета многовходового элемента совпадения, при этом выходы регистра чисЗ5 лителя соединены с разрядными входами блока разрешения записи и с другими входами многовходового элемента совпадения.

Источники информации принятые во внимание при экспертизе

l. Авторское свидетельство СССР

4о № 437229, кл. Н 03 К 23/02, 197!.

2. Авторское свидетельство СССР № 451199, кл. Н 03 К 23/00, 1972 (прототип) .

819966

Составитель В. Чернышев

Редактор Е. Гончар Техред А. Бойкас Корректор М. Коста

Заказ 1259/36 Тираж 988 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий! 13035, Москва, % — 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4