Устройство для формирования временныхинтервалов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Респуублик (61) Дополнительное к ввт; свид-ву (22) Заявлено 2 10278 (21) 2 58 3 304/18-24 с присоединением заявки ¹ (23) Приоритет

Опубликовано 150481. Бюллетень 89 14 (51) М. Кл з 6 06 F 1/04

Государственный комитет

СССР во яеявм брии и открытий (53) УДК 681 325 (088. 8) Дата опубликования описания 25. 04. 81

Ю.О.Абугов, К.И.Диденко, Г.И.Загарий, В.И. и E.M.Ùåâåëåâ. (72) Авторы изобретения

3 ч

Специальное конструкторское бюро систем авФффт ческого управления Министерства приборостроения, средств автоматизации и систем управления СССР / - " -:: .. у . .!., „ (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ВРЕМЕНННХ

ИНТЕРВАЛОВ

Изобретение отнобится к автоматике и может найти применение при поостроении систем программного и логического управления, когда возникает необходимость формирования последовательности управляющих временных команд для исполнительных устройств одной технологической цепи, причем длительности команд могут отличаться друг от друга на одни или несколько порядков. Кроме того, устройство может. использоваться для подсчета и выдачи сигналов при достижении заданного количества импульсов, что позволяет производить до- 15 зировку материала или иэделий по за данной программе. известны устройства формирования временных интервалов, основанные на 20 использовании цифровых схеМ и содер жащие счетчик, соединенный через дешифраторы с входами управляющих триггеров j1).

Недостатком таких устройств явля-. 25 ется то, что для получения последовательности временных команд необходимо использовать несколько таких устройств, что значительно увеличивает аппаратурные затраты. 30

Известно устройство для формирования временных интервалов, содержащее управляющие триггеры, счетчик, элементы ИЛИ, дешифратор и коммутатор, адресные шины которого соединены с единичными выходами управляющих триггеров и входами элемента

ИЛИ, выход которого соединен с нулевым установочным входом счетчика, счетный вход которого соединен с выходом коммутатора, информационные шины которого соединены с источником фиксированных частот (2J.

Недостатками этого устройства являются: ограниченные функциональные возможности, т.е. оно работает по жесткой программе, для изменения которой необходима перепайка выводов дешифратора, а также низкая помехоустойчивость.

Наиболее близким к предлагаемому является устройство для формирования временных интервалов, содержащее счетчик, на вход которого подается частота с генератора тактовых.импульсов, выходы счетчика подключены к первой группе входов схемы сравнения, выход которой подключен к одному из входов триггера, дру822 1б4 гой вход которого подключен к шине запускающего сигнала. Другая группа входов схемы сравнения соединена с выходами задающего устройства (блока памяти) (3).

Недостатком такого устройства является невозможность формирования нескольких последовательных временных интервалов, поступающих на различные выходы, что бывает необходимо при построении устройств программного управления техноЛогическими агрегатами.

Кроме того, ввиду наличия единственного генератора тактовой частоты, затруднено формирование временных интервалов, порядок которых различен.

Цель изобретения — расширение функциональных ноэможностей устройства.

Для достижения поставленной цели устройство для формирования временных интервалов, содержащее блок памяти, счетчик, схему сравнения, триггер, причем, выходы счетчика соединены с первой группой входов схемы сравнения, выход .которой соединен с первым входом триггера, единичный вход которого соединен с первым входом запуска устройства, а единичный выход — с первым выходом устройства, содержит дополнительно (п"i) триггеров, {где n — общее число выходов устройства), (n-1) блоков памяти, коммутатор, элемент

ИЛИ и блок развязки, причем выходы всех блоков памятИ соединены со входами блока развязки, выходы: которо

ro подключены ко второй группе входов схемы сравнения, j-й вход запуска устройства (j=2,...,n) соединен с единичным входфм (j-1)-ого дополнительного триггера, нулевой

<вход которого соединен с выходом схемы сравнения, а единичный выходс j-м выходом устройства, каждый выход устройства соединен с входом считывания соответствующего блока памяти, с соответствующим входом элемента ИЛИ и,с соответствующим управляющим входом коммутатора, информационные входы которого соединены с входами фиксированных ча- . стот устройства, а выход - с входом счетчика, управляющий вход которого соединен с выходом элемента ИЛИ.

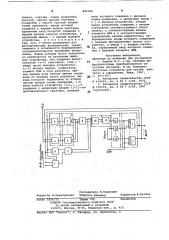

<На чертеже приведена функциональ- . на схема устройства.

Схема устройства содержит и триггеров 1, счетчик 2, например десятичный, и блоков 3 памяти, каждый иэ которых может быть выполнен в виде совокупности управляющего ключа 4 и программируемого постоянного запоминающего узла 5 (например двоично-десятичного переключателя), элемент ИЛИ 6, коммутатор 7, блок 8 развязки, схема 9 сравнения, которая может быть, например, выполнена в виде совокупности разрядных элемен20

d0

65 тов ИСКЛЮЧАЮЩЕЕ ИЛИ 10, выходы ко-. торых соединены со входом элемента

ИЛИ-HE 11 выход которого является выходом схемы 9 сравнения. Сигналы на входы триггеров 1 могут подаваться через формирователи 12, наличие которых не является принципиальным.

Устройство работает следуюцим образом.

В исходном состоянии все управляюцие триггеры 1 н разрядные триггеры счетчика 2 сброшены в "0", ключи

4 закрыты.

После запуска триггера 1, например первого на его единичном выходе и соответстнуюцем выходе устройства появляется высокий потенциал, который открывает ключ 4 первого блока 3 памяти через элемент ИЛИ 6, снимает сигнал блокировки счетчика 2 и,воздействуя на коммутатор 7, разрешает прохождение одной из фиксированных частот, обеспечивающей получение требуемого диапазона времени. Значение требуемой величины временного интервала (требуемое число накопленных импульсов) устанавливается при помоци переключателя 5, на который через соответствующие ключи 4 .подается питание.

Выходной сигнал переключателя, представленный двоичным кодом, через блок 8 развязки поразрядно поступает на вход схемы 9 сравнения таким образом, что на вход каждого из разрядных элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 10 поступают сигналы одноименных разрядов счетчика 2 и переключателя 5.

Таким образом; при достижении требуемой выдержки времени на всех выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 10 будет .присутствовать низкий потенциал, следовательно, на выходе элемента ИЛИ-НЕ 11 появится высокий потенциал, под воздействием которого первый триггер 1 будет возвращен в исходное (нулевое) состояние,. после чего нсе элементы схемы вернутся в исходное состояние. Запуск следукщего триггера 1 может осуществляться либо по команде со входа устройства, либо по окончании формирования первого временного интервала. В этом случае, формирователь 12 последующего триггера 1 подключается к нулевому выходу предыдуцего триггера. Далее укаэанный цикл .повторяется.

Использование новых элементов и нбвых структурных связей позволяет расширить функциональные возможности устройства по сравнению с известными за счет возможности формирования различных по длительности временных интервалов на различных выходах устройства.

Формула изобретения

Устройство для формирования временных интерналон, содержащее блок

822164

Составитель В.Березкин

РеДактоР М.НеДолУженко ТехРеД A.Бабинец КоРРектоР В.БУтЯга

Заказ

Тираж Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4 памяти, счетчик, схему сравнения, триггер, причем выходы счетчика соединены с первой группой входов схемы сравнения, выход которой соединен с первым входом триггера, единичный вход которого соединен с первым входом запуска устройства, а единичный выход — с первым выходом устройства, о т л и ч а ю щ е е с я тем, что, с целью расширения его функциональных воэможностей, заключающихся в возможности формйрования последовательности временных интервалов, длины которых могут значительно различаться на различных вйходах устройства, оно содержит дополнительно (n-1) триггеров, (где побщее число выходов устройства), (и-1) блоков памяти, коммутатор, элемент ИЛИ и блок развязки,.причем выходы всех блоков памяти соединены со входами блока развязки, выходы которого подключены ко второй группе входов схемы сравнения, j-й вход запуска устройства (j=2y и) соединен с единичным входом (j-1)-ого дополнительного триггера, нулевой вход которого соединен с выходом схемы сравнения, а единичный выход

c j-м выходом устройства, каждый выход устройства соединен с входом считывания соответствующего блока памяти, с соответствующим входом элемента ИЛИ и с соответствукщим управляющим входом коммутатора, информационные входы которого соединены с входами фиксированных частот устройства, а выход - с входом счетчика, управляющий вход которого соединен с выходом элемента ИЛИ.

Источники информации, принятые во внимание при экспертизе

15 1. Берлин В.Г. и др.. Типовые цифроаналоговые преобразователи ча:стотных сигналов. В с0. Комплекс частотных устройств для систем. контроля и управления. Киев, 1967, щ с. 103-107.

2 ° Авторское свидетельство СССР

Р 4 34401, кл. G 06 F 1/04, 1972.

3. Авторское свидетельство СССР . Р 230214, кл. 6 06 F 1/02, 1967 (прототип).