Преобразователь прямого двоичнодесятичного кода b дополнительныйдвоично-десятичный код

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Рееттублик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

И АВТОРСКОМУ СИИ ЕТЕЛЬСТВУ (и)8221 74 (61) Дополнительное к авт. свид-ву (22) Заявлено 06.07.79 (21) 2792652/18-24 (51)М. Кл. с присоединением заявки ¹ (23) Приоритет

С 06 F 5/02

Государстиенный комитет

СССР но делам изобретений и открытий

Опубликовано 150481 Бюллетень Н9 4

Дата опубликования описания 15. 04. 81 (53) УДК 681 З25 (088.8) (72) Автор. изобретения

A.À. Чудов (71) Заявитель (54 ) ПРЕОБРАЗОВАТЕЛЬ ПРЯМОГО ДВОИЧНО-ДЕСЯТИЧНОГО

КОДА В ДОПОЛНИТЕЛЬНЫЙ ДВОИЧНО-ДЕСЯТИЧНЫЙ

КОД

Изобретение относится к автоматике и цифровой вычислительной технике и может быть использовано в цифровых устройствах для формирования дополнений десятичных чисел.

Известен преобразователь прямого двоично-десятичного кода в дополнительный двоично-десятичный код,.содержащий десятичный сумматор блок инверторов и два корректирующих сумматора (1) .

Недоотаток этого преобразователянизкая скорость преобразования, связанная с необходимостью прибавления единицы к исходному коду с последую- 1э щим прибавлением десяти к содержимому тех тетрад, где не был выработан сигнал переноса. Кроме того, относительно велик объем аппаратуры.

Наиболее близким :;;o технической 20 сущности и схемному решению к предлагаемому является преобразователь прямого двоично-десятичного кода в дополнительный двоично-десятичный ,код, содержащий и тетрад элементов

НЕ, где и — число десятичных разрядов преобразуемого кода, входы которых являются входами преобразователя, и суммирующих блоков, каждый. из кот рых содержит первый, второй 30 и четвертый полусумматоры, элемент

ИЛИ и два элемента НЕ, информационные входы суммирующих блоков соединены с выходами элементов НЕ соответствующих тетрад, входы второго и четвертого полусумматоров каждого суммирующего. блока соединены с выходами переноса соответственно первого и третьего полусумматоров того же суммирующего блока, выходы суммы которых являются соответственно выходами первого и третьего двоичных разрядов каждого десятичного разряда преобразователя, выход суммы второго полусумматора соединен с входом первого элемента НЕ и с первым входом элемента ИЛИ того же суммирующего блока, второй вход которого соединен с выходом переноса второго полусумматора того же суммирующего блока, а выход элемента

ИЛИ соЕдинен со вторым входом третьего полусумматора того же суммирующего блока, выход суммы четвертого полусумматора соединен со входом второго элемента НЕ того же суммирующего блока (2) .

Недостаток данного преобразователя также состоит в относительно—

822174 х4х3х2 х4 x4x3xã x! P У4УЗУ y„y4 У3 У У! P У4У У У

0 0000

1 0001

2 0010

11111 1 1010

0000

0 1001

0 1000

0 0111

1 1001

1 1000

1110 °

1001

1101

1000 низком быстродействии и больших аппаратных затратах.

Цель изобретения — увеличение быстродействия преобразователя и его упрощение.

Поставленная цель достигается тем, что в преобразователь прямого двоично-десятичного кода, в дополнительный двоично-десятичный код, содержащий и тетрад элементов НЕ, где п число десятичных разрядов преобразуемого кода, входы которых являются входами преобразователя, и суммирующих блоков, каждый из которых содержит первый, второй третий и четвертый полусумматоры, элемент ИЛИ и два элемента НЕ, информационные входы суммирующих блоков соединены с выходами элементов НЕ соответствующих тетрад, входы второго и четвертого полусумматоров каждого суммирующего блока соединены с выходами переноса 29

I соответственно первого и третьего полусумматоров того же суммирующего блока, выходы суммы которых являются соответственно выходами первого и третьего двоичных разрядов каждого д десятичного разряда преобразователя, выход суммы второго полусумматора соединен с входом первого элемента НЕ и с первым входом элемента ИЛИ того же суммирующего блока, второй вход которого соединен с выходом переноса второго полусумматора того же-суммирующего блока, а выход элемента

ИЛИ соединен со вторым входом третьего полусумматора того же суммирующего блока, выход суммы четвертого полусумматора соединен со входом второго элемента HE того же суммирующего блока, дополнительно введены три группы из и элементов И, причем первый и второй входы элементов И 40 первой группы соединены соответствен— но с выходами первого элемента НЕ и выходом суммы четвертого полусумматора, соответствующего суммирующего блока, входы элементов И второй груп- 4 пы соответственно соединены с выходами суммы второго полусумматора, второго элемента НЕ соответствующего суммирующего блока, а выходы элементов И первой и второй групп являются выходами второго и четвертого двоичных разрядов соответствующего десятичного разряда преобразователя, первый и второй входы элементов И третьей группы соответственно соединены с выходами первого и второго элементов НЕ соответствующего сумми рующего блока, выход элемента И третьей группы i-ro (i=1=(n-1) десятичного разряда соединен со вторым входом первого полусумматора (i+1)-го суммирующего блока, второй вход первого полусумматора первого суммирующего блока является входом добавления единицы преобразователя.

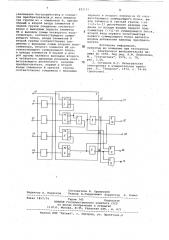

На чертеже представлена блок-схема одного десятичного разряда предлагаемого преобразователя.

Преобразователь содержит тетраду

1 элементов НЕ, суммирующий блок 2, выполненный на полусумматорах 3-6, элементе ИЛИ 7, элементы НЕ 8 и 9, а также элементы И 10, 11 и 12,вход

13 добавления единицы, выход 14 переноса в следующий старший десятичный разряд. Входы преобразователя соединены со входами тетрады 1 элементов НЕ, выходы которой подключены ко входам суммирующего блока 2 (к первым входам полусумматоров 3-6).

Второй вход полусумматора 3 соединен с входом 13 добавления единицы,вторые входы полусумматоров 4 и 6 соединены соответственно с выходами переноса полусумматоров 3 и 5, выходы которых подключены соответственно к выходам первого и третьего разряда выходного числа. Выход суммы полусумматора 4 соединен со входом элемента HE 8, с первым входом элемента

И 11 и с первым входом элемента ИЛИ

7, второй вход которого подключен к выходу переноса полусумматора 4, а выход элемента ИЛИ 7 соединен со вторым входом полусумматора 5. Выход суммы полусумматора 6 соединен со входом элемента НЕ 9 и с первым входом элемента И 10, второй вход которого объединен с первым входом элемента И 12 и подключен к выходу элемента HE 8. Выход элемента HE 9 соединен со вторыми входами элементов

И 11 и 12, выходы элементов И .10 и

11 соединены соответственно с выходами второго и четвертого разрядов выходного числа, а выход элемента И

12 подключен к выходу 14.

Преобразователь работает следующим образом.

На входы преобразователя в данном разряде поступает двоичнодесятичное число х 4 х 2 х3 х4, которое может принимать значейие от 0 до 9. На выходе тетрады элементов НЕ формируется инверсное значение двоично-десятичного числа >„х х х+. ! ! i

У4 У7 У2 У!

822174

О 0110

3 0011

4 0100

5 О1О1 б 0110

7 0111

8 1000

9 1001

11ОО

1 0111

0111

1011 1 0110

О11О

О 0101

О 0100

1010

1 0101

1. 0100

1 0011

1 001О

1 ООО1

О1О1

1001

О10О

О ОО11

ОО1О

0001 о оооо

100О

0011

0111

0110

ОО10

ООО1

Преобразователь прямого двоичнодесятичного кода в дополнительный двоично-десятичный код, содержащий и НЕ, где и число десятичных разрядов преобразуемого кода, входы которых являются входами преобразователя, и суммирующих блоков, каждый из которых содержит первый, второй, третий и четвертый полусумматоры, элемент ИЛИ

40 и два элемента НЕ, информационные входы суммирующих блоков соединены с выходами элементов НЕ соответствующих тетрад, входы второго и четвертого полусумматоров каждого суммирую 45 щего блока соединены с выходами переноса соответственно первого и третьего полусуммагоров того же суммирующего блока, выходы суммы которых яв.ляются соответственно выходами перво50 го и третьего двоичных разрядов каж,дого.десятичного разряда преобразователя, выход суммы второго полусумматора соединен с входом первого элемента НЕ и с первым входом элемента ИЛИ того же суммирующего блока, второй вход которого соединен с выходом переноса второго полусумматора того же суммирующего блока, а выход элемента ИЛИ соединен со вторым входом третьего полусуммато60 ра того же суммирующего блока, вы-,. ход суммы четвертого полусумматора соединен со входом второго элемента НЕ того же суммирующего блока, о т л и ч а ю65 шийся тем, что, с целью

В зависимости от сигнала (Р) на входе 13 добавления единицы с помощью суммирующего блока 2 осуществляется суммирование инверсного значения двоично-десятичного числа

x4х>х2х„либо с числом 1011 (11), либо с числом 1010 (10).

В первом разряде (i=1) многоразрядного двоично-десятичного числа, а также в любом -ом разряде, если в предыдущих младших разрядах двоично-десятичного числа содержатся только нули, на входе 13 добавле ния единицы должен быть сигнал логической единицы. В этом случае к инверсному значению входного числа прибавляется число 1011.

Если входное число в данном разряде равно 0000 (О) и во всех младших разрядах входные числа равны О, то при суммировании инверсного значения 1111 с числом 1011 на выходе суммирующего блока 2 формируется число у у у у,, равное 1010. Однако в этом случае должно формироваться выходное число ус1у у у„, равное 0000, поэтому на выходах второго и четвертого разрядов суммирующего блока 2 введены элементы И 10 и 11, которые позволяют исключить формирование логических единиц во втором и четвертом разрядах при одновременном присутствии логических единиц в этих разрядах на выходах элементов HE 8 и 9.Одновременное формирование логи-, ческих единиц на выходе сумматора 2 кодов во втором и четвертом разрядах. означает, что в данном i îì разряде и во всех младших разрядах входные числа равны О одновременно. В этом случае на выходе 14 с помощью элемента И 12 формируется сигнал логической единицы, который поступает на вход добавления единицы аналогичной схемы в i+1 разряд двоичнодесятичного числа (не показан).

Если хотя бы в одном младшем разряде число не равно нулю, то на входе 13 преобразователя имеется сигнал логического нуля, и к инверсному коду входного числа в данном разряде прибавляется число 1010. ь этом случае на выходе 14 всегда формируется сигнал логического нуля,.

Таким образом, предлагаемый преобразователь позволяет совместить во времени операции добавления единицы и коррекции (добавления числа

10), что практически вдвое позволяет повысить скорость преобразования.

Предлагаемый преобразователь позволяет упростить конструкцию известных преобразователей за счет упрощения десятичного сумматора, устранения одного из корректирующих

25 сумматорОв и за счет управления преобразовалетем.

Формула изобретения

82717л

Составитель М. Аршаэский

Редактор A. Наурсков Техред Е.Гаврилешко Корректор Е. Рошко

Тираж 745 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, .Раушская наб., д . 4/5

Заказ l857/74

Филиал ППП "Патент", г. Ужгород, ул. Проектная,4 увеличения быстродействия и упрощения преобразователя,в него введены три группы из и элементов И, причем первый и второй входы элементов И первой группы соединены соответственно с выходами первого элемента

НЕ и выходом суммы четвертого полусумматора, соответствующего суммирующего блока, входы элементов И второй группы соответственно соединены с выходами суммы второго полусумматора, второго элемента HE соответствующего суммирующего блока, а выходы элементов И первой и второй группы являются выходами второго и четвертого двоичных разрядоэ соответствующего десятичного разряда 15 преобразователя, первый и второй входы элементов И третьей группы соответственно соединены с выходами первого и второго элемен-.ов НЕ соответствующего суммирующего блока, выход элемента И третьей группы I-го (i=1=(n-1) десятичного разряда сое-динен со вторым входом первого полусумматора (i+1)-го суммирующего блока, второй вход первого полусумматора первого суммирующего блока является входом добавления единицы преобразователя.

Источники информации, принятые во внимание при экспертизе

1. Электронная вычислительная машина ЕС 1050. Под ред. A.M. Ларионова, M. "Статистика", 1976, с. 78, рис. 3.16.

2. Гутников В.С. Интегральная электроника в измерительных приборах. Л., "Энергия", 1974, с. 59-60 (прототип).