Устройство для сравнения двоичныхчисел

Иллюстрации

Показать всеРеферат

Сентз Советских

Соцналнстнческнк

Республнк

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ИТИЛЬСТВУ ()822178 (61) Дополнительное к авт. свид-ву (51)М. Кл. (22) Заявлено 04.0б.79 (2l) 2773838/18-24 с присоединением заявки М

G F 7/04

Государствеииый комитет

СССР по делам изобретеиий и открытий (23) Приоритет

Опубликовано 150481. Бюллетень Но 14

Дата опубликования описания 15 . 04. 81 (53) УДК б81.325.5 (088 ° 8) (72) Автор изобретеиия

Г.П. Апарин

L

;Г

Институт технической кибернетики AH Белорусской " (. Н - -"." : (71) Заявитель (54) УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ

Изобретение относится к автоматике и вычислительной технике и может быть использовано при реализации технических средств дискретной автоматики и вычислительных машин.

Известно устройство для сравнения двоичных чисел, содержащее регистры сравниваемых чисел, элементы И, ИЛИ, НЕ, причем в каждом разряде устройства прямые выходы соответствующих разрядов первого и второго -регистров сравниваемых чисел соединены с первыми входами соответственно первого и второго разрядных элементов И, вторые входы которых подключены к инверсным выходам тех же разрядов соответственно второго и первого регистров сравниваемых чисел, выходы первого и второго разрядных элементов И 2О каждого разряда подключены ко входам установки единицы младшего разряда соответственно первого и второго регистров сравниваемых чисел и ко входам установки нуля младшего разряда соответственно второго и первого регистров сравниваемых чисел, кроме того, выходы разрядных элементов И подключены ко входам элементов ИЛИ, выходы которых через элементы НЕ подключены ко входам оконечного элемента И (1g .

Недостатком этого устройства является его сложность.

Наиболее близким к предлагаемому является устройство, содержащее два и-разрядных регистра на триггерах, и поразрядных узлов сравнения и элемент ИЛИ-НЕ, причем прямой и инверсный выкоды триггера каждого

i-го разряда первого регистра, где i = 1,2,...,п соединены с первым и вторым входами i-го поразрядного узла срав 4ния соответственно, прямой и.инверсный выходы каждого

i-го триггера второго регистра под- ключены к третьему и четвертому входам i-ro поразрядного узла сравнения соответственно, пятые входы всех поразрядных узлов сравнения соединены с шиной синхронизации, а информационные входы регистров подключены к шинам сравниваемых чисел, первый выход каждого J-ro поразрядного узла сравнения, где J 1,2, ...,(n ) соединен со входом установки в единичное состояние триггера ()+1)-ro разряда первого регистра и со входом установки в нулевое состояние триггера ()+1)-ro

822178 разряда второго регистра,„ второй выход каждого j-ro поразрядного узла сравнения подключен ко входу установки в нулевое состояние триггера (j+1)-ãî разряда первого регистра и ко входу установки в единич1 ное состояние триггера.(j+1)-го раз ряда второго регистра, выходы n-ro поразрядного узла сравнения соединены со входами элемента ИЛИ-НЕ 2

I Недостатком указанного устройства также является его сложность.Когда одно из сравниваемых чисел задается в виде числоимпульсной последовательности, то указанная реализация не является оптимальной по стоимости.

Цель изобретения — упрощение устройства.

Поставленная цель достигается тем, что в устройстве для сравнения двоичных чисел, содержащем и-разрядный счетчик, установочные входы которого соединены с шинами первого сравниваемого числа, триггеры, элементы И, ИЛИ, элемент задержки, выход переполнения и-разрядного счетчика через элемент задержки подключен ко входу установки в единичное состояние первого триггера, прямой выход которого соединен с первыми входами первого и второго элементов

И, выход первого элемента И подключен ко входу установки в единичное состояние второго триггера, инверсный выход которого соединен со вторым входом второго элемента И и с первым входом третьего элемента И, второй вход которого подключен к инверсному выходу первого триггера, входная шина второго сравниваемого числа устройства соединена с первым входом элемента ИЛИ, второй вход которого подключен к шине управления устройства, а выход элемента

ИЛИ соединен с информационным входом счетчика и со вторым входом первого элемента И, входы установки в нулевое состояние триггеров подключены к шине сброса.

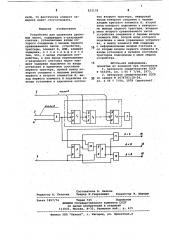

Йа чертеже представлена блок-схема устройства.

Устройство содержит и-разрядный счетчик 1, шину 2 первого сравниваемого числа, шину 3 второго сравниваемого числа, шину 4 управления, шину

5 сброса, элемент ИЛИ б, элемент 7 задержки,. триггеры 8 и 9, элементы

И 10-12, выходные шины 13-15.

Устройство работает следующим .образом.

Перед началом сравнения по шине

5 поступает сигнал сброса и устанавливает триггеры 8 и 9 в нулевое состояние. Первое сравниваемое число подается по шине 2 таким образом, чтобы в и-разрядном счетчике 1 установилось его инверсное значение.

После этого по шине 3 через элемент

<о

ЬО

ИЛИ 6 на информационный вход младtuего разряда счетчика 1 поступает второе число в виде числоимпульсной последовательности. Когда второе число передано, по шине 4 управления поступает сигнал и, спустя время переходных процессов, на одной иэ выходных шин 13-15 сформировывается результат сравнения в виде единичного сигнала. На выходных шинах 13-.15 результат сравнения сохраняется до поступления сигнала сброса по шине 5.

Пусть А = Б = 101, тогда в счетчике 1 число А устанавливается в . виде инверсного кода 010. После приема на счетный вход младшего разряда числоимпульсной последовательности из 101 импульса в счетчике 1 происходит суммирование 010 + 101

111. После поступления по шине 4 управления сигнала в счетчик 1 добавляется еще единица и на выходе старшего разряда сформировывается сигнал переполнения, который после задержки на элементе 7 устанавливает в единичное состояние триггер 8 сразу после прекращения сигнала на выходе элемента ИЛИ б. Единичное состояние триггера 8 и нулевое триггера 9 обеспечивают формирование единичного сигнала с помощью элемента И 11 на выходной шине 14 (А Б)при нулевых сигналах на двух других шинах 13 и 15.

Пусть А с Б для определенности

А 101 и Б = 110. Б счетчике 1 устанавливается код 010, а после приема на счетный вход 110 устанавливается в единичное состояние триггер

8. После поступления по шине 4 сигнала фиксации на выходе элемента

И 10 формируется единичный сигнал и триггер 9 устанавливается в единичное состояние, тем самым определяя единичный сигнал на выходной шине 13 и нулевые — на выходных шинах 14 и 15.

Пусть А > Б для определенности

A = --101 и Б = 100. После приема числа в счетчике 1 устанавливается инверсное значение 010, а после приема на счетный вход 100 импульсов получается сумма 010 + 100 = 110.

После поступления по шине 4 сигнала фиксации полученная сумма увеличивается на единицу: 110 + 001 = 111 °

Так как сигнал переполнения в этом случае не появляется, то триггеры, 8 и 9 остаются в нулевом состоянии.

На выходной шине 15 с помощью элемента И 12 формируется единичный сигнал A > Б при нулевых сигналах на двух других выходных шинах 13, 14.

Устройство для сравнения двоичных чисел может иметь более простую модификацию. Когда выдерживаются . необходимые временные соотношения и время задержки может быть равным

822178 нулю, то фактически элемент задержки может отсутствовать.

Формула изобретения

ЧисЛа 4

Составитель В. Белкин

Редактор М. Петрова Техред Е.Гаврилешко Корректор М. Шароши

Заказ 1857/74 Тираж 745 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r . Ужгород, ул. Проектная,4

Устройство для сравнения двоичных чисел, содержащее и-разрядный счетчик, установочные входы которого соединены с шинами первого сравниваемого числа устройства,. триггеры, элемент И, ИЛИ, элемент задержки, о т л и ч а ю щ е е с я тем, что, с целью упрощения устройства, в нем выход переполнения в"разрядного счетчика через элемент задержки подключен ко входу установки в единичное состояние .первого триггера, прямой выход ко торого соединен с первыми входами первого и второго элементов И, выход первого элемента И подключен ко входу установки в единичное состояние второго триггера, инверсный выход которого соединен с первым входом третьего элемента И, второй вход которого подключен к инверсному выходу первого триггера, входная шина второго сравниваемого числа устройства соединена с первым входом элемента ИЛИ, второй вход которого подключен.к шине управления устройства, а выход элемента ИЛИ соединен с информационным входом счетчика и со вторым входом первого элемента И, входы установки в нулевое состояние .триггеров подключены к шине сброса устройства.

15 Иаточьики информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 565296, кл. G 06 F 7/04, 1973.

2. Авторское свидетельство СССР .

gp по заявке М 2674783/18-24, кл. G 06 F 7/04, 1978 (прототип). !