Устройство для поиска чисел в заданномдиапазоне

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДВТИЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 09.07.79 (21) 2794004/19-24 5 ) Союз Советских

Социалистических

Республик с присоединением заявкн йо (23) Приоритет

G 06 E 7/06

Государственный комитет

СССР по делам изобретении н открытий

Опубликовано, 150481. Бюллетень Н9 14

Дата опубликования описания 15. 04. 81 (53) УДК 681 325.5 (088.8) (72) Автор изобретения

Н.Р, Иванов (7! ) Заявитель (54) устРОЙсТВО длп пОискА чисел В 3АдАннОм

ДИАПАЗОНЕ

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах обработки цифровой информации.

Известно устройство для сортировки данных, содержащее ассоциативный запоминающий блок, блок управления, буферный запоминающий блок, ключевые схемы и блок записи (1) .

Недостатком этого устронства является его сложность.

Наиболее близким по техническому решению к предлагаемому является устройство для поиска чисел в заданном диапазоне, содержащее регистры чисел, выходы которых соединены с первыми входами блоков сравнения, вторые входы которых соединены с входом устройства, триггеры и регистр значений границ диапазона (21 . 2O

Недостатком данного устройства является низкое быстродействие.

Целью изобретения является повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройство для поиска чисел в заданном диапазоне, содержащее регистры, генератор тактовых сигналов, формирователи тактовых сигналов, элементы И, ИЛИ, НЕ, трнггеры и дешифратор, введены сумматор и сдвигающий регистр, причем входная информационная шина и шина задания центра диапазона соединены с информационными входами первого и второго регистров соответственно, выход-первого регистра через первый элемент НЕ подключен к первому входу сумматора, второй вход которого соединен с выходом второго регистра, пЕрвый выход сумматора соединен с первым входом первого элемента И и через второй элемент

НŠ— с первым входом второго элемента И, выходы первого и второго элементов И подключены ко входам установки в единичное состояние первого и второго триггеров соответственно, шина начального пуска устройства соединена со входами установки в нулевое состояние триггеров и со входом управления генератора тактовых сигналов, выход которого подключен ко входам управления первого и второго регистров, ко входам формирователей тактовых сигналов и ко входу управления сдвигающего регистра, выход первого формирователя тактовых сигналов соединен со вторыми входами первого

822179!

20 и и второго элементов И, выход переносов сумматора подключен к информа ционному входу сдвигающего регистра, выход которого подключен ко входу переносов сумматора, а выходы старших разрядов первого и второго регистров соединены с информационны ми входами дешифратора, выход переносов сумматора соединен с первым входом третьего элемента И, второй вход которого подключен к выходу второго формирователя тактовых сигналов, выход третьего элемента И соединен со входом установки в единичное состояние третьего триггера, выход которого подключен ко входу управления дешифратора, первый и второй выходы которого соединены с первыми входами четвертого и пятого элементов И, вторые входы которых подключены к выходам первого и второго триггеров соответственно, третьи входы четвертого и пятого элементов

И соединены с выходом третьего формирователя тактовых сигналов, выходы четвертого и пятого элементов И подключены ко входам элемента ИЛИ, выход которого подключен к выходу устройства.

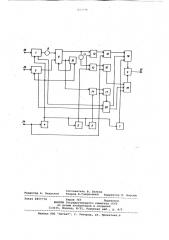

На чертеже представлена блок схема устройства.

Устройство содержит регистры 1 и 2, элемент ИЛИ 3, генератор 4 тактовых сигналов, формирователи 5,6 и 7 тактовых сигналов, элемент НЕ 8, сумматор 9, сдвигающий регистр 10, элемент НЕ 11, элементы И 12, 13 и

14, триггеры 15, 16 и 17, элементы

И 18 и 19, дешифратор 20, выходную шину 21 устройства, входную информационную шину 22, шины задания диапазона 23 и начального пуска 24 устройства.

Устройство работает следующим образом.

В регистр 1 вводится число, характеризующее центр диапазона, в котором необходимо произвести поиск и найти число, принадлежащее указанному диапазону.

В регистр 2 вводятся поочередно числа, подлежащие анализу. В регистры 1 и 2 вводятся также знаки чисел. При этом, если в разряде знака записана единица ("1"), то это значит, что число принадлежит положительной полуоси. В этом случае код числа прямой. Если в разряде знака. записан ноль ("0"), то это значит, что число принадлежит отрицательной полуоси,и код числа обратный.

По окончании ввода в регистр 2 каждого очередного числа на вход

"Пуск" устройства подается пусковой импульс. Этот импульс устанавливает в исходное положение триггеры 15,16 и 17 и запускает генератор 4 тактовых. сигналов, форми5 !

О

65 рующий серию тактовых импульсов.

Число тактовых импульсов в серии на единицу превышает количество разрядов двоичных чисел. При появлении тактовых импульсов с регистров 1 и 2 на одноразрядный сумматор 9 начинает поступать информация — последовательные двоичные коды чисел, начиная с младших разрядов. С каждым очередным тактом суммируется очередной разряд числа. Для обеспечения процесса суммирования выход переноса одноразрядного сумматора 9 подключен.ко входу этого сумматора через одноразрядный сдвигающий регистр 10, осуществляющий задержку импульсов переноса на один такт на один разряд. На вход тактов сдвигающего регистра 10 поступают тактовые импульсы с выхода генератора

4 тактовых сигналов. Последовательный код с выхода суммы сумматора

9 представляет собой число, которое с точностью до единицы равно разности чисел. Это число может быть представлено либо в прямом, либо в обратном коде. Кроме того, оно может быть на единицу меньше разности или равно разности. Судить об этом можно лишь по окончании процесса суммирования всех разрядов, когда станет известно, существует ли в самом старшем разряде единица переноса при суммировании.

Значения чисел, снимаемых с выхода суммы сумматора 9, зависит от знаков суммируемых чисел и наличия или отсутствия единицы переноса.в старшем разряде. Для получения разности чисел достаточно проанализировать знаки кодов и наличие единицы переноса в старшем рязраде и использовать либо прямой,. либо инверсный код с выхода суммы сумматора 9. Этот анализ производится с BoMol jbfo дешифратора 20.

Знаки чисел снимаются с регистров

1 и 2 в виде потенциалов с соответствующих разрядов регистров. Для

"запоминания" единицы переноса в старшем разряде используется триггер 17, на вход которого в моменты такта старшего разряда через .элемент И 14 подается сигнал е выхода переноса сумматора 9. С триггера

17 сигнал наличия единицы переноса в старшем разряде снимается на соответствующий вход дешифратора 20.

Число считается принадлежащим к диапазону, центр которого задан соответствующей координатой маркера, если в старших разрядах кода разности нет ни одной единицы.

Изменяя количество анализируемых старших разрядов, можно ступеньчато изменять величину исследуемого диапазона. Например, уменьшение количества анализируемых старших разрядов на "1" вызовет увеличе822179 ние исследуемого диапазона в два раза. Большей точности для решения поставленной задачи и не требуется.

Наличие единиц в старших разрядах кода разности проверяется на элементах И 12 и 13, один из входов каждого из которых подключен к выходу формирователя 5 тактовых сигналов. Поскольку до конца суммирования неизвестно в каком коде (прямом или обратном) будет разность, анализируются оба варианта — прямой и обратный. На элемент И 12 с выхОда суммы сумматора подается прямой код, а на элемент И 13, через элемент

HE 11 — обратный код. При наличии в старших разрядах разности хотя бы 15 одной единицы сработает триггер 15, либо триггер 16. По окончании суммирования дешифратор 20 знака выдает на элементы И 18 и 19 команду, определяющую с какого триггера дол- Щ жен сниматься результат анализа.

По такту считывания, которые следует сразу же за тактом старшего разряда, с выхода одного из элементов

И 18 или 19 результат анализа через элемент ИЛИ 23 поступает на выход

21 устройства.

Технико-экономические преимущества предлагаемого устройства по сравнению с известным проявляются в повышении быстродействия устройства.

Формула изобретения

Устройство для поиска чисел в 35 заданном диапазоне, содержащее регистры, генератор тактовых сигналов, формирователи тактовых сигналов,элементы И, ИЛИ, НЕ, триггеры и дешифратор, о т л и ч а ю щ е е с я тем, 4О что, с целью повышения быстродействия, в него введены сумматор и сдвигающий регистр, причем входная информационная шина и шина задания центра диапазона соединены с информационными входами первого и второго регистров соответственно, выход первого регистра через первый элемент НЕ подключен к первому входу сумматора, второй вход которого соединен с выходом второго регистра, первый выход сумматора соединен с первым входом первого элемента И и через второй элемент НŠ— c первым входом второго элемента И, выходы первого и второго элементов И подключены ко входам установки в единичное состояние первого и второго триггеров соответственно, шина начального пуска устройства соединена со входами установки в нулевое состояние триггеров и со входом управления генератора тактовых сигналов, выход которого подключен ко входам управления первого и второго регистров, ко входам формирователей тактовых сигналов и ко входу управления сдвигающего регистра, выход первого формирователя тактовых сигналов соединен со вторыми входами первого и второго элементов И, выход переносов сумматора подключен к информационному входу сдвигающего регистра, выход которого подключен ко входу переносов сумматора, а выходы старших разрядов первого и второго регистров соединены с информационными входами дешифратора, выход переносов сумматора соединен с первым входом третьего элемента И, второй вход которого подключен к выходу второго формирователя тактовых сигналов, выход третьего элемента И соединен сЬ входом установки в единичное состояние третьего триггера, выход

Ъ которого подключен ко входу управления дешифратора, первый и второй выходы которого соединены с первыми входами четвертого и пятого элементов И, вторые входы которых подключены к выходам первого и второго триггеров соответственно, третьи входы четвертого и пятого элементов

И соединены с выходом третьего формирователя тактовых сигналов, выходы четвертого и пятого элементов И подключены ко входам элемента ИЛИ, выход которого подключен к выходу устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 486316, кл. G 06 F 7/06, 1973.

2. Авторское свидетельство СССР

9 486317, кл. G 06 F 7/06, 1973 (прототип).

Тираж .745 Подписное

ВНИИПИ Государственного коМитета СССР по делам изобретений и открытий

113035, Москва, Ж 35, Раушская наб., д. 4/5

Заказ 1857/74

Филиал ППП "Патент", r. Ужгород, ул . Проектная,4

Составитель В. Белкин

Редактор A. Наурсков Техред Е.Гаврилешко Корректор М. Шароши