Устройство для умножения чиселв дополнительных кодах

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ (1822181 (61) ДОПОЛНИтЕЛЬИОЕ К аВт. Саид-Ву (22) Заявлено 21. 08. 78 (21) 2660932/18-24 (51) М. Кл.з с присоединением заявки ¹

G F 7/52

Государствеииый комитет

СССР по делан изобретений и открытий (23) Приоритет

Опубликовано 150481, Бюллетень МЯ 14

Дата опубликования описания 15 . 04 . 81 (53) УДК 681. 325 (088.8) (72) Авторы изобретения

Ю.Я. Ледянкин и Б.Н. Малиновский

Ордена Ленина институт кибернетики

AH Украинской ССР

ИБ Щу„.-.((А (71) Заявитель (54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ

В ДОПОЛНИТЕЛЬНЫХ КОДАХ

Изобретение относится к вычислительной технике и может быть исполь- зовано в арифметических устройствах специальных цифровых .вычислительных машин.

Известно устройство последовательного типа для,умножения двоичных чисел, содержащее регистр множкмого, множителя и частичного произведения, элементы И и инвертор. 3То устройство позволяет выполнять умножение двоичных чисел в дополнительных кодах.

Недостатком такого устройства является невысокое быстродействие., связанное с необходимостью выполнения корректирующих циклов суммирования для учета умножения множимого на знак множителя. Особенно значительно происходит понижение быстродействия при небольшой разрядности мно5кителя °

Наиболее близким к предлагаемому по техническому решению является устройство последовательного типа для умножения двоичных чисел, содержащее регистр множимого, регистр множителя, регистр результата, узел суммирования, элемент И, причем входы регистров.множимого и множителя соединены с входными шинами множи- 30

2 мого и множителя устройства соответственно а выходы с первым и вторым входами элемента И, выход регистра множимого соединен также со входом этого регистра, выход элемента И соединен с первым входом узла суммирования, выход узла суммирования соединен со входом регистра результата, выход регистра результата соединен со вторым входом узла суммирования и с выходной шиной результата устройства. Данное устройство позво.ляет выполнять умножение двоичных чисел как в прямых, так и в дополнительных кодах без специальной коррекции результата за счет расширения разрядной сетки сомножителей.

Недостатком известного устройства является также невысокое быстродействие при выполнении умножения двоичных чисел в дополнительных кодах, связанное с расширением разрядной сетки сомножителей, которое увеличивает общее число циклов суммирования.

Цель изобретения — увеличение быстродействия устройства.

Для достижения поставленной цели в устройство для умножения чисел в дополнительных кодах, содержащее

822181 регистр множимого, регистр множителя, регистр результата, узел суммирования, элемент И, причем входы регистров множимого и множителя соединены со входными шинами множимого и множителя устройства. соответственно, выход регистра множимого соединен со входом

:этого регистра, выход элемента И соединен с первым входом узла суммирования, выход регистра результата соединен с выходной шиной результата устройства, введены триггер знака, триггер модификации сдвига, преобразователь кода множителя в дополнительный код, входной и выходной коммутаторы, причем выход регистра множимого соединен с информационным вхо- 15 дом,триггера модификации сдвига, управляющий вход этого триггера соединен с первым управляющим входом устройства, выход регистра множителя соединен с информационным входом пре- Щ образователя кода множителя в дополнительный код, выход знакового разряда регистра множителя соединен с информационным входом триггера знака, управляющий вход которого соединен со вторым управляющим входом устройства, выходы триггера модификации сдвига и преобразователя кода множителя в дополнительный код соединены с первым и вторым входами элемента И соответственно, прямой выход триггера знака соединен с первыми управляющими входами входного и выходного коммутаторов и с управляющим входом преобразователя кода множителя ительный zo, инверсный триггера знака соединен со вторыми управляющими входами входного и выходного коммутаторов, прямой и инверсный информационные входы входного коммутатора соединены с выходом ре- 40 гистра результата, а выход этого коммутатора — co вторым входом узла суммирования, прямой и инверсный информационные входы выходного коммутатора соединены с выходом узла сумми- 45 рования, а выход — co входом регистра результата.

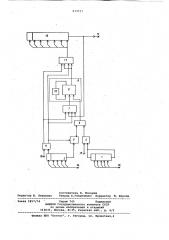

Схема устройства представлена на чертеже.

Устройство содержит регистр 1 мно- 5р жимого,регистр 2 множителя, триггер 3 модификации сдвига, триггер 4 зна ка, преобразователь 5 кода множителя в дополнительный код, элемент И б, входной коммутатор 7, узел 8 суммирования, содержащий одноразрядный сумматор 9 и элемент 10 задержки, выходной коммутатор 11, регистр 12 результата, входные шины 13 и 14 множимого и множителя, первый и второй управляющие входы 15 и 1б устройства 4р выходную шину 17 результата.

При работе устройства в регистры множимого 1 и множителя 2 по входным шинам записываются коды сомножителей.

В зависимости от знака кода множителя g5

= 0,01110

1) О,ООООООмножитель;

2) 0,000000 множитель;

1,111111

1 1010

z, so otuâ€

0i011000 (+ — ).

30 б4 ч.п. 0,101 т.к.ч.п. 0,101 о.к.ч.п. множимое о.к.ч.п. п.к.ч.п. в регистре 2 триггер 4 знака множителя устанавливается в единичное или нулевое состояние. Если знак множителя положительный, то прохождение кода множителя через преобразователь 5 кода осуществляется без преобразования, т.е. в коде представления (прямом); если же знак отрица тельный — берется дополнительный код от дополнительного кода отрицательного числа, т.е. множитель преобразуется в абсолютную величину. Таким образом, код множителя всегда делается положительным. Триггер 4 зиака своими выходами управляет входным и .выходным коммутаторами так, что информация подается с выхода регистра,12 на вход узла 8 суммирования через входной коммутатор, и с выхода узла 8 суммирования на вход регистра 12 результата (через выходной коммутатор 11) в прямом коде, если знак множителя положительный, или в обратном, если знак отрицательный. В то же время множимое всегда поступает в узел

8 суммирования непосредственно в коде представления без преобразований. После передачи знакового разряда множимого на выход регистра

1 он будет зафиксирован триггером

3 модификации сдвига, который в течение последующих микротактов не будет сбрасываться, и в узел 8 суммирования, в соответствии с правилом модифицированного сдвига числа будет подаваться код знакового разряда множимого.

Знак множителя определяет необходимые сложения или вычитания промежуточного результата (частичного произведения) с кодом множимого.

При этом реализуется алгоритм вычитания чисел, представленных дополнительным кодом, в соответствии с которым необходимо проинвертировать код уменьшаемого (B данном случае код результата), сложить его с кодом вычитаемого (в данном случае с кодом множимогО),а полученный псевдорезультат операции сложения вновь проинвертировать, после чего на выходе (после выходного коммутатора) получается разность исходных чисел.

Приме р. (- — ) x (- — ) = 1 010 х 1,011 = б 5

8 8

822181

3) 0,011000 п.к.ч.п. 0,101 множитель

4) 0,011000 — т.к.ч.п. 0,101 множитель

1,100111 — о.к.п.ч., 1,111010 — множимое

1,100001 — псевдорезультат.

1,011110 — результат = (+ — 4)

64 где ч.п. — частичное произведение; о.к. — обратный код; п.к. — прямой код.

В приведенном примере реализуется умножение, начиная со старших разрядов множителя со сдвигом множимого вправо и с неподвижным частичным произведением. Возможна реализация умножения, начиная с младших разрядов множителя.

Таким образом, устройство позволяет выполнять операцию умножения двоичных чисел в дополнительных кодах без коррекции с интерпретацией знаковых разрядов как числовых.

Введение двух дополнительных триггеров, преобразователя кода множителя и двух коммутаторов позволяет вдвое сократить число циклов суммирования, при выполнении операций умножения чисел в дополнительных кодах без коррекции, так как отпадает необходимость расширения разрядной сетки сомножителей.

Это приводит к увеличению быстродействия предлагаемого устройства в 1,7-1,8 раз по сравнению с известным. Предлагаемое устройство позволяет также совместить устройство для сложения (вычитания) чисел в дополнительных кодах с устройством умножения (деления) аналогичных чисел.

Формула изобретения

Устройство для умножения чисел в дополнительных кодах, содержащее регистр множимого, регистр множителя, регистр результата, узел суммирования, элемент И, причем входы регистров множимого и множителя соединены со входными шинами множимого и множителя устройства соответственно, выход регистра множимого соединен со входом этого регистра, выход элемента И соединен с первым входом узла суье ирования, выход регистра резуль- . тата соединен с выходной шиной результата устройства, о т л и ч а ю щ ее с я тем, что, с целью увеличения быстродействия, в устройство введены триггер знака, триггер модификации сдвига, преобразователь кода множителя в дополнительный код, входной и выходной коммутаторы, причем выход регистра множимого соединен с информационным входом триггера модификации сдвига, управляющий вход этого триггера соединен с первым управ20. ляющим входом устройства, выход регистра множителя соединен с информационным входом преобразователя кода множителя в дополнительный код, выход знакового разряда регистра множителя соединен с информационным входом триггера знака, управляющий вход которого соединен со вторым управляющим входом устройства, выходы триггера модификации сдвига и преобразователя кода множителя в дополнительный- код соединены с первым и вторым входами элемента И соответственно, прямой выход триггера знака соединен с первыми управляющими входами входного и выходного коммутатора и с управляющим входом преобразователя кода множителя в дополнительный код, инверсный выход триггера знака соединен со вторыми управляющими входами входного и

40 выходного коммутаторов, прямой и инверсный информационные входы входного коммутатора соединены с выходом регистра результата, а выход этого коммутатора — co вторым входом

45 узла суммирования, прямой и инверсный информационные входы выходного коммутатора соединены с выходом узла суммирования, а выход — со входом . регистра результата

Составитель Н. Мосарев

Редактор Ю. Петрушко Техред Е. Гаврилешко Корректор М. Шароши

«f

Заказ 1957/74 Тираж 745 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная,4