Устройство для интегрирования

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (ii) 822194 (61) Дополнительное к авт. свид-ву (22) Заявлено 02,0279 (21) 2720611/18-24 с присоединением заявки ¹ (23) Приоритет

Опубликовано 150481 Бюллетень ¹ 14

Р11М. Кл.

G F 15/32

G 06 J 3/00

Государствеииый комитет

СССР ио делам мзобретеиий и открытий (53) УДК 681. 323, . 057 (088. 8) Дата опубликования описания 150481

«Пухов, Г. Я, Вереговенко и В.B.(Фф офрв. с

/ в ц* I

Институт электродинамики АН Украинской С (72) Авторы изобретения (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ИНТЕГРИРОВАНИЯ

Изобретение относится к области вычислительной техники и может быть использовано при построении специализированных вычислителей для решения различных задач, связанных с решением обыкновенных дифференциальных уравнений с начальными условиями.

Известен интегратор (11, содержащий усилитель постоянного тока, резисторы, переключающие элементы и конденсаторы. Данный интегратор выполнен на аналоговых элементах и точность его ограничена.

Из известных устройств наиболее близким по технической сущности к изобретению является интегратор (2j который состоит из двух блоков комбинационных сумматоров, матрицы комбинационных умножителей и матрицы комбинационных функциональных преобразователей, горизонтальные шины матрицы комбинационных умножителей соединены соответственно с входами-интегратора и входами первого блока комбинационных сумматОров, аналогичные шины комбинационных функциональных преобразователей соответственно соединены с, входами интегратора и с входами второго блока комбинационных сумматоров, вертикальные шины обеих матриц соединены с выходами интегратора.

Это устройство предназначено для интегрирования решетчатых функций с учетом граничных условий, Процесс решения задачи на таком устройстве неизбежно происходит по итерациям„ . органиэацию которых одним из методов осуществляет блок управления.

К недостаткам данного устройства для интегрирования следует. отнести сравнительйо невысокое быстродействие из-за итераций и низкую точность получаемого результата.

15 Целью изобретения является повышение быстродействия и точности устройства.

Поставленная цель достигается тем, что в устройство для .интегри20 рования, содержащее блок суммирования и блок умножения значений функции на коэффициенты матриц, входы первой группы которых соединены соответственно с информационными входами устройства, введен блок умножения значений интегральной функции в точках на табличные коэффициенты, входы которого соединены соответственно с входами задания интерполя30 ционных коэффициентов, задания пред822194 шествующих значений интегрируемой функции и входом задания величины шага интегрирования устройства, а выходы подключены соответственно к входам второй группы блока суммирования, выходы которого являются выходами устройства, входы третьей группы блока суммирования соединены соответственно с выходами блока умножения значений функции на коэффициенты матриц, входы второй группы которого подключены соответственно к входам коэффициентов устройства, вход начальных значений интеграла и вход задания величины шага интегрирования устройства подключены к соответствующим входам блока суммирования.

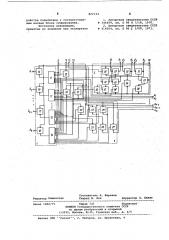

Схема устройства для случая кубической интерполяции представлена

»а чертеже, где обозначено: блок 1 суммирования, блок 2 умножения зна- 20 чений функции на коэффициенты матриц, блок 3 умножения значений интегральной функции в точках на табличные коэффициенты, входы 4 — 4 и значений интегральной функиии устройства, выходы 5. — 5 устройства, вход 6 начальных значений интеграла устройства, входы 7. — 7 коэффициентов, входы 8 — 8 задания предшествующих значений интегральной

Функции, входы 9 - 92 задания интерполяционных коэффициентов, вход 10 задания величины шага интегрирования, сумматоры 11-14, умножители 15-39.

Блок 1 состоит из сумматоров 1114, способных осуществлять алгебраическое суммирование (число сумматоров равно числу входов в устройство).

Число входов у каждого сумматора увеличивается на единицу с ростом его номера. результат каждого сум- 40 мирования до выхода из устройства умножается на величину шага интегрирования, так что блок 1 суммирования содержит и умножители

15-18. 45

Блок 2 содержит умножители, сгруппированные в строки, число умножителей в строке не больше степени выбранщ>го интерполяционного полинома.Блок 2 предназначен для образования произведений значений входной функции на отличные от единицы коэффициенты матриц. Значения этих коэффициентов в каждой строке повторяются.

Устройство работает следующим образом.

В зависимости от необходимой точности выбирают удовлетворяющую степень интерполяционного полинома К..

Предварительно рассчитанные по формулам Грегори значения коэффициентов задают через входы 7 — 7 в блок 2 умножения. В блок 3 на входы 9 — 93 задают известные коэф1 фициенты из таблиц. Подавая на вход

6 начальное значение интеграла, на входы 8 — 8 заданные значения интегрируемой функции в точках, предшествующих интервалу интегрирования, на вход 10 значение величины шага

15 интегрирования и на входы 4 4 — 4 и значения интегрируемой функции, на выходах 5 — 5 получают значения интеграла от входной функции.

Формула изобретения

Блок 3 представляет собой набор умножителей„ на которых в блоке суммирования формируются выражения как произведения. некоторого числа заданных предшествующих значений интегрируемой функции (число это равно степени интерполяционного полинома) на сомножители в виде различных степеней значений шага интегрирования.

Данное устройство в отличие от известного интегратора дает возможность обеспечить любую наперед заданную точность интегрирования как предварительным выбором степени интерполяционного полинома, так и выбором шага интегрирования.

Кроме того, значения интеграла в каждой точке вычисляются без итераций параллельно, т.е. значение интеграла от входной функции определяется за один такт, равный времени вычисления интеграла в последней точке.

Устройство для интегрирования, содержащее блок суммирования и блок умножения значений функции на коэффициенты матриц, входы первой группы которых соединены соответственно с информационными входами устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия и точности, в него введен блок умножения значений интегральной функции, в точках на табличные коэффициенты,- входы которого соединены соответственно с входами задания интерполяционных коэффициентов, задания предшествующих значений интегрируемой функции и входом задания величины шага интегрирования устройства, а выходи подключены соответственно к входам второй группы блока. суммирования,. выходы которого являются выходами устройства, входы третьей группы блока суммирования соединены соответственно с выходами блока умножения значений функции на коэффициенты матриц, входы второй группы которого подключены соответственно к входам коэффициентов устройства, вход начальных значений интеграла и вход задания величины шага инте11рирования уст822194 свидетельство СССР

06 G 7/18, 1970, свидетельство СССР

06 Д 3/00, 1971., 8 У lg 9 8 Уу Щ

7 7g 7у

S(Составитель A. Жеренов

Техред М. Лоя Корректор О. Билак

Редактор Каминская

Жираж 745 Подписное

ВНИИПИ Государственного комитета СССР по делам иэобретений н открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Закаэ 1856/75

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4 ройства подключены к соответствующим входам блока суммирования.

Источники информации, принятые во внимание при экспертиэе

1. Авторское

9 344459, кл. С

2. Авторское

М 414604, кл. G

Ь-Р

Ь-!. ф