Устройство для воспроизведенияполинома лежандра

Иллюстрации

Показать всеРеферат

Союз Советскик

Социаяистичесимк

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ (61) Дополнительное к оат. саид-ау(22) Заявлено 18p67g (21) 2785277/18-24 ®) + с присоединением заявки H4С 06 6 7/40

Государственный комитет

СССР но делам июбретеиий и открытий (23) Приоритет

Опубликовано 15р481 Бюллетень М 16

Дата опубликования описания 150481 (З» УДК 681.333 (088.8) (72) Авторы изобретению

В.С.Поненко, H.È.Êóäðÿûîâ фала ъггр t, г (71) Заявитель (54 ) УСТРОИСТВО ДЛЯ ВОСПРОИЗВЕДЕНИЯ ПОЛИНОИА

ЛЕЖАНДРА

30

Изобретение относится к аналогоsoA вычислительной технике и может быть использовано в многоканальных системах связи, a также при решении краевых задач математической физики.

Известно устройство для моделирования разрывных функций, содержащее сумматоры, преобразователи аналог .код, дешифраторы, инверт)р, коммутаторы и группы ключей, которые ком» мутируют резисторы (13 .

Однако это устройство не позволяет формировать колебания, описываемые присоединенными полиномами Лежанд-15

"а ра р„, (

Наиболее близким к предлагаемому устройству является схема образования полинома Лежандра, содержащая интеграторы, блоки перемноженИя и сумматор (2) .

Однако известное устройство фор-, мирует колебания, описываевые полиномами Лежандра которые являются решениями дифференциального уравнения вида (X- з) Р „() -2срк (О+к (к+1) p„(t) =0, и не позволяет формировать колебания, описываемые присоединенными полиномами Лежандра, которые являются решениями дифференциального уравнения

l< г )р )t)-ггр )г) ° (р)ргг)-, „)р )ц:р, .где р щ, г ) < г)Щ г-m n-т1) .щ-г) „.m.г

Ф (и- нЦн-в-< и-m-2)(л щ.)) „щ 4.

t и 4(2п- )(2п-з)

Цель изобретения - расширение класса решаеваас задач.

Поставленная цель достигается тем, что в известное устройство, содержащее первый интегратор, вход которого является входом чстройства, а выход соединен с первым входом первого блока перемножения и со входом»822216 ся на вход инвертора 10, 65 второго интегратора, выход которого подключен к первому входу второго блока перемножения, выход которого соединен с первым входом сумматора, выход кот рого соединен со вторым входом второго блока перемножения

5 и со входом третьего интегратора, выход которого соединен со входом четвертого интегратора и со вторым входом первого блока перемножения, выход которого подключен ко второму входу сумматора; выход четнертого интегратора соединен с третьим входом сумматора и является выходом устройства, дополнительно введены пятый интегратор, блок деления и инвертор, причем выход первого интегратора подключен ко входу пятого интегратора, выход которого соединен с первым входом блока деления, выход которого подключен ко входу инвертора, выход которого подключен к чет- 2О вертому входу сумматора1 выход четвертого интегратора соединен со вторым входом блока деления.

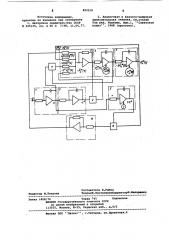

На чертеже схематически изображено предлагаемое устройство, 25

Устройство содержит интеграторы

1-5, блоки б и 7 перемножения, сумматор 8, блок 9 деления и инвертор10.

Устройство работает следующим образом. 30

До начала формирования колебаний вводятся начальные условия в интегратор 5 - единица, в интеграторы 3 и 4 соответственно при m$n p (p)=o; p (p)= З5

m, nl 2n)!

h n 2nnI in-г )! и п (2 n)!

m-n P (o)-Q P (о)= и I n 2п,nl

При,включении питания постоянное напряжение П подается на вход интег- 4() ратора 1, который преобраэует его в сигнал текущего времени t. Этот сигнал параллельно подается на первый вход блока 7 перемножения, на второй вход которого поступает колебание, описываемое функцией-2Рп (t), с выхо-. да интегратора 3, сигнал текущего времени t поступает также на вход интегратора 2 и на вход интег— ратора 5 . С выхода интегратора

2 сигнал квадрата текущего времени 5О подается на первый вход блока перемножения 6, на второй вход которого подается колебание, описываемое функцией Р (), с выхода сумматора

8, а с выхода интегратора 5 колеба- 55 ние, описываемое функцией 1-t, подается на первый вход блока 9 деления, на второй вход которого подается колебание, описываемое функцией (Ъ), с выхода интегратора 4. С ЬО вйхода блока 9 деления колебание, pITI ( описываемое. функцией и ) . подаетq 2

Формируемые на выходах блоков 6 g и 7 перемножения, интегратора 4 и инвертора 10 колебания, описываемые функциями соответственно (-1зР„(t)), l-.2t>n (t) ) i fP, () ) ы (Ь Р,",(} ), подаются иа 1-4-ый входы сумматора 8.

В результате на выходе сумматора

8 формируется колебание, описываемое функцией Р „(Ъ). Это колебание параллельно подается на второй вход блока б перемножения и на вход интегратора 3, который его преобразует в колебание, описываемое функцией-2Ри„ (Ъ). Это колебание параллельно подается на второй вход блоха 7 перемножения и вход интегратора 4, с выхода которого снимается колебание, описываемое требуемой функцией вида Р (1), присоединенным полиномом Лежандра соответствующего порядка.

Использование предлагаемого устройства позволяет создавать генераторы колебаний, описываемых присоединенными полиномами Лежандра нида

Р. «Й(- ) „PÄ«) для, многоканальных систем связи с разделением каналов по форме, а также для построения моделей полей магнитного диполя кругового тока и электрического диполя конечного размера.

Формула изобретения

Устройство для воспроизведения полинома Лежандра, содержащее первый интегратор, вход которого является . входом устройства, а выход соединен с первым входом первого блока перемножения н со входом второго ин,— тегратора, выход которого подключен к первому входу второго блока перемножения, выход которого соединен с перным входом сумматора, выход которого соединен со вторым входом второго блока перемножения и со входом третьего интегратора, выход которого соединен со входом четвертого интегратора и со вторым входом первого блока перемножения, выход которого подключен ко второму входу сумматора, выход четвертого интегратора соединен с третьим входом сумматора и является. выходом устройства, о т л и ч а ю щ е е с я тем, что, с целью расширения класса решаемых задач, в устройство дополнительно введены пятый интегратор, блок деления и инвертор, причем выход первого интегратора подключен ко входу пятого интегратора, выход которого соединен с первым входом блока деления, выход которого подключен ко входу иннертора, выход которого подключен к четвертому входу сумматора; выход четвертого интегратора соединен со вторым входом блока деления.

822216

Составитель В.Рыбин

ТехредЖ.КастелевичКорректорЮ.Макаренко.

Редактор М.Петрова

Заказ 1858/76 Тираж 745 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП Патент, г.ужгород, ул.Проектная,4

Источники информации, принятые во внимание при экспертизе

1 Авторское свидетельство СССР

Р 525125, кл. G 06 G 7/48, 11.04,77.

2. Аналоговая и аналого-цифровая вычислительная техника..Сб.статей

Под ред. Ушакова. Вып. 1, Советское радио, 1968 (прототип).