Полупроводниковое запоминающееустройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

<>822290

Союз Советскик

Социалистических. Республик

4i

Ф

К АВТОРСКОМУ СВИДЕТЕЛЫ;ТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 09. 07. 79 (21) 2794162/18-24 (5S)V KjI3

G 11 С 11/40 с присоединением заявки ¹â€”

Государственный комитет

СССР но делам изобретений и открытий (23) Приоритет—

Опубликовано 15.0431. Бюллетень № 14

Дата опубликования описания 15.0431 (53) УДК 681. 327. 66 (088.8) (72) Авторы изобретения

В.Р.Рябцев, В.В.Кулаков, А.В.Лихошерстов и Б.А.Валихметов (54) ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ

УСТРОЙСТВО

Изобретение относится к вычислительной технике и предназначено для использования в качестве запоминающего устройства видеотерминального комплекса.

Известно полупроводниковое запоминающее устройство,, содержащее на-. копитель, формирователи сигналов адреса, формирователи сигналов унравления, формирователи выборки блоков, формирователи сигналов входной информации, селектор, регистр информации и формирователи сигналов выходной информации. В данном устройстве, с целью увеличения быстродействия, в каждом разряде накопителя выбирается одновременно две микросхемы памяти, а младший разряд кода адреса используется для селекции информации этих микросхем на входе регистра информации (1) .

Однако lips увеличении емкости памяти время проверки устройства возрастает, так как нельзя осуществить одновременную проверку нескольких микросхем памяти, выходы которых подключаются через селектор к регистру информации

Наиболее близким по техническому решению к предлагаемому является запоминающее устройство, содержащее блоки памяти, объединенные в матричный накопитель; входы запись-считывания которых подключены к выходу . формирователей записи-считывания, . выходы соединены с выходными шинами, входы импульсного питания подключены через, формирователи импульсного питания к одним из выходов генераторов импульсов строк, другие выходы кото" рых соединены с одним иэ входов блока разрешения записи, другие входы которого соединены с соответствующи ми входами генераторов импульсов строк т5 и с выходами дешифратора строк, вход которого соединен с одним иэ выходов регистра адреса, другие выходы которого подключены к формирователям ад-. реса, соединенным с адресными входа"

20 ми блоков памяти, информационные входы которых соединены с информационной шиной (2).

Недостаток данного устройства заключается в том, что, при увеличе25 нии е ости к ц,ого информационнож разряда путем увеличения числа бло.ков памяти в каждом столбце, быстродействие устройства снижается ва счет увеличения суммарной емкости

З0 информационных входов и выходов уст822290 ройства. В таком устройстве увеличивается скорость передачи кода адреса из процессора, однако скорость передачи информации .возрасти не может, так как из различных строк матрицы информация поступает по общим шинам, и скорость ее обработки определяется быстродействием блоков памяти. Время проверки запоминающего устройства зависит от его емкости и от скорости обработки информации запоминающим устройством. Так, для проверки устройства с временем цикла

1 мкс, емкостью 4096 бит по -тесту

"скачущие единицы и. нули" необходимо затратить время, определяемое по формуле

t=BN t 8 4096 1 10 =2,24 мин где и — емкость проверяемого устройства, время цикла проверяемого устройства.

Для проверки устройства емкостью

16384 бит с тем же быстродействием потребуется уже 35,84 мин. Резкое увеличение времени проверки необходимо учитывать при разработке полупроводниковых запоминающих устройств с высокой информационной емкостью, так как при этом снижается производительность контрольного оборудова-: .ния, увеличивается стоимость контроля и себестоимость устройства.

Целью изобретения .является повь. шение информационной емкости устройства.

Поставленная цель достигается тем, что в полупроводниковое запоминающее устройство, содержащее матричный накопитель, выходы которого подключены к одним из входов селектора и выходным шинам устройства, одни из входов матричного накопителя через формирователи выборки соединены с выходами дешифратора адреса, входы которого подключены к одним иэ выходов регистра адреса, другие выходы которого через адресные формирователи подключены к адресным входам матричного накопителя, информационные шины и шины аписи-считывания, в него введены дополнительный дешифратор адреса, элементы ИЛИ и ИЛИ-НЕ, причем один из входов дополнительного дешифратора адреса подключен к первой шине записи-считыва". ния, другие входы — к другим входам селектора и соответствующим выходам регистра адреса, выходы дополнительного дешифратора адреса подключены к первым входам .элементов ИЛИ, вторые входы которых подключены -к второй шине записи-считывания, а выходы элементов ИЛИ подключены к другим входам матричного накопителя, информационные входы которого подключены к выходам соответствующих элементов

ИЛИ-НЕ, входы которых подключейы к входным информационным шинам.

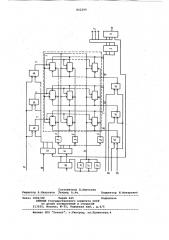

На чертеже представлена функциональная схема полупроводникового запоминающего устройства.

Устройство содержит блоки памяти, объединенные в матричный накопитель

1, выходцые шины 2, регистр 3 инфор-, мации, селектор 4, выходные шины 5 устройства, входы 6 и 7 матричного накопителя, формирователи 8 выборки, дешифратор 9 адреса, регистр 10 адреса, адресные формирователи 11, адресный вход 12 матричного накопителя, дополнительный дешифратор 13 адреса, .элементы 14 ИЛИ, элементы 15 ИЛИ-НЕ, шины 16 и 17 записи-считывания, йнформационные входы 18 матричного накопителя, входные информационные шины 19 и 20.

Устройство имеет два режима работы: режим работы в составе видеотерминального комплекса и режим контро20 ля.

Во время работы в составе видеотерминального комплекса запись информации осуществляется, как в одноразрядное ЗУ. Код адреса с выходов регистра 10 адреса поступает на входы формирователей 11, входы дешифратора 9 и дешифратора 13. Входная ин-формация поступает по шине 20, код операции записи — по шине 16. Формирователи 8 выборки выбирают необходимую строку блоков памяти матричного накопителя 1, дешифратор 13 выбирает необходимый блок в выбранной строке, который по коду операции, поступающему по шине 16, переключается в режим записи, а остальные блоки данной строки остаются в режиме чтения. Информация, поступившая по шине

20, записывается в выбранный блок памяти. В режиме чтения информация счи40 тывается одновременно со всех блоков памяти выбранной строки и записывается в регистр 3 информации, который работает в режиме сдвига информации и преобразует параллельный код ин4 . формации в последовательный, что увеличивает скорость передачи информации. Предусмотрена также возможность. передачи на выходные шины одного разряда информации через.селект) тор 4.

В режиме контроля код записи поступает по шине 17, а информация— по шинам 19. Выбор блоков памяти осуществляется дешифратором 9 строк.

Запись информации осуществляется одновременно во все блоки памяти выбранной строки. При чтении в режиме контроля считанная информация поступает на выходные шины 5 через регистр

3 информации параллельным кодом.

Щ В предлагаемом устройстве используются для дешифрации входы записьсчитывание блоков памяти, что позво.ляет увеличить емкость устройства не эа счет увеличения числа блоков

$5 в столбце, а за счет увеличения вы822290 ходов дешифратора кода операции.При этом уменьшается емкость входных и выходных информационных шин, что увеличивает быстродействие устройства.

Одновременное чтение информации со всех блоков памяти выбранной строки и передача ее последовательным кодом позволяют значительно увеличить ско; рость обработки информации запоминающих устройств видеотерминального комплекса, у которого осуществляется последовательная выборка информации.

Одновременное считывание и выдача информации со всех блоков памяти выбранной строки в режиме контроля позволяют уменьшить время его контроля и снизить себестоимость.устройства.

Формула изобретения

Полупроводниковое запоминающее устройство, содержащее матричный накопитель, выход которого подключены к одним из входов селектора и выходным шинам устройства, одни из входов матричного накопителя через формирователи выборки соединены с выходами дешифратора адреса, входы которого подключены к одним из выходов регистра адреса, другие выходы которого через адресные формирователи подключены к адресным входам матричного накопителя, информационные шины и шины записи-считывания, о т л и ч а ю— щ е е с я тем, что, с целью повышения информационной емкости устройства, в него введены дополнительный де шифратор адреса, элементы ИЛИ и ИЛИНЕ, причем один из входов дополнительного дешифратора адреса. подключен к первой шине записи-считывания, другие входы — к другим входам селектора и соответствующим выходам регистра адреса, выходы дополнительного дешифратора адреса подключены к первым входам элементов ИЛИ, вторые входы которых подключены к второй шине записи.-считывания, а выходы элементов ИЛИ подключены к другим входам матричного накопителя, информационные входы которого подключены к выходам соответствующих элементов

ИЛИ-НЕ, входы которых подключены к

20 входным информационным шинам.

Источники информации, принятые во внимание при экспертизе

1. Виталиев Г.В. и др. Разработка полупроводниковых сверхоперативных запоминающих устройств. Вопросы радиоэлектроники. Сер."Электронная вычислительная техника", 1977, вып.5, рис.12.

2 ° Авторское свидетельство СССР

Р 598120, кл.G 11 С 11/40, 1975 (прототип).

Составитель Л.Амусьева

Редактор А.Наурсков .Техред А.Ач, Корректор Ю.Макаренко

Заказ 1886/80 Тираж 645 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Рауыгкая наб., д.4/5

Филиал ППП "Патент", г.ужгород, ул.Проектная;4