Динамический логический элемент

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических.Республик

<11822370

Ф

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. сеид-ву(22) Заявлено 110379. (21) 2733860/18-21 с присоединением заявки И9(23) Приоритет

Опубликовано 15.0481„Бюллетень N9 14 р )м. к„.з . Н 03 К 19/20

Государственный иОмнтет

СССР но делам нзобретеннй н открытий (5З) УДК 621 ° 375. 083(088.8) Дата опубликования описания 15.0481 (72) Авторы изобретения г

Л.К. Самойлов, Ю.И. Рогозов и B.Â. Гайворонс с сс:", ссс / с с

Таганрогский радиотехнический институт им. В.Д. Калмыкова с (71) Заявитель (54} ДИНАМИЧЕСКИЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ

Изобретение относится к вычислительной технике и предназначено для построения динамических устройств, в частности микроэлектронных.

Известно устройство, содержащее два и-р-и транзистора, образующих триггер, и два р-п-р-транзистора, являющихся управляемыми источник;ми тока (1).

Недостаток данного устройства— ограниченные функциональные возможности, так как дополнительные возможности. элемента памяти исчерпываются одновходовой операцией сдвига.

Известно также устройство, содержащее триггер с непосредственными связями на двух многоколлекторных транзисторах, тактируемый и-р-и-транзистор, позволяющий совместно с фиксирующим диодом, диодом с малым прямым падением напряжения (например диодом Шоттки) и токозадающим двухколлекторным транзистором обеспечи вать нормальную работу элемента как в режиме хранения, так и в режиме установки j2).

Недостатком этого устройства является, во-первых, то, что он не может работать на ему подобные элементы без дополнительных схем согласования, что требует дополнительных аппаратурных затрат при проектировании вычислительных структур, а последнее ведет за собой увеличение габаритов, возрастание потребляемых мощностей и времени обработки информации. Во-вторых, использование коллекторов в качестве входных цепей приводит в режиме установки к значительному повыаенио потребляемой мощности.

Цель изобретения — умеиыаение мощ.ности, потребляемой элементом от Источника питания.

Для этого в устройство, содержа15 .щее два многоколлекторных траизисто ра TH n-p-и с перекрестными коллекторнобазовыми связями, базы которых подключены к коллекторам токозадающе» го транзистора р-п-р-типа, 5аза кото20 рого соединена с эмиттерами многоколлекторных транзисторов, коллектором ключевого транзистора п-р-и-типа и анодом фиксирующего диода, катод которого подключен к общей шине, эмиттеру ключевого транзистора и катоду диода с малым прямым падением напряжения, анод которого подключен к коллектору первого многоколлекторного транзистора, база ключевого тран"

30 .зистора подключена к неовой тактовой

822370 шине, введены два инжектирующих транзистора р-п-р-типа, базы которых подключены к аноду фиксирующего диода, а эмиттеры ко второй тактовой шине, коллектор второго инжектирующего транзистора подключен к входам устройст5 ва и эмиттеру перехватывающего инжекторного транзистора р-I;-p-òèïà, база которого подключена к аноду фиксирующего диода, а коллектор — к базе первого многоколлекторного транзистора, эмиттер токозадающего транзистора подключен к базе ключевого транзистора, а незадействованные коллекторы многоколлекторных транзисторов подключены к выходам устройства.

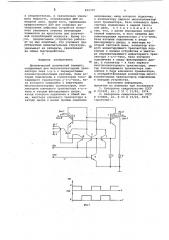

На фиг. 1 дана принципиальная 15 электрическая схема элемента, на фиг. 2 — топология элемента.

Динамический логический элемент (ДЛЭ) содержит два перекрестно соединенных многоколлекторных транзистора 20

1 и 2, образующие триггер, токозадающий транзистор 3, ключевой транзистор 4, фиксирующий диод 5, диод 6 с малым прямым падением напряжения, инжектирующие транзисторы 7 и 8 и пе- 25 рехватывающий инжекторный транзис— тор 9.

Первые тактовые импульсы подаются на эмйттер токозадающего транзистора 3 и базу ключевого транзистора 4, вторые в противофазе подаются на объединенные эмиттеры инжектирующих транзисторов 7 и 8. Входные логические сигналы подаются на коллектор инспектирующего транзистора 8 и эмиттер перехватывающего инжекторного транзистора 9, а выходные снимаются с незадействованных коллекторов многЬколлекторных транзисторов 1 и 2.

Элемент может работать в режиме хранения (ключевой транзистор 4 на- 40 сыщен при подаче импульса на первую тактовую шину и отсутствии импульса на второй тактовой шине) и в режиме установки (ключевой транзистор 4 закрыт). 45

В режиме хранения ключевой транзистор 4 насыщен и потенциал объединенных эмиттеров многоколлекторных транзисторов 1 и 2 равен U< < 0 что исключает влияние диода с мальл; прямым падением напряжения на режим хранения динамического логического элемента. Присутствие же в этом режиме нулевого потенциала на второй тактовой шине отключает инжектирующие транзисторы 7 и 8, исключая инжекцию тока в базы многоколлекторных транзисторов 1 и 2, следовательно исключается влияние входных сигналов.

В этом режиме триггер на многоколлек-60 торных транзисторах 1 и 2 питается от токозадающего транзистора 3.

В режиме установки потенциал объединенных змиттеров многоколлекторных транзисторов 1 и 2 равен Ugq 65 инжектирующие транзисторы 7 и 8 начинают инжектировать ток в базы многоколлекторнь1х транзисторов 1 и 2, а токозадающий транзистор 3 отключается. В дальнейшем при описании работы элемента, предположим, что в режиме. хранения многоколлекторный транзистор 1 включен, а многоколлекторный транзистор 2 выключен. Тогда при наличии хотя бы одного нулевого входного сигнала ток инжектирующего транзистора 8 полностью отбирается и таким образом ток в базу многоколлекторного транзистора 2 втекать не будет и триггер сохранит свое предыдущее состояние. В случае же, если нулевой входной сигнал отсутствует, ток от инжектирующего транзистора 8 отбираться не будет и в базы многоэмиттерных транзисторов 1 и 2 потекут одинаковые токи (в базу многоколлекторного транзистора 1 от инжектирующего транзистора 7). Однако за счет наличия в коллекторе многоколлекторного транзистора 2 диода 6 с малы л прямы.л падением напряжения U „ + 0„ ) 0 переход база-коллектор многоколлекторного транзистора. 2 будет смещен в прямом направлении, а следовательно не весь ток инжектирующего транзистора 8 будет втекать в коллектор многоколлекторного транзистора 1, что приведет к появлению тока в базе многоколлекторного транзистора 2, который, усиленный в J5 ) 1 раз, потечет через. многоколлекторный транзистор 2, что повлечет к уменьшению базового тока многоколлекторного транзистора 1, а впоследствии к его полному отключению, при этом многоколлекторный транзистор 2 включается.

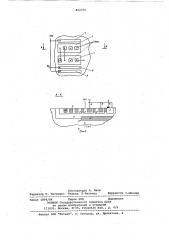

Из приведенной на фиг.2 топологии

ДЛЭ видно, что схема элемента позволяет вь:полнить все элементы одной фазы в общей изолированной области, причем подложка (P -область) является эмиттером токозадающего транзистора 3, обслуживающего многоколлекторные транзисторы 1 и 2 в одной фазе.

Ключевой транзистор 4, фиксирующий диод 5, база токозадающего транзистора 3 общие для элементов одной фазы. Коллекторы токозадающего транзистора 3 являются базами многоэмиттерных транзисторов 1 и 2 и коллекторами инжектирующих транзисторов 7 и 9.

База токозадающего транзистора 3 является эмиттером многоколлекторных транзисторов 1 и .2, коллектором ключевого транзистора 4 и базой инжектирующих транзисторов 7, 8 и .9. Эмиттер перехватывающего инжекторного транзистора 9 является коллектором инжектирующего транзистора 8.

Используя принцип управления инжекции путем введения дополнительных P-областей, удалось, незначительно усложнив топологию схемы, значительно уменьшить входной ток, 822370

t5 фиг. 1 а следовательно, и значительно уменьшить мощность, потребляемую ДЛЭ по входной цепи. Кроме того, применение предлагаемого ДЛЭ для создания интегральных цифровых устройств позволяет увеличить степень интеграции элементов на кристалле при полученной потребляемой мощности. Кроме то}го, . предлагаемое устройство работает на ему подобные, что упрощает про. ектируемые вычислительные структуры, уменьшает их габариты, увеличивает их общее быстродействие. о

Формула изобретения

Динамический логический элемент, содержащий два многоколлекторных транзистора типа n — р-п с перекрестными коллекторнобазовыми связями, базы которых подключены к коллекторам токо- Щ задающего транзистора р-п-р-типа, база которого соединена с эмиттерами многоколлекторных транзисторов, коллектором ключевого транзистора и-р-итипа и анодом фиксирующего диода, катод которого подключен к общей шине, эмиттеру ключевого транзистора и катоду диода с малым прямым падением напряжения, анод которого rîäêë:i÷åö. к колллектору первого многоколлекторного транзистора, база ключевого тран-, зистора подключена к первой тактовой шине, .отличающийся тем, что, с целью уменьшения потребляемой мощности, в него введены два инжектирующих транзистора р-n-p-типа, базы которых подключены к аноду фиксирующего диода, а эмиттеры. ко второй тактовой шине, коллектор второго инжектирующего транзистора .подключен к входам устройства и эмиттеру перехватывающего инжекторного транзистора п-р-п-типа, база которого подключена к аноду фиксирующего диода, а коллектор — к базе первого многоколлекторного транзистора, эмиттер токозадающего транзистора подключен к базе ключевого транзистора, а незадействованные коллекторы многоколлекторных транзисторов подключены к выходам устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Ð 513391, кл. С 11 С 11/40, 1974.

2. Авторское свидетельство СССР

9 573881, кл. Н 03 К 19/22, 1976 (прототип}.

822370

Юых

А -Д

Э ОЙ 2

Составитель A. Янов

Редактор !О. Петрушко Техред Т.Маточка, Корректор С.Шекмар

Заказ 1894/84 Тираж 988 Подпис ное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, 5-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4