Делитель частоты следования импульсовс дробным коэффициентом деления

Иллюстрации

Показать всеРеферат

Сеаез Севетскик

СОцивлистических

Республик

ОЙИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВ ЕТЕДЬСТВУ

< 322379 (61) Дополнительное к еат. саид-ау(22) Заявлено 0%0779 (21) 2792014/18-21 (5 )ы. К„.з с присоединением заявки NoH 03 К 23/24

Гаеударствеммый комитет

СССР ио делам изобретений и открытий (23) ПриоритетОпубликовано 15,04,81. Бюллетень N9 14 (53) УДК 621,4.74. 44 (088.8) Дата опубликования описания 1504.81 (72) Авторы (54 ) ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ

С ДРОБНЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ

Изобретение относится к импульсной технике и может быть использовано в измерительной аппаратуре, в устройствах формирования некратных частот, например в цифровых синтезаторах частоты.

Известен делитель частоты следования импульсов, содержащий блок запрета с подключенным к его выходу пересчетным блоком, счетчик импульсов элемент ИЛИ .и элемент задержки 1 ).

Недостатком данного устройства является его сложность.

Наиболее близким по технической сущности к предлагаемому является делитель частоты следования импульсов с дробным коэффициентом деления, содержащий три пересчетных блока, вход первого из которых соединен с выходом узла блокировки одного импульса, а выход - с первым входом узла блокировки oL импульсов, выход кото-. рого соединен со входом второго переу 2> счетного блока, выход которого подключен к входам узла блокировки одно» го импульса и третьего пересчетного блока, выход котОрого соединен со вторым входом узла блокировки aL пульсов (2).

Недостатком этого устройства является высокий уровень паразитной фазовой модуляции., Цель изобретения- уменьшение паразитной фазовой-модуляции частоты следования импульсов путем повышения равномерности чередования выходных импульсов, имеющих различные периоды следования.

Для достижения этой цели в делитель частоты следования импульсов с дробным коэффициентом деления, содержащий три пересчетных блока, введены коммутирующий блок, четвертый пересчетный блок и блоки управления, выхад первого из которых соединен с установочным входом первого пересчет. ного блока, первый вход — с выходом второго пересчетного блока и первым входом коммутирующего блока, второй вход — с первым входом третьего пересчетного блока и выходом четверто«

ro пересчетного блока, вход которого соединен с первым выходом коммутирующего блока, второй выход которого соединен со вторым входом третьего пересчетного блока, а второй входс выходом третьего пересчетного блока и входом второго блока управления, выход которого подключен к установоч822379 ному входу второго пересчетного блока, вход которого соединен с выходом первого пересчетного блока.

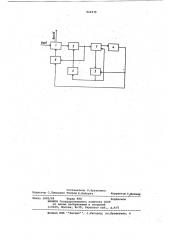

На чертеже представлена структурная электрическая схема устройства.

Устройство содержит пересчетные блоки 1-4, блоки 5,. б управления,,блок 7 коммутирующий °

Устройство работает следующим образом.

Блок 1 имеет при начальной установке делителя коэффициент пересчета

=М, поэтому при поступлении на его вход М импульсов на вход блока 2 поступает один импульс. Коэффициент пересчета блока 1-изменяется на К«

=Р, поэтому следующие выходные импуль-15 сы блока 1 поступают на вход блока 2 . после каждой группы P входных импульсов. Коэффициент пересчета в блоке

2 равен Кд „ = q,+2, поэтому через (0,+

+2) входных импульсов выходной им- 2О пульс блока 2 поступает на вход блока б, который производит установку в блоке 1 коэффициента пересчета

К, =М. Таким образом, на выходе блока 1 образуется последовательность импульсов, из которых один следует через М входных импульсов делителя, а (+1)импульс — через Р входных импульсов. Следующий цикл из { +2 ) выходных импульсов такой же, и коли.— чество циклов равно коэффициенту пересчета блока 3, который считает выходные импульсы блока 2, пропускаемые на его первый вход блоком 7.

Коэффициент пересчета блока 3 постоянный и равен I( з

После отсчета указанных циклов выходной сигнал блока 3 поступает на вход блока 5, который устанавливает коэффициент пересчета блока 2 равным К, -— < +1. 40

Выходной сигнал блока 3 одновременно переключает блок 7, поэтому выходные импульсы блока 2 с этого .момента поступают на блок 4 и не поступают на вход блока 3. Блок 4 имеет постоянный коэффициент пересчета К,, = R. Он считает количество 4 циклов, в которых один импульс следует через М входных импульсов делителя и < импульсов, следующих через

P входных импульсов, т. е. каждый цикл состоит из (+1) импульсов.

После отсчета и таких циклов нг. выходе блока 4 появляется сигнал„ который устанавливает в исходное состояние блок 3 и блок б так, чтобы

его выходной сигнал установил в блоке 1 коэффициент пересчета КА„„ =N, Далее, поступающие на вход делителя импульсы образуют на его выходе (на выходе блока 1) такую же импульсную щ последовательность. Таким образом, на выходе делителя образуется периодическая импульсная последовательность с периодом т„=атэ„, =(Nm+n) тВХ 65 количество выходных импульсов за время T

N« m+n — количество входных импульсов за время Т; .

Коэффициент деления частоты делителя при этом равен где m.Тдщ N m+n N n

Tax где N — целая часть коэффициента деления, и его дробная часть.

Коэффициенты пересчета блоков делителя.должны быть

r=n-(m-n)q;

R=-m-n-г(если n >(m-n), где - целая часть и

m-u дроби и где ) — целая часть дроби

Г и 1 И

Формула изобретения

Делитель частоты следования импульсов с дробным коэффициентом делеиия, содержащий три пересчетных блока, отличающийся тем, что, с целью уменьшения паразитной фазовой модуляции частоты следования импульсов путем повышения равномерности че- редования выходных импульсов, имеющих различные периоды следования, в него введены коммутирующий блок, четвертый пересчетный блок и блоки управления, выход первого из которых соединен с установочным входом первого пересчетного блока, первый вход — c выходом второго пересчетного блока и первым входом коммутирующего блока, второй вход с первым входом третьего пересчетного блока и выходом четвертого пересчетного блока, вход которого соединен с первым выходом коммутирующего блока, второй выход которого создинен со вторым входом третьего пересчетного блока, а второй вход - свыходом третьего пересчетного блока и входом второго блока управления, выход которого подключен к установочному входу второго пересчетного блока, вход которого соединен с выходом первого пересчетного блока.

Источники информации, принятые во внимание при экспертизе

1 ° Авторское свидетельство СССР

Р 425358, кл. Н 03 К 23/00, 03.01.72.

2. Авторское свидетельство СССР

9 534038, кл. Н 03 К 23/24, 13.06.75.

822379

Составитель О.Кружилина

Редактор С.Тимохина Техред Н.Бабурка

Корректор С. Шекмар.

Филиал ППП Патент, r.Óæãîðîä, ул.Проектная, 4

Закаэ 1885/84 Тираж 988 Подписное

ВНИИПИ Государственного комитета СССР по делам иэобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5