Устройство для поверки цифровыхприборов

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗЬВРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскнк

Социалистнческик

Рес у м824090 (6! ) Дополнительное к авт.. саид-ву (22)Заявлено11.07 ° 79 (2!) 2795528/18-21 с присоединением заявки М (23) П риоритет (51)М. Кл.

G 0l Й 35/00 фкударстюив11 кееитет

СССР ю ааааа взебретеввй в еткрыткВ

Опубликовано 23.04 ° 81 Бюллетень М 15 (53) УДК 681.325 (088. 8) Дата опубликования описания » 04 ° 81 (72) Авторы изобретения

Ю. М. Вешкурцев и В. Г. Гладилови (7I ) Заявитель

Омский политехнический институт (54) УСТРОЙСТВО ДЛЯ ПОВЕРКИ ЦИФРОВЫХ ПРИБОРОВ

Изобретение относится к измерительной технике и используется для поверки статистических анализаторов, имеющих выходные кодовые сигналы, соответствующие их показаниям или резуль5 татам измерения.

Известно устройство, содержащее поверяемый прибор, источник эталонного сигнала, блок памяти с двумя выходами, блок регистрации и обработки погрешностей 111.

Недостатками данного устройства является низкая надежность и низкое быстродействие.

Цель предлагаемого изобретения заключается в повышении быстродействия и надежности поверки .

Для достижения указанной цели в устройстве для поверки цифровых приборов, содержащее поверяемый прибор, источник эталонного сигнала, блок памяти с двумя выходами, блок регистрации н обработки погрешностей, введе-, ны модулятор, блок сопоставления и вычитания кодов, первый вход которого подключен к первому выходу блока памяти, второй — к выходу поверяемого прибора, а выход подключен к входу блока регистрации и обработки погрешностей, причем второй выход блока памяти соединен с управляющим входом модулятора, высокочастотный вход которого соединен с выходом источника эталонного сигнала, а выход подключен к входу поверяемого прибора.

Блок памяти выполнен на генераторе случайных чисел и блоке хранения законов распределения случайных чисел, выходы которых подключены соответственно к второму и первому выходам блока памяти.

Кроме того, с цалью поверки статистических.анализаторов фазы, выход источника эталонного сигнала соединен с опорным входом поверяемого прибора.

Формула изобретения

3 824090 4

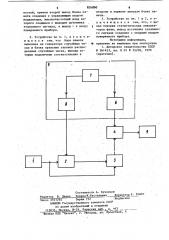

На чертеже представлена структур- тора 2 с изменяющимся случайным об- ная схема устройства для поверки циф- разом параметра Х анализируется поверовых приборов. ряемым прибором 3. На выходе прибоУстройство для поверки цифровых ра 3 получается оценка W+(x) закона приборов содержит источник 1 эталон- 5 распределения параметра Х,.которая в ного сигнала, модулятор 2, поверяемый виде кодов поступает на один вход прибор 3, блок 4 сопоставления и вы- блока 4 сопоставления и вычитания кочитания кодов, блок 5 памяти, блок 6 дов. На другой вход блока 4 с первохранения законов распределения слу- го выхода блока -5 памяти поступают чайных чисел, блок 7 синхронизации 1о коды, значения которых соответствуют и управления,. генератор 8 случайных образцовому закону распределения W(x), чисел, блок 9.регистрации и обработ- записанному в памяти блока б хранеки погрешностей. ния законов распределения случайных

Выход 1 источника эталонного сиг- чисел. Разность W(x) -W (x) законов

44. нала соединен с высокочастотным is распределения с выхода блока 4 в виде входом модулятора 2, выход которого кодов поступает в блок 9 регистрации соединен с входом поверяемого прибо- и обработки погрешностей, где погрешра 3. Выход прибора 3. соединен со вт1о- ности поверяемого прибора определяютрым входом устройства 4 сопоставления ся и регистрируются. Затем блок 7 и вычитания кодов, с первым входом ко синхронизации и управления включает торого соединен первый выход блока 5 закон W(x} с другими числовыми хапамяти, являющийся одновременно вь рактеристиками m q и бх, и весь про-. ходом устройства 6 хранения законов цесс поверки повторяется. Поверка распределения случайных "Bceuf BTopo прибора 3 заканчивается, когда будут выход .блока 5 памяти, являющийся од использованы все законы распределений новременно выходом генератора 8 слу- параметра Х с разными числовыми ха-. чайных чисел, подключен к управляюще- Рактеристиками, хранящимися в блоке 5 му входу модулятора 2. Выходы блока 4 . памяти. В конце поверки блок 9 ыцает сопоставления и вычитания KopoB coepH погрешности прибора 3, возникающие IIpH иены.с входом блока 9 регистрации и зо анализе случайных процессов. обработки погрешностей. .Таким образом, по командам блока 7

При замене поверяемого прибора 3 автоматически поверяется прибор при на цифровой статистический анализа- воздействии на него сл ай х сигнатор фазы выход источника 1 эталонно- .лов с разными законами распределения го сигнала в дополнение к имеющемуся и числовыми характеристиками, что насоединен еще с опорным входом при- чительно сокращает время поверки пр - . бора 3, а выход модулятора 2 c Hc бора и повышается надежность поверки, следуемым входом поверяемого при так как не требуется целого набора оббора 3 ° разцовых мер и операций для подключеУстройство для поверки цифровых ния и согласования их всякий раз с приборов работает следующим образом. поверяемым прибором.

С выхода источника 1 эталонного сигнала на высокочастотный вход модулятора 2 подается детерминированный сигнал. По команде с блока 7 генератор 8 .случайных чисел вырабатывает 4 1. Устройство для поверки цифровых последовательность цифровых кодов N4, приборов, содержащее поверяемый Йризначения которых распределены по за- бор, источник эталонного сигнала, ранее установленному в устройстве 6 блок памяти с двумя выходами, блок дифференциальному M(x) или интеграль- регистрации и обработки погрешностей, ному Е(x) закону с вполне конкретными 5о о.т л и ч а ю щ е е с я тем, что, числовыми характеристиками е и 6„, с целью повышения быстродействия и где m y — среднее значение, а 6»- сРед надежности поверки, в него введены неквадратичное значение параметра Х модулятор, блок сопоставления и вывходного сигнала модулятора. В резуль- читания кодов, первый вход которого тате модуляции параметр Х становится, ss подключен к первому выходу блока параспределенным по заранее выбранному мяти, а второй — к выходу поверяемого закону W(x) с числовыми характеристи- прибора, а выход подключен к входу

«ами m „ и6х . Выходной сигнал модуля блока регистрации и обработки погреш5 821 09á ностей, причем второй выход блока .памяти соединен с управляющим входом модулятора, высокочастотный вход которого соединен с выходом источника эталонного сигнала, а выход — к входу поверяемого прибора.. 2. Устройство по п. 1, о т л и ч аю щ е е с я тем, что блок памяти выполнен на генераторе случайных чи- 16 сел и блоке хранения законов распределения случайных чисел, выходы которых подключены соответственно к второму и первому выходам бпока па" мяти..

3. Устройство по пп. 1 и 2, о тл и ч а ю щ е е с я тем, что, с целью поверки статистических анализаторов фазы, выход источника эталонного сигнала соединен с опорным входом поверяемого прибора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Ф 361453, кл. G Ol R 35/00, 1970 (прототип).

Составитель А. Кузнецов

Редактор В. Данко Техред Ж.Кастелевич Коррект р Е. Рошко

Заказ 2101/65 Тираж 732 . . Подписное

ВНИИПИ Государственного. комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб. д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4