Устройство для сопряжения

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (»)824185 (61) Дополнительное к авт. свид-ву— (22) Заявлено 25.06.79 (21) 2784973/! 8-24 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл.з

Гееудерстееннмй комитет

G 06 F 3/04

СССР (53) УДК 681.325 (088.8) до делам изобретений и еткрмтий

Опубликовано 23.04.81. Бюллетень № 15

Дата опубликования описания 04.04.81 (72) Авторы изобретения

В. И. Финаев и Б. Ф. Харчистов

Таганрогский радиотехнический институ им. В. Д. Калмыкова (71) Заявитель (54) УСТРОИСТВО ДЛЯ СОПРЯЖЕНИЯ

Изобретение относится к вычислительной технике и может быть использовано в системах для сопряжения датчиков дискретной информации с устройством обработки данных или с управляющей вычислительной

1 машиной, в частности при передаче информации возбужденных датчиков состояний объектов.

Известно устройство для сопряжения„ содержащее блок считывания, блок местного управления, блок коммутации, блок пред варительного накопления информации, блок формирования импульсов, вход которого соединен со входом устройства, выход с первым входом блока накопления, второй вход которого соединен с первым выходом блока управления, входы которого соединены со вторыми входами устройства, а второй выход — с первым входом блока коммутации, первый вход которого соединен с выходом блока накопления, а выход — с йервым входом блока считывания, второй вход которого соединен с третьим выходом блока управления, а выходы являются выходами устройства (1).

Недостатком известного устройства является низкое быстродействие при вводе информации в управляющую вычислительную машину.

Наиболее близким к предлагаемому по технической сущности является устройство для сопряжения, содержащее блок управления, регистр, блок сравнения, счетчик текущего состояния датчиков, элементы И, 1О . распределитель, блок вывода информации, счетчик адреса, дешифратор адреса, коммутатор, первые входы которого соединены со входами устройства, вторые входы — с выходами дешифратора адреса, входы которого соединены соответственно с первыми входами элементов И и с выходами счетчика адреса, вход которого соединен с первым выходом блока управления, второй выход которого соединен с первым входом блока вывода, выход которого есть выход

20 устройства, а второй вход соединен с выходом коммутатора и со входом распределителя импульсов, выходы которого соединены соответственно со вторыми входами элементов И, и с первым входом счет824185

5S чика текущих состояний, вторые входы которого соединены с выходами элементов И, а выходы — с первыми входами блока сравнения и регистра, второй вход которого соединен с третьим выходом блока управления, а выходы — со вторыми входами блока сравнения, выход которого соединен со входом блока управления (2).

Однако устройство имеет низкое быстродействие, так как при изменении состояний датчиков передаются состояния всех датчиков, хотя достаточно передавать состояния только возбужденных датчиков.

Цель изобретения — повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройство, содержащее коммутатор, информационные входы которого являются соответствующими входами устройства, а адресные входы соединены с соответствующими выходами дешифратора адреса, входы которого подключены к соответствующим выходам счетчика адреса и первым входам соответствующих элементов И группы, выходами соединенных с соответствующими входами счетчика текущего адреса датчиков, группа выходов которого подключена к группе входов регистра и первой группе входов схемы сравнения, вторая группа входов которой соединена с группой выходов регистра, а выход — со входом узла управления, подключенного соответственно первым и вторым выходами ко входам счетчика адреса и регистра, введены память адресов и шифратор, причем группа входов памяти адресов подключена к выходам соответствующих элементов И группы, вход — к третьему выходу узла управления, а выходчерез шифратор к выходу устройства, выход коммутатора соединен со вторыми входами элементов И группы и вторым входом узла управления, группа входов которого подключена к выходам счетчика адреса.

При этом узел управления содержит первый и второй дешифраторы, триггер, реверсивный счетчик, генератор., первый, второй, третий и четвертый элементы И, причем первый вход реверсивного счетчика соединен со вторым входом узла, выходы через первый дешифратор соединены с единичным входом триггера, а второй вход реверсивного счетчика соединен с третьим выходом узла и с выходом первого элемента И, первый вход которого соединен с нулевым выходом триггера, а второй вход— с выходом генератора, первым входом второго элемента И, и первым входом третьего элемента И, второй вход которого соединен с первым входом четвертого элемента И и с выходом второго дешифратора, входы которого являются группой входов узла, нулевой вход триггера соединен с первым входом узла и вторым входом четвертого элемента И, выход которого соединен с тре5 о

l5

2О

25 зо

35 тьим входом реверсивного счетчика, единичный выход триггера соединен со вторым входом второго элемента И, выход которого является первым выходом узла, выход третьего элемента И является вторым выходом узла.

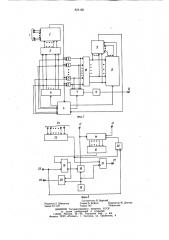

На фиг. 1 приведена блок-схема устройства; на фиг. 2 — функциональная схема узла управления.

Устройство содержит входы 1 устройства, по которым поступает информация о состояниях датчиков в виде двух уровней сигнала («О» — невозбужденное состояние и «1»возбужденное состояние), коммутатор 2, функциональное назначение которого состоит в поочередном подключении входов 1 к выходу коммутатора, элементы И 3 группы, число которых определяется разрядностью принятого кода адреса датчика, узел

4 управления, выполняющий функцию синхронизации при функционировании устройства в целом, дешифратор 5 адреса, определяющий номера выходов датчиков состояний, счетчик 6 адреса, память 7 адресов, состоящую из набора регистров, регистр 8, схему 9 сравнения, счетчик 10 текущего состояния датчиков, шифратор 11, преобразующий код адреса возбужденного датчика в код вычислительной машины, выход 12 устройства.

Узел 4 управления содержит второй вход 13 узла, реверсивный счетчик 14, первый дешифратор 15, на выходе которого должна быть единица при нулевом состоянии реверсивного счетчика 14, триггер 16, третай в ыход 17 узла, первый элемент И 18, генератор 19, второй, третий и четвертый элементы И 20 — 22 второй дешифратор 23, группу входов 24 узла, первый вход 25 узла, первый выход 26 узла, второй выход 27 узла.

Устройство работает следующим образом.

Импульсы от генератора 19 с выхода 26 элемента И 20, на втором входе которого имеется разрешающий потенциал с единичного выхода триггера 16, поступают на вход счетчика 6 адреса, в котором последовательно формируются адреса опрашиваемых датчиков. Каждому адресу датчика соответствует свой набор двоичных символов на выходах счетчика 6 адреса. Код адреса дешифрируется дешифратором 5 адреса, причем на выходах дешифратора последовательно во времени формируются потенциалы, подаваемые на входы коммутатора 2, который последовательно во времени подключает датчики к своему выходу. При этом если датчик невозбужден, то на выходе коммутатора — нулевой потенциал, если датчик возбужден — единичный потенциал. Единичный потенциал с выхода коммутатора подается на входы элементов И 3, разрешая запись в счетчик 10 адрес возбужденного датчика, причем этот адрес также одновременно записывается в памяти 7 адресов, а

824185

6 по входу 13 в реверсивный счетчик 14 записывается единица.

В течении цикла опроса адреса возбужденных датчиков суммируются в счетчике 10 и последовательно записываются в памяти 7.

Как только в счетчике 6 сформируется адрес последнего датчика то, согласно набору нулей и единиц на вторых входах 24, на выходе второго дешифратора 23 появляется потенциал.

Предварительно схема 9 сравнения на последнем в цикле такте генератора 19 проводит сравнение состояний счетчика 10 и регистра 8, и если их состояния равны, то на выходе схемы 9 сравнения потенциал отсутствует,а если их состояния отличны, то на выходе схемы 9 сравнения потенциал свидетельствует о том, что в течение цикла опроса по меньшей мере один из них изменил состояние, т. е. определена необходимость передачи адресов возбужденных датчиков по каналу связи с управляющей ма- 20 шиной., Присутствие нулевого потенциала на входе 25 и единичного потенциала на выходе второго дешифратора 23 приводит к сбросу через четвертый элемент И 22 реверсивного счетчика 14 в нулевое состояние.

Кроме того, по сигналу с выхода дешифра- - 5 тора 23 на паузе генератора 19 через элемент И 21 по выходу 27 осуществляется перепись содержимого счетчика 10 в регистр

8 со стиранием предыдущего состояния регистра 8. Если на вход 25 поступает единичный потенциал, то по его переднему фронту триггер 16 перебрасывается в нулевое состояние и запрещается подача импульсов на выход 26 запретом по второму входу второго элемента И 20, а разрешается прохождение импульсов генератора 19 через элемент

И 18 на второй вход реверсивного счетчика

14 и выход 17 узла 4. Импульсы с выхода

17 подаются на память 7, из которой адреса возбужденных датчиков считываются через шифратор 11 по выходу 12 в управляющую машину.

Когда будет считан последний адрес в реверсивном счетчике 14 будет также считана последняя единица, так как число единиц в счетчике 14 равно числу адресов в памяти 7. При нулевом состоянии реверсив- 4s ного счетчика 14 на выходе первого дешифратора 15 появляется единичный потенциал, по которому триггер 16 перебрасывается в единичное состояние и вновь импульсы генератора 19 поступают на выход 26, заново опрашивая состояния датчиков.

Таким образом, устройство обеспечивает опрос датчиков и формирование 6 управляющего машину адресов датчиков, и изменивщих свое состояние.

Формула изобретения

1. Устройство для сопряжения, содержащее коммутатор, информационные входы которого являются соответствующими входами устройства, а адресные входы соединены с соответствующими выходами дешифратора адреса, входы которого подключены к соответствующим выходам счетчика адреса и первым входам соответствующих элементов И группы, выходами соединенных с соответствующими входами счетчика текущего адреса датчиков, группа выходов которого подключена к группе входов регистра и первой группе входов схемы сравнения, вторая группа входов которой соединена с группой выходов регистра, а выход— со входом узла управления, подключенного соответственно первым и вторым выходами ко входам счетчика адреса и регистра, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены память адресов и шифратор, причем группа входов памяти адресов подключена к выходам соответствующих элементов И группы, вход — к третьему выходу узла управления, а выход — через шифратор к выходу устройства, выход коммутатора соединен со вторыми входами элементов И группы и вторым входом узла управления, группа входов которого подключена к выходам счетчика адреса.

2. Устройство по п. 1, отличающееся тем, что узел управления содержит первый и второй дешифраторы, триггер, реверсивный счетчик, генератор, первый, второй, третий и четвертый элементы И, причем первый вход реверсивного счетчика соединен со вторым входом узла, выходы через первый дешифратор соединены с единичным входом триггера, а второй вход реверсивного счетчика соединен с третьйм выходом узла и с выходом первого элемента И, первый вход которого соединен с нулевым выходом триггера, а второй вход — с выходом генеpampa, первым входом второго элемента

И и первым входом третьего элемента И, второй вход которого соединен с первым входом четвертого элемента И и выходом второго дешифратора, входы которого являются группой. входов узла, нулевой вход триггера соединен с первым входом узла и вторым входом четвертого элемента И, выход которого соединен с третьим входом реверсивного счетчика, единичный выход триггера соединен со вторым входом второго элемента И, выход которого является первым выходом узла, выход третьего элемента И является вторым выходом узла.

Источники информации, принятые во внимание при экспертизе

l. Авторское свидетельство СССР № 352270, кл. G 06 F 3/04, 1970.

2. Авторское свидетельство СССР № 548856, кл. G 06 F 3/04, 1977 (прототип).

Фиа1

Z0 фиг.2

Составитель В. Вертлиб

Редактор А. Шишкина Техред А. Бойкас Корректор М. Демчик

Заказ 2111)70 Тираж 745 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5 филиал ППП «Патент», г. Ужгород, ул. Проектная, 4