Устройство для вычисления функций

Иллюстрации

Показать всеРеферат

Союз Советскнк

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

<>824207

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву(22) Заявлено 221238 (21) 2699923/18-24 (51) М. Кл.

6 06 F 7/548 с присоединением заявки ¹Государственный комитет

СССР яо делам изобретений н открытий (23) Приоритет

Опубликовано 2 Э,0481.БЮллетень Но 15

Дата опубликования описания 230481

М) ЮК 681.3 (088.8) A.Â. Гусев, В.Н. Ахметов, Г.В. Пелевин и М.П. Цветков (72) Авторы изобретения (7 ) Заявитель

"*

/ (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИя фуНКЦИЯ

Поставленная цель достигается тем, что. в устройство для вычисления функций, содержащее блок сдвига, блок умножителей и сумматор, причем пер- . вый и второй входы устройства соединены с первым и вторым входами блока сдвига, первый и второй входы сумматора соединены с первым и вторым выходами блока умножителей, à первый выход сумматора соединен с первым выходом устройства, дополнительно введены коммутатор, сдвиговый регистр, накапливающий сумматор и блок выработки констант, причем первый и второй входы коммутатора соединены соответственно с первым и вторым входами устройства, выходы блока сдвига соединены с третьим и четвертыми входами коммутатора, первый и второй выходы коммутатора соединены соответственно с первым и вторым входами блока умножителей, пятый вход коммутатора соединен с третьим входом сумматора и выходом переноса сдвигового.регистра, выход которого соединен с первым входом накапливающего сумматора, выход которого соединен со вторым выходом устройства и входом блока выработки констант, первый и второй выходы которого соедиИзобретение относится к автомати. ке и вычислительной технике и может быть использовано в устройствах цкфрового автоматического управления и в тригонометрических вычислителях

ЦВМ.

Известны устройства для вычисления функций, использующих метод интегрирования цифровых сигналов (1).

Недостатком этих устройств являются значительные аппаратурные затраты.

Известно также устройство для вычисления функций, использующее итерационный метод (2). !

Наиболее близким техническим решением к предлагаемому является устройство для вычисления функций, содержащее блок сдвига, блок умножителей, функциональный генератор и ге- 2О нератор импульсов, сумматор,.компаратор, схему управления и схему или счетчик (2 1.

Недостатком обоих устройств является недостаточное быстродействие при вычислениях функций.

Цель изобретения - повышение быстродействия устройства за счет увели-чения скорости вычисления. 30

/

l (8242

В начальный момент в сдвнговом регистре 9 устанавливается двоичный код 1000 ... равный аргументу -45 который поступает в >:акапливающнй сумматор 10, предварительно установленный в нулевое положение. Далее код ..аргумента Ро с выхода. накапливающего сумматора 10 попадает в блок,выработки констант, выполненный, например, на основе постоянного запоминающего устройства, где .вырабатываются функции синуса и косинуса о которые поступают в блок 5 умножителей, как одни из сомножителей. Входные переменные Х и Y в виде параллельно- .го двоичного кода поступают на входы

1 и 2 и блок 3 сдвига, в кото6ом происходит сдвиг переменных Х и Y влево до появления старшей значащей единицы, наибольшей из входных пе, ременных Х. и У в старшем разряде, при этом число сдвигов входных переменных .одинаково. Так, например, если X-=00001010, Y=00100110, то на выходе блока 1 сдвига получаем сдвинутые коды .входных переменных Х =

=00101000, У 10011000, т. е. Xci=Х. 2

У, =У.2 ., где k=2

Далее сдвинутые коды входных переменных.Хд и У поступают через коммутатор 4 на вход умножителей 5, как вторые сомножители. В блоке 5 умножителей происходит выработка произвеДений Х1 siп goè У< соs PoпослеДние поступают в сумматор б, работаюций на вычитание, выход переноса которого определяет знак разности двух слагаемых.

На следующем этапе код аргумента

Ро в сдвиговом регистре 9 сдвигается вправо на один разряд. При этом код на выходе сдвигового регистра .9 равен = .2 " =0100 ... что соответ,ствует аргументу 22,5 . В зависимости от поступающего знака . в на1 капливающем сумматоре 10 происходит суммирование или вычитание предыдущего значения аргумента о и поступающего Pq в зависимости от знака разности . Результат поступает на блок 12 выработки констант и т.д.

На и-ом шЪге на выходе 11 накапливающего сумматора получим искомый угол 8. Регистр сдвига 9 очищается, а единица на выходе переноса сдвигового .регистра 9 поступает на управляющие входы коммутатора 4 и сумматора б. При этом коммутатор 4 подключает вхбды Х и Y устройства к блоку 5 умножителей, а сумматор б работает на сложение. В результате на выходах блока 5 умножителей получим X cos 9; и Y sin9<, а на информационном выхо е 7 сумматора 6

Х- cos 8„+Y ь! о6;=- Х +Y, т.е. искомую сторону р йрямоугольного треугольника (полярный вектор).

При решении прямоугольного треугольника по гипотенузе и катету

Х-Ып 6 = у с,ose

X.СОЛО 1 МАНИВ =P, причем где

50 знак разности и — число итераций, определяемое заданной точностью вычислений, и в кон-,60 кретном устройстве постоянно.

Рассмотрим работу предлагаемого устройства для случая определения полярного вектора и угла по двум известным декартовым координатам Х и Y. нен с третьим и четвертым входами блока умножителей, вторОй выход сумматора соединен со вторым входом накапливающего сумматора„ а вход сдвигоаого регистра соединен с тактовым входом устройства..

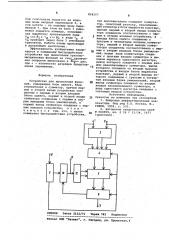

На чертеже представлена блок-схема предлагаемого устройства.

Устройство содержит первый 1 и второй 2 входы, блок 3 сдвига, комму-татор 4, блок 5 умножителей, сумматор 6, первый выход 7, тактовый вход.

8, сдвиговый регистр 9, накапливающий сумматор 10, второй выход 11,. блок 12 выработки констант. устройство работает следующим об- разом. 15 .Блок 3 сдвига осуществляет операцию сдвига кодов входных переменных

X и У, коммутатор 4 кодов служит .для коммутации входных переменных, блок 5 умножения осуществляет перем- Щ ножение кодов синуса и косинуса на коды входных переменных.

Первый и второй входы блока 5 ум- . ножителей подключаются через коммутатор 4 к выходам блока 3 сдвига и к. входам 1 и 2 устройства и входам блока 3 сдвига. Вход 8 является тактовым входом устройства.

Устройство позволяет вычислять оп;новременно функции arctg Y/X и + Х +У

Для вычисления этих.тригонометрических зависимостей используется формула

824207

Формула изобретения

ВНИИПИ Заказ 2112/71 Тираж 745 Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная,4 код гипотенузы подается на кодовые шины входной переменной Х, а код катета — на кодовые шины переменной У. При этом на блок 5 умножения подается команда, запрещающая выработку произведений вида .

X< cos p< v Y< sin f3„, а коды У -и

Х проходят через блок 5 умножения транзитом. Работа схемы происходит в дальнейшем аналогично.

Эффективность изобретения заключается в повышении быстродействия устройства при вычислении:тригонометрических функций за счет„увеличения скорости вычисления в -„ — раз, где n — количество разрядов йредставления переменных.

15 устройство для вычисления функ- 20 ций, содержащее блок сдвига, блок умножителей и сумматор, причем первый и второй входы устройства соединены с первым и вторым входами блока сдвига, первый и второй входы 25 сумматора соединены с первым и вторым выходами блока умножителей, а первый выход сумматора соединен с первым выходом устройства, о т л ич а ю щ е е с я тем, что, с целью. повышения быстродействия устройства, оно дополнительно содержит коммута. тор, сдвиговый регистр, накапливаю- . щий сумматор и блок выработки констант, причем первый и второй входы коммутатора соединены соответственно с пер= вым и.вторым входами устройства; а выходы блока сдвига соединены с третьим и четвертыми входами,коммутатора, первый и второй выходы коммутатора соединены соответственно с первым и вторым входами блока умножителей, пятый вход коммутатора соединен с третьим входом сумматора и выходом переноса сдвигового регистра, выход которого соединен с первым входом .накапливающего сумматора, выход которого соединен со вторым выходом устройства и входом блока выработки констант, первый и второй выходы которого соединены с третьим и четвертым входами блока умножителей, второй выход сумматора соединен со вторым входом накапливающего сумматора, а вход сдвигового регистра соединен с тактовым входом устройства..

Источники информации, принятые во внимание при экспертизе

1. Цифровые дифференциальные анализаторы. Под ред Б.Я. Когана, И., ГИФНЛ, 1959, с. 205.

2. Авторское свидетельство СССР

9 660059, кл. G 06 F 15/34, 1977 (прототип).