Устройство для блокировки и перезапускавычислительной системы при сбоях питания

Иллюстрации

Показать всеРеферат

О П И С,А Н И Е

ИЗОБРЕТЕНИЯ

Союз Советскик

Социалистических

Раслублик оо824214

Ж

" I л ф

»

4, /Г---=

% ",» (61) Дополнительное к авт. свид-ву (22) Заявлено .13337,8 (21) 2591826/18-24 (5М)М. Кл. с присоединением заявки йо (23) Приоритет

G 06 F. 11 j22 ъ

Государственный комитет

СССР ио делам изобретений н откРытий

Опубликоваиа 230481. ноллетеиь @ 15

Дата опубликования описания 230481 (53) УДК 681 326.

»7 (088.8) (72) Авторы изобретения

Б. В. 5евкопляс, Б. Г, Бекетов, Л. и Э. П. Овсянникова-Пан (73) Заявитель (54) УСТРОЙСТВО ДЛЯ БЛОКИРОВКИ

И ПЕРЕЗАПУСКА ВЫЧИСЛИТЕЛЬНОЙ

СИСТЕИЫ ПРИ СБОЯХ ПИТАНИЯ

2 ство для защиты системы электропитания, содержащее узел нормализации, входы которого являются входами пита:ющих напряжений устройства, узел согласования сигналов, включающий групI .,пу диодов развязки, подключенных анодами к соответствующим входа»м узла нормализации, а катодами — ко входу датчика состояния, группу элементов

1 И-НЕ, генератор тактовых импульсов, соединенный со входом распределителя, выходы которого соединены с катодами соответствующих диодов узла согласования сигналов и первыми входами со-! ответствующих элементов И-НЕ группы, вторыми входами подключенных к вы-

xnav латчика состояния, входч ге ератора тактовых импульсов и входу . исполнительного реле, выходы элеметов И«НЕ группы соединены с соответствующими входами узла индикации (2). (Недостаток этого устройства сос тоит в его сложности, резко возрас.та1ощей в условиях работы многомашин- ных вычислительных систем.

Цель изобретения — упрощение устройства.

Поставленная цель достигается тем, что в устройство, содержащее фор1

Изобретение относится к вычисли- . тельной технике и может найти при- . менение в многомашинных вычислитель-: ных системах.

Известно устройство для блокировки информации в вычислительной машине при включении и выключении Электропитания, содержащее триггер, блоки контроля, входы которых подключены к входам устройства, а выходы через элемент И соединены с входом блока автопуска и блока аварийного выключения. Установка триггера производится при переходе к подпрограмме прерывания при получении предупрежда45 ющего сигнала, а его сброс осуществляется по окончании работы прерывающей программы, что обеспечивает повышение надежности работы устройства при кратковременном исчеэновении20 питающего напряжения Ã1 . . Недостатком устройства является ограниченная область применения из» за невозможности его использования в вычислительных системах с магистральной, структурой связей между отдельными машиначи, каждая иэ которых имеет автономный блок питания.

Наиболее близким техническим решением к предлагаемому является устрой-30

824214 мирователь предупреждающих сигналов, соединенный входом с входом первичного питания устройства, группу элементов развязки, элемент И-НЕ и четыре элемента согласования,, уровня, введен элемент И, причеьс первый выход формирователя предупреждающих сигналов соединен. с выходом первого элемента развязки, вход которого.подключен ко входам,предупредительных сигналов устройства и первого элемента согласования уровня, выход ко- о торого соединен со входом прерыва° ния устройства и входом второго эле мента развязки, выходом подключенного к первому выходу формирователя:. предупредительных сигналов, второй fj выход которого соединен с выходами третьего-шестого элементов развязки, входы которых подключены саотввтст-I венно к выходу второго элемента согласования уровня, входу и выходу : 2() третьего элемента согласования уровня и первому входу элемента И, вы ход которого соединен с шиной нулевого потенциала, а второй вход — с вы" в дом элемента И-НЕ подк "енн "и -25 первым входам через четвертый элемент согласования уровня ко входу - выходу сброса устройства и входу третьего элемента развязки, а вторым входом — ко входу второго элемента согласования уровня и управляющему входу устройства, вход и выход третьего элемента согласования уровня являют» ся соответственно входом и выходом управления памятью устройства, вход четвертого элемента .развязки соединен со входом сброса устройства.

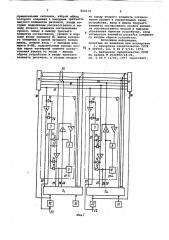

Яа фиг. 1 представлена блок-схема

:предлагаемого устройства, включенно- го в типовую вычислительную систему с общей шиной ; на .Фиг . 2 — схема 4() согласующего блока; на фиг. 3 - схема формирователя предупреждающих сигналов" на фиг. 4 — временная. диаграмма работы устройства.

Устройства. 1 для блокировки и перезапуска вычислительной системы при сбоях питания подключены к выходам .ЭВМ 2, входящих в вычислительную систему (на фиг. 1 показаны-только две крайние ЭВМ). Каждое устройство щ.

1 содержит формирователь 3 предуп-, реждающих сигналов, первый 4, третий 5, второй 6 и четвертый 7 эле- . менты согласования уровня, элемейт

И-НЕ, элемент И 9, элементы (диоды) 10-15 развязки. Кроме тога, на схеме обозначены шина 16 объединяю-, щая„входы предупредительных сигна лов устройств. Х всех ЭВМ, блоки 17 электрического согласования,шин, шина 18, объединяющая входы уйрав-, 60 ления памятью устройств 1, шина 19, объединяющая входЫ-выходы сброса устройств 1, первый выход 20 и вход.

2i формирователя 2, блок 22 питания, вход 23 первичного питания, второй " 45 вход 24 формирователя 3, шина 25 выхода уйравления памятью устройства, шина 26 входа сброса устройства, шина

27 нулевого потенциала (земляная шина), шина 28 управляющего входа устройства, шина 29 выхода прерывания устройства, выход 30 блока 22 питания, резервный источник 31 питания, шина

32 передачи данных.

Блоки 17 электрического согласования содержат набор делителей на резисторах 33. и 34 (фиг. 2), подключенныхl . к земляной шине 35 и выходу 30. Средние точки делителей соединены с шинами 16 1 8, 19 и 31.

Формирователь 3:предупреждающих сигналов (фиг. 3) выполнен по известной схеме и содержит последовательно соединенные выпрямитель 36 и фильтр

37, выход которого соединен с двумя дискриминаторами уровня 38 и 39. Выходы дискриминаторов уровня 38 и 39 соедйнены с выходными каскадами

40 и 41 формирователя 3, выполненными на транзисторах 42 и 43, соответст» венно, р-и-р и, и-р-и типа, базовых резисторах 44 и нагрузочных реезисторах:.

45, подключенных к шине 46 положительного питания и к тсйскам 20 и 24. устройство работает следующим образом.

При нормальной работе вычислительной системы на шины 23 первичного питания подано напряжение питающей сети, которое преобразуется блоками

22 питания в постоянное напряжение, питающие соответствующие ЭВМ 2 и сог- ласующие блоки 17. В точках 20 и 24, а также на шинах 16, 18 н 19 поддерживаются высокие потенциалы за счет нагрузочных резисторов, в точках 25, 26, 28 и 29 также присутствуют положительные потенциалы. Энергия от резервных источников 31 питания не потребляется,. они находятся в пассивном состоянии или в состоянии подзарядки (цепи подзарядки на фиг. 1 не показаны). Обмен информацией между ЭВМ 2, как обычно, осуществляется по шинам 31, которые в совокупности с шинами 16, 18 и 19 представляют собой общую, магистраль. При этом, «as-за подключения согласующих .блоков 17 к концам магистрали, .обеспечивается во-первых, электрическое согласование волнового сопротивле- .. ния линий связи на концах, и во-вторых, поддержание .высоких потенциалов на линиях в . пассивном состоянии, т.е. при. отсутствии сигналов типа Активный 0 на линиях.

Напряжение питания исчезает на входе одной из ЭВМ системы или одновременна на входах нескольких или всех ЭВИ. Рассматривают случай исчезновения питания на входе 23 первой ЭВМ 2.при исправном питании вто рай ЭВМ 2. Пусть в момент времени Т (фиг. 4) на шине 23,первичное пита»

824214

Ь ние первой ЭВМ выключается (эпюра

47 на фиг. 4). В момент временй Т напряжение на выходе фильтра 37 (эпюра 48) блока 3 снижается до величины, равной порогу срабатывания дискриминатора 38 (эпюра 49), н результате чего на выходе 20 вырабатывается низ° кий потенциал (эпюра 50). При даль-. нейшем снижении напряжения на выходе

Фильтра 37 в момент Т по уровню 51 срабатывает дискриминатор 39 блока

3, в результате чего на выходе 24 также формируется низкий потенциал

{эпЮра 52). В течение рассмотренного периода времени (Tg-Т ) питающее напряжение на выходе блока 22 питания

:(эпюра 53) не успевает существенно )5 измениться.за счет накопленной в блоке энергий, например, на емкости

Фильтра. К моменту Т3 напряжение на выходе блока питания выходит за заданные (гарантированные) пределы, а затем, после момента Тд,практически полностью исчезает. Низкие потенциалы точек 20 и 24 передаются через диоды 10, 13 и 12 в шины 16, 18 и

19 внешнего ТТЛ-интерфейса и через диоды .11, 14 и 15 — в шины 29, 25 и

26 внутренне о K-МОП-интерфейса. Потенциалы перечисленных шин остаются низкими при полном отсутствии питания, так как в этом случае потенциал, например шины 16 не превышает величины, равные сумме порогов отпирания диода 10 и выходного каскада 40 блока

3. Низкие потенциалы с шин внешнего интерфейса поступают н ЭВМ 2 (c исправным питанием), пройдя через эле- 35 менты 4, 5, 7, 8 и 9, питание которых не нарушено. .. Таким, образом, генерация последовательности сигналон, показанная на фиг. 4, осуществляется блоком 3, связанным с отказавшей ши- 40 ной питания; низкие потенциалы на шинах {внешних: и внутренних) поддерживаются за с ет диодов этого блока.

В ЭВМ с испранным питанием сигналы передаются с внешнего интерфейса во внутренний обычным путем,, через элементы согласования уровней.

После восстановления перничного питания (эпюра 47, момент Т ) восстанавливается вторичное питание иа выходе блока 22 первой ЭВМ (эпюра

53, период Т СТ<ТВ, после чего в моменты времени Т и Т7 последовательно выключаются дискрйминаторы 39 и

38 (эпюры 52 и 50), диоды закрываются, на шинах 16, 18, 19 устанавливают-, 55 ся высокие потенциалы, соответствующие ТТЛ-элементам, на шинах 29, 25 и 26 устанавливаются высокие потенциалы, соответствующие К-МОП-элементам.

Если питание исчезает на входах 60 нескольких (или всех) ЭВМ системы, то каждый блок 3 этих ЭВМ вырабатывает на своих выходах 20 и 24 сигналы (Фи1 . 4), которые суммируются на внеивней магистрали и передаются в ЭВМ с 65

HcHpckBHblM питанием (если таковые с ществуют) через элементы соглэ спрания уровней. Так же,как и в рассмот ренном случае, низкие потенциалы на шинах 29, 25 и 26 в 3BN с неисправ- . ным .питанием гарантируются диодами

11, 14 B 15.

Реакция каждой ЭВМ на сигналы в линиях 16, 18, 19, 29, 25 и 26 является общепринятой и состоит в следующем.

В момент времени Т„ отрицательный фронт сигнала на линии 29 (эпюра 50) воспринимается каждой ЭВМ как сигнал прерывания, по которому ЭВМ упряты, вает s память своей или чужой ЭВМ всю информацию, необходимую для сохранения .ее состояния. За время T=TТ эта процедура полностью заканчивается во всех ЭВМ. В момент Т низz кие потенциалы формируются на входах

25 и 26 всех ЭВМ. Потенциал н точке

25 блокирует оперативную память данной ЭВМ, потенциал н точке 26 приводит ЭВМ в состояние общий сброс. На интервале Т <Т(Т6 питание памяти осуществляется от резервных источников.

После восстановления питания н момент.

Т снимаются сигналы блокировки и о6щего сброса, а затем, в момент Т., все ЭВМ по положительному фронту сигнала в точке 29 переходят к восстановлению состояний и к продолжению прерванных вычислений. Сигнал общего сброса в шинах 19 и 26 инициируется, кроме того, как обычно, одной из ЭВМ по цепям: 28-6-19, 28-8-9-26 (в сво ей ЭВМ) или по цепи 19-7-8-9». 26 (из чужой ЭВМ).

Таким образом, устройство имеет более простую конструкцию и позволяет повысить надежность питания ЭВМ и сни1

:нить требования к резервным источникам питания.

Формула изобретения

Устройство для блокировки и перезапуска вычислительной системы при сбоях питания, содержащее фбрмирора тель предупреждающих сигналов, соеди- ненный входом с входом первичного питания устройства, группу элементов развязки, элемент И-HE и четыре элемента согласования уровня, о т л и—

9 ч а ю щ е е с я тем, что, с целью упрощения устройства, в него введен элемент И, йричем первый выход формирователя предупреждающих сигналов соединен с выходом первого элемента развязки, вход которого подключен ко входам предупредительных сигналов устройства и первого элементасогласования уровня, выход которого соединен со входом прерывания устройства и входом второго элемента развязки, выходом подключенного к первому выходу формирователя преду824214 предительных сигналов, вФэрой эйха которого соединен с выходами .третьего шестого элементов развязки, входы которых подключены, соответственно к выходу второго злемеита согласования уровня, входу и выходу третьего элемента согласования уровня и первому входу элемента й; выход которого .соединен с шиной нулевого потен циала, второй вход — с выходом элемента И-BR подключенным первым входам через четвертый элемент согла- сования уровня ко входу - выходу сброса устройства и входу третьего элемента развязки, а вторым входомко входу второго элемента согласования уровня и управляющему входу устройства, вход и выход третьего элемента согласования уровня являются соответственно входом и выходом управления памятью устройства, вход четвертого элемейта развязки соединен со входом сброса устройства.

Источники информации, принятые во внимание при экспертизе

l. Авторское свидетельство СССР

Р 495665, кл. G 06 F 9/18, 1974.

2. Авторское свидетельство СССР по заявке 9 2544960/18-24, кл, G 06 F ll/04, 1977 (прототип).

824214 т т, т

7о Т Т Tj T4

Составитель В. Вертлиб

Редактор Н. Рогулич Техред A.Ñàâêà Корректор H. шароши

Заказ 2126/72 Тираж 745 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035 М

i осква, Ж 35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4