Устройство для решения р-мерных задачматематической физики

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ИЗЛЬСТВУ

Союз Советских

Социалистических

Рес убли ()824216 а (6t) Дополнительное к авт. свид-ву (22) Заявлено 050679 (21) 2807656/18-24 сприсоединением заявки Йо

6 06 F 15/32

Государственный комнтет

СССР по деЪам изобрЕтений.я открмтяй (23) Приоритет

Опубликовано 230481. Бюллетень ИР 15

Дата опубликования описания 210481 (53) УДК 681.333 (088.8) l

И ° Kàáèí В. И. Коонейчук, В П. Т и A. A. Шерб не;)

1 "

Киевский ордена Ленина политехн ескй им. 50-летия Великой Октябрьской соцйа революции (72) Авторы изобретения (73) Заявитель

{54) УстРОЙстВО, Дт)Я РешениЯ р-меРных

ЗАДАЧ МАТЕМАТИЧЕСКОЙ ФИЗИКИ

Изобретение относится к вычислительной технике и может быть исполь зовано при построении специализированных вычислительных устройств для решения задач математической физики.

Известно устройство для решения р-мерных задач математической физики Е1) .

Однако известное устройство. имеет большое количество оборудования,: поскольку представляет собой унйверсальную ЦВИ, а р шенне задач математической Физики осуществляется в нем путем реализации соответствующей програмии, что обусловлквает низкое бы- тз стродействие устройства.

Наиболее близким к предлагаемому по технической сущности является устройство для решения трехмерных задач математической Физики, содержащее 2О блок ввода, блок вывода, р-мернухт., сетку, регистры адреса, блок управления, блок вычисления коэффициента и блок сравнения.В известном устройстве алгоритм решения задачи реализо- 2$ ван аппаратурно 2 .

Однако в устройстве S+1-я итерация выполняется только. после того, как окончена S- я итерация, т.е. процессы выполнения S-й и S+1-й итерации 30 не перекрываются во времени. Кроме

-.îãî, в известном устройстве одновременно может решаться не более одной задачи, что ведет к снижению эффективности использования оборудования..

Цель изобретения — повышение быстродействия и эффективности устройства.

Поставленная цель достигается тем, что в известное устройство, содержащее блок управления, -установочный выход которого соединен с установочными входами первой р-мерной сетки, состоящей из К ячеек, управляющие выходы блока управления подключены я упуправляющим входам блоков вывода и ввода, первая группа выходов которого подключена и управляющим входам

nepaoN p-меркой сетки, вторая группа выхода блока ввода соединена с информационными оводами первой р-мерной сетки, введено Ы-1 р-мерных сеток, причем информационные входы каждой

1-ой р-мерной сетки подключены к инФормационжзе входам 1+1-оа р-мерной сетки, а инфсцжационные выходи

И-ой р меуиой сетки соединены с ин(формационными входами блока вывода,:

;выходы которого соединены с информа824216 ционнымн входами блока ввода. пЦюая группа выходов которого подключена > к управляющим входам 0-1 р-мерных сеток,, установочные входы которых соединены .с установочным выходом блока уцравления 5

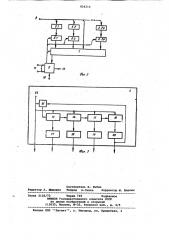

Ерове того, каждая ячейка р-мерной сетки сбдфржит 2р регистров, 2р ком- . мутаторов, накапливающий сумматор и распределитель, причем информационные входы ячейки соединены с первой груп- о пой информационных входов распределителя, управляющий вход распределите-. ля является управлящим входом ячейки, управляющие выходы распределителя,соединеныс управляющими входамн коммута-: торов и накапливающего сумматора, вы- 15 ходы пяти старших разрядов которого подключены ко второй группе информационных входов распределители,инфор- мационные выходы которого являются информационныМи выходами ячеек, устаЩ новочные .входы которого соединены с установочными входами накапливающего сумматора и с установочными входами 2р регистров, выходы которых подключены к установочным входам 2р коммутаторов, выходы которых соединены с информационными входами накапливающего суьюатора., Иа фиг. 1 показана структурная схема устройства; на фиг. 2 — то же, ячейки; на Фиг. 3 — то же, блока управления.

Устройство содержит р-мерные сетки 1.1-1.N,, блок 2 ввода, блок 3 ! вывода и блок 4 уцразления. Каждая ячейка р-мерной сетки содержит речист ры 5.1-5.2р, коммутаторы 6.1 6.2р, накапливающий сумматор 7, распределитель 8. установочные входы 9, управляющие входы 10, информационные входы 11, информационные выходы 12. 40

Блок 4 управления содержит последовательно соединенные счетчик 13 тактов, счетчик 14 циклов, счетчик

15 сеток и счетчик 16 итераций, выходы которых подключены соответствен 45

Но ко входам дешифраторов 17-20, выходы которых являются управляющими . выходами блока управления. Выход дешифратора 20 соединен с первым входом генератора 21. тактовых импульсов, О выход которого подключен к первому входу счетчика 13 тактов, Шина 22 установкн исходного состояния соединена со вторыми входами генератора

21 тактовых импульсов, счетчика.l3 тактов, счетчика 14 циклов, счетчи-. ,:ка 15 сеток, счетчика 16 итераций н: является установочным выходом блока

4 управления.

Устройство работает следующим об-, 60 дазоме

До начала вычислений в регистры .5.1-5.2р записываются значения коэффициентов а1, а в сумматоры 7 вано- 65 сятся значения правых частейФ урав-о нения д а.О Ф

Д а,.

„6+1 е 2Р. а;

121

В каждом j-м цикле вычисления (jl,n) на информационные входы 11 каждой ячейки сетки 1.1 с блока 2 ввода поступают цифры операндов

Uf, принимающие значения из множества (1, О, Ц и имеющие вес 2, где с - количество двоичных разрядов, после которых фиксируется за.пятая. Цифра операнда Up поступающая на управляющий вход коммутатора

6.1, управляет выдачей содержимого регистра 5.1 на сумматор 7 таким образом, что на сумматор 7 поступает прямой код регистра 5.1, бсли цифра

U равна плюс единице, дополни- тельный код, если цифра равна минус единице, и код регистра 5.i не выдается, если принимаемая цифра равна нулю. Йачиная с четвертого цикла,. распределитель 8, анализируя содержимое А пяти старших разрядов сумматора 7, формирует и выдает на информационные выходы 12пцифру числа .

U<, имеющую вес 2 . Эта цифра равна плюс единице, если А)Э, нулю — если А=О, или минус единице, если А(0. При этом на сумматор 7 со сдвигом на три разряда влево выдается.прямой код всех регистров 5, если формируемая цифра U равна минус единице, либо их дополйительный код, если цифра U равна плюс единице.

В трех первых циклах цифры U" pasны нулю независимо от содержймого сумматора 7. В конце каждого цикла осушествляется сдвиг содержимого сумматора 7 на один разряд влево.

Цифры операндов U" формируемые в j-м цикле вычисления ячейками сетки 1.1, в j+1-м цикле поступают на

Входы )1 соответству)ящик ячеек сетки 1 ° 2, которые формируют на выходах

12 значения операндов U ïoñTóïàþùèå на входы 11 ячеек сетки 1 ° 3 и т.д.

Таким образом, в каждом j- @ mac вычисления, на выходах сетки 1.8 формируются цифры ойерандов (7,имеющие вес 2 <В+ "р Вслн 1Ф,ф+1, где и — разрядноеть U, то значения старших разрядов операндов U" формируются на выходах сетки 1.0 в. тот момент, когда -в сетке 1.1 вычисления уже закончены. В этом случае цифры операндов U> через блок 3 вывода и блок

2 ввода непосредственно поступают на входы 11 .сетки 1.1. Если,же й<д +1, то в блоке 2 ввода дополнительно осуществляется задержка кодов U на и-4(й-)) ццклов.до окончания вы-числения 0" яа сетке 1.1. В дальнейшем выполнение каждой $-й итерации осуществляется на сетке 1 S(modN) .

Таким образом, изобретение дает возможность приступать к вычислению-.

824216,U 9+" не после окончания вычисления

U>, а непосредственно после получения первых разрядов кодов U, .что при наличии в составе устройства И сеток, позволяет организовать вычислительный процесс так, что выполнение S-й итерации íà S(modN)-й сетке перекрывается во времени с выполнением каждой 8 -й итерации (Р =Б-N+1, S+N-1) в 6 (mod N)-й сетке, за счет чего достигается выигрыш в быстродействии по сравнению с известным уст-, 10 устройством в ф\ ((1.п+Со(Г р)(д+ с)

К

-т г —,— р ь, 15 раэ, где tg — время сложения кодов в одноразрядном сумматоре; t z - время сдвига; M — количество итерацчй.

При этом в предлагаемом устройстве достигается большая эффективность gp использования оборудования за счет воэможности распределения аппаратурных ресурсов устройства между нес- колькими задачами. Так например, если сетки. устройства имеют размерность

L L L то в нем могут одновременно решаться две трехмерные задачи размерности (Ь-4) ЬхЬ, одна двухмерная задача размерности ЗЬхЬ и три одномерные задачи разномерности L<.

Формула изобретения

1. Устройство для решения р-мерных задач математической физики., содержащее блок, управления, установочный выход которого соединен с установочными входами первой р-мерной сетки, состоящей из К ячеек, управляющие выходы блока управления подключены 4() к управляющим входам блоков вывода и ввода, первая группа выходов ко» торого подключена к управляющим входам первой р-мерной сетки, вторая группа выходов блока ввода соединена с информационными входами первой р-мерной сетки, о т л и ч а ю щ.е е с я тем, что, с целью повышения быстродействия и эффективности устрояства, s него введены N-1 р-мерных сеток, причем информационные .выходы каждой 1-ой р-мерной сетки подключены к информационным входам i+1-ой р-мерной - сетки,,а информационные выходы N-ой. р-мерной сетки соединены с информационныМи входами бло,ка вывода, выходы которого соединены с информационными входами блока ввода, первая группа выходов которого подключена к управляющим входам

N-1 р-мерных сеток, установочные входы которых соединены с установочным выходом . блока управления.

2. Устройство о и. 1, о т л и— ч а ю щ е е с я тем, что каждая ячейка р-мерной сетки содержит 2р регистров, 2р коммутаторов, накапливающий сумматор и распределитель, причем информационные входы ячейки соединены с первой группой информационных входов распределителя, управляющий вход распределителя является управляющим входом ячейки, управляющие выходы распределителя соединены ,с управляющими. входами коммутаторов и накапливающего сумматора, выходы пяти старших разрядов которого подключены ко второй группе информационных входо распределителя, информационные выходы которого являются информационными выходами ячеек, установочные входы которого соединены с установочными входами накапливающего сумматора и с установочными входами 2р регистров, выходя которых подключены к установочным входам 2р коммутаторов, выходы которых соединены с информационными входами накапливающего сумматора.

Источники информации, принятые so внимание прн экспертизе

1. Авторское свидетельство СССР Р 565299, кл. G 06 F 15/32, 1977.

2., Авторское свидетельство СССР

9 603997, кл. G 06 F 15/32, 1978.

824216

Составитель В. Рыбин

Редактор А. Мишкина Техред А.Савка Корректор М. Шароши

Ю ВВФЮ ° ° В Ф ЮФВЮ

Заказ 2126/72 Тираж 745 Подписное

ВЯИИПИ Государственного комитета СССР по делам изобретений и открытий

3.13035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал DOll Патент, г. Ужгород, ул. Проектная, 4