Интегратор

Иллюстрации

Показать всеРеферат

Союз Советскик

Социалистических

Ресвублик о 324226 (61) Дополнительное к авт. сеид-ву (22) Заявлено 060779 (21) 27926 3б/18-24 (51)м. кл.з

G 06 G 7/184 с присоединением заявки Ио

Государственный комитет

СССР ио дМам изобретений и открытий (23) Приоритет—

Опубликовано 23048ХЬюллетеиь Н9 15

Дата опубликования описания 23.04. 81 (53) УДК 681 ° 335 (088. 8) В. И. Кос ауров (72) Автор изобретения (71) Заявитель (54) ИНТЕГРАТОР

Изобретение относится к вычислительной и импульсной технике, в частности < устройствам преобразования временного интервала в аналоговое напряжение.

Известны устройства Пля преобразования временного интервала в аналоговое,напряжение, использующие метод заряда конденсатора постоянным током, и содержащие спусковые схемы формирования стартовых и стоповых сигналов, эмиттерный повторитель, .транзисторные ключи, управляемые стартовыми и стоповыми импульсами, накопительный конденсатор, источник 15 постоянного напряжения P1), Однако преобразователь требует стабилизации зарядного тока конденсатора, постоянства формы импульса этого тока, высокое напряжение пита - 20 ния.

Наиболее близким к предлагаемому по техническрй сущности является линейный интегратор, содержащий входной одновибратор (формирователь импульсов), сое- 25 диненный с транзисторным ключом и через резистор с источником напряжения смещения, токозадающий транзистор, коллектор которого через диод и интегрирующую RC-цепь подключен к 30 источнику импульсного напряжения, а эмиттер через резистор соединен с выходом транзисторного ключа, подключенного через резистивный делитель к источнику импульсного напряжения. Кроме того, устройство содержит дополнительный транзистор, коллектор которого соединен через дополнительный резистор с источником импульсного напряжения и с базой токозадающего транзистора, эмиттер дополнительного транзистора подклчюен к средней точке резистивного делителя, а база соединена с эмиттером токозадающего транзистора (2)

Недостатком из вест ного интегратора является его значительная нелинейность, вызванная тем, что при получении достаточно высокой температурной стабильности устройства за счет отрицательной обратной связи, величина зарядного тока токозадающегс транзистора мала., Цель изобретения — уменыаение нелинейности интегратора.

Поставленная. цель достигается тем. что в интегратор содержащий формирователь импульсов, ключевой транзи,стор, эмиттер которого соединен с ши ной нулевого потенциала, а коллектор

824226 через первый ограничивакщий резистор подключен к источнику питания, усилительный транзистор, база которого подключена к шине нулевого .потенциала, соединенной через последовательно влюченные разделительный диод и первый масштабный резистор с эмиттврсм усилительного транзистора, коллектор которого подключен к базе токаоэадающего транзистора и через второй ограничиваяций резистор — к источнику питания, соединенному с эмиттером токозадающего транзистора, коллектор токоэадающего транзистора через интегрирующую RC-цепь соединен с шиной нулевого потенциала, и второй масштабный резистор, введены разделительный конденсатор, корректирующая RC-цепь и накопительный конденсатор, включенный между общим выводом разделительного диода и первого масштабного резистора и эмиттером ключевого транзистора, база которого через последовательно соединенные корректирующую RC-цепь и разделительный конденсатор подключена к выходу формирователя импульсов, а общий вывод разделительного конденсатора и корректирующей RC-цепи через второй масштабный резистор соединен с шиной нулевого потенциала.

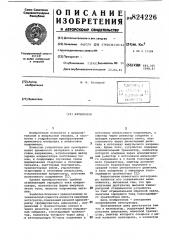

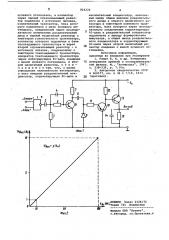

На фиг. 1 представлена электрическая принципиальная схема интегратора, на фиг. 2 — зависимость аналогового напряжения интегратора (08,„) от длительности входных импульсов (tÄ) °

Интегратор содержит формирователь

1 импульсов, разделительный конденсатор 2, масштабный резистор 3, корректирующую RC-цепь, состоящую из параллельно включенных конденсатора

4 и резистора 5, ключевой транзистор б с резистором 7 в цепи коллектора, накопительный конденсатор 8, разделительный диод 9, усилительный транзистор 10 с масштабным резистором

11 в цепи эмнттера и ограничивающим резистором 12 в цепи коллектора, токозадающий транзистор 13 с интег.рирующей RC-цепью, состоящей из конденсатора 14 и резистора 15.

Конденсатор 2 и цепочка параллельно включенных конденсатора 4 и резистора 5 включены между выходом формирователя 1 импульсов и базового ключевого транзистора 6, а их общий вывод через резистор 3 соединен с шиной нулевого потенциала, коллектор ключевого транзистора 6 подключен к накопительному конденсатору 8, который через резистор 11 соединен с эмиттером усилительного транзистора 10, общий вывод накопительного конденсатора 8 и резистора 11 через диод 9 подключен к шине нулевого потенциала, которая соединена с базой усилительного транзистора 10, а его коллектор через резистор 12 под-,) щей R С-цепи, формируя выходное, аналоговое напряжение, снимаемое с выхода интегратора.

При подаче на вход интегратора от генератора Г5-48 импульсов длительностью от 1,5 нс до 100 нс при частоте повторения импульсов 3-5 кГц нелинейность выходного аналогового напряжения составила менее 1Ъ, а выходное аналоговое. напряжение составило 1000 мВ нри подаче на вход интегратора импульсов длительностью

10 нс, и 10000 MB при подаче на вход интегратора импульсов длительностью 100 нс.

Таким образом, предлагаемый интегратор позволил уменьшить нелинейность и повысить выходное аналоговое напряжение при преобразовании врв40

55 менного интервала (преимущественно наносекундного диапазона) в аналоговое напряжение.

Формула изобретения Интегратор, содержащий формирова тель импульсов, ключевой транзистор, эм««ттер которого соединен с шиной ключен к источнику постоянйого напряжения, к которому присоединен эмиттер токозадающего транзистора

13, а его коллектор подключен к выходу интегратора и через интегрирующую RC-цепь — к шине нулевого потенциала.

Интегратор работает следующим образом.

Формирователь 1 импульсов форми рует на своем выходе импульсы, длительность которых определяется временным положением "Старт","Стоп" импульсов. При поступлении импульсов с формирователя 1 импульсов в базу ключевого транзистора 6, последний

15 открывается. .Накопительный конденсатор 8, ранее заряженный до напряжения E no цепи шина нулевого потенциала, диод 9, накопительный конденсатор 8, резистор 7 в цепи коллектора ключевого транзистора б и источник .питания Е, разряжается по цепи обкладка накопительного конденсатора 8, резистор

11, эмиттерный переход усилительного транзистора 10, шина нулевого потенциала и через открытый ключевой транзистор .б, обкладка «Ькопитвльного конденсатора 8.

Ток разряда накопительного конденсатора 8 протекая через эмиттерный переход усилительного транзистора 10, усиливается им, при этом на вго коллекторной нагрузке резистора 12 формируется импульс, усиленный по мощ-. ности, который и открывает токозадающий транзистор 13. Коллекторный ток токоэадающего транзистора 13 заряжает конденсатор 14, интегрирую824226 од аз 2126/72

Подписное нулевого потенциала, а коллектор через первый ограничивающий резистор подключен к источнику питания, усилительный транзистор, база которого подключена к шине нулевого потенциала, соединенной через последо- вательно включенные разделительный диод и первый масштабный резистор с эмиттером усилительного транзистора, коллектор которого подключен к базе токозадающего транзистора и через второй ограничивающий резистор - к источнику питания, соединенному с эмиттером токоэадающего транзистора, коллектор токозадающего транзистора через интегрирующую. ЯС-цепь соединен с шиной нулевого потенциала, и вто- l5 .рой масштабный резистор, о т л и.ч а ю шийся тем, что, с целью уменьшения нелинейности интегратора, в него введены разделительный конденсатор, корректирующая RC-цепь и . gp накопительный конденсатор, включенный между общим выводом разделительного диода и первого масштабного резистора и эмиттером ключевого транзистора, база которого через последовательно соединенные корректирующую

RC-цепь и разделительный конденсатор подключена к выходу формирователя импульсов, а общий вывод разделительного конденсатора и корректирующей

RC-цени через второй масштабный резистор соединен с шиной нулевого потенциала.

Источники информации, принятые во внимание при экспертизе

1. Рехин Е. И. и др. Измерение интервалов времени в экспериментальной физике. М., "Атомиздат", 1967, с. 238-239, р. 7. 10а.

2. Авторское свидетельство СССР

Р 369577, кл. G 06 G 7/18, 1972 (прототип) .

Филиал ППП "Патент", г.ужгород, ул.Проектная,4