Ассоциативное запоминающее устройство

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОбРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советсиик

Соцмалистическмл

Республик

Iiii824311 (6 I ) Дополнительное K авт. с вид-ву— (22) Заявлено 25. 12.78 (21) 27009 13/18-24 с присоединением заявки,%— (23) Приоритет (5l) M. Кл .

G 11 С 15/00

Гееударстеенный кемитет

СССР ле делам изебретеннй и еткрытий (53) УДК681.327 (088.8) Опубликовано 23.04 81 Бюллетень ¹1.5

Дата опубликования описания 25.04.81 (54) АССОЦИАТИВНОЕ ЗАПОМИНАЮКЕЕ

УСТРОЙСТ ВО

1 . Изобретение относится к запоминаюшим устройствам и может быть использавано, например цля хранения и поиска информации о несправных адресах блоков памяти.

Известно э о наюшее усройсжо. 5 (ЗУ), используемое для хранения и поиска информации о неисправных адресах, представляюшее полноадресное однозарядное устройство 11.

Однако учитывая, что число неисправ-тй ных адресов значительно меньше числа работоспособных, применение полноадресного одноразрядного ЗУ для построения устройства для хранения и обнаружения неисправных адресов приводит к большой т избыточности оборудования.

Наиболее близким техническим решением к предлагаемому является ЗУ, в которсм BblxoHbI регистра адреса разбиты HB

20 группы по числу накопителей, выходы которых соединены через элементы И с. выходом устройства, каждая группа раэ рядов регистра адреса подключена к ад-2 ресным входам одного накопителя. Разрядность накопителя принимается равной числу неисправных адресов $2).

Однако обладая высоким быстродейст вием, устройство требует больших аппаратурных затрат.

Цель изобретения — упрощение устройства.

Поставленная цель достйгается тем, что в ассоциативном ЗУ, содержашем Я однозарядных адресных накопителей емкостью 2к бит каждый и Й +К-1-разрядный регистр, входы которого являются входами устройства (гле Я и К вЂ” целые числа,. ЙЪ 1 и К Ъ 1), причем выходы одноразрядных адресных накопителей подключены ко входам элемента И, вьссод которого является выходом устройства, адресные входы i -го однозарядного адресного накопителя (где 3 1.,2..., М ) подключены соответственно к выходам

Я+K-1-разрядного регистра, начиная с

1-го по i +К-1-ый.

3 82431

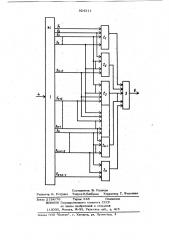

Нв чертеже представленв структурная схема,ассоциативного ЗУ.

Устройство соцержит И +К-1-разрядный регистр 1, одноразрядные адресные накопители 2,, 2,..., 2 с К-адресными

Входами каждый, алеьюнт И 3. Входы

4 регистра 1 являются входами устройства. Выходы 5., 5,..., 5цц . " регистра

1 подключены к адресным входам накопителей 2., 2, ..., 2 следукицим образом о выходы 5g... . 5к подключены к адресным вхоцам накопителя 2, выходы Q...ф jqq к адресным входам накопителя 2,1, и т.д., выходы 5 ... 5й+к, — к адресным вхор дам накопителя 2> . Выхоц каждого на- 15 копителя 2, 2, ...,2и подключен к соответствующему входу элемента И 3.

Выхоц 6 элемента И 3 является выходом устройства.

Устройство работает следующим об- 20 разом.

В исходном состоянии по всем адресам накопителей Д„, 2 „..., 2 записаны нули. Сигналы кода адреса блока памяти (БП) подаются на входы 4 регистра 1.

По сигналу обращения к БП происходит считывание информации из накопителей

2, 2,..., 2 „.

По сигналу ошибки, возникшей в считываемом из БП слове, в элементы па- мяти накопителей 2,, 2, ..., 2 м, адресуемых разрядами неисправного кодв адреса с выходов регистра 1, записывается "1 .

При -возникновении ошибки в другом слове, считываемом из БП описанная опера35 ция записи 1 повторяется.

Таким образом,.каждый pas при появ ленин нового неисправного адреса на регистре l в элементы памяти накопителей

2<. 2, -., 2, адресуемых разряцвми регистра 1, записывается 1 . МаксимвльФ Ф 0

1 4 ное число неисправных адресов А не преф вышает 2 " .

При повторном обращении по неиспрввМому ацресу из всех накопителей 2., 2 >

2 считывается "1" и элемент И 3 на выхоце 6 выцает сигнал обнаружения неисправного .адреса.

Технико-экономическое пренмущес гво, предлагаемого устройства по сравнению с известным заключается в значительном сокращении аппаратурной избыточности.

Например,при емкости блока памяти

4096 слов и числе неисправных адресов (ячеек памяти), равном 64, количество

Запоминающих элементов в устройстве сокращается в 4 раза.

Формула изобретения

Ассоциативное запоминающее устройство, содержащее Й одноразрядных адресных накопителей емкостью 2 бит каждый и

Й +K-l-pазряцный регистр, входы которого являются входами устройства (где Й и К вЂ” целые числа, Я 1 и К Ъ 1), причем выходы оцноразряцных адресных накопителей подключены ко входам алемента И, выход которого является выходом устройства, от ли ча ющ ее с ятем, что, с целью упрощения устройства, в нем адресные входи -ro оцноразряшiого адресного накопителя (гце 1 =1,2,..., Й ) подключены соответственно к выходам

И+К-1-разрядного регистра, начиная, с

4-ro,ïî +К-l-ый.

Источники информации, принятые во внимание при акспертизе

1. Патент США N 3768071, кл. 340-146.1, опублик. 1973.

2. Патент США N 4028678, кл. 340-146.1, опублик. 1978 (прототип), 8243ii

Составитель В. Рудаков

Рецактор H. Рогулич Техрец Н.Майорощ Ксщректор 1 . Решетник

Заказ 2134/76 Тираж 645 Подписное.ВНИИПИ Государственного комитета СССР по делам изобретений и откръгтий

113035,,Москва, Ж-35, Раушская наб., ц. 4/5 филиал ППП Патент, г. Ужгород, ул. Проектная, 4