Устройство для умножения частотыследования периодическихимпульсов

Иллюстрации

Показать всеРеферат

(71) Заявитель (54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧАСТОТЫ СЛЕДОВАНИЯ

ПЕРИОДИЧЕСКИХ ИМПУЛЬСОВ

Изобретение относится к автоматике и вычислительной технике и .может найти применение в цифровых устройствах различного назначения, например в цифровых преобразователях и измерительных приборах, в системах автоматического . управления и т.д.

По основному авт,св. У 357668 известно устройство для умножения частоты следования периодических импуль10 сов, содержащее делитель опорной частоты, входной счетчик импульсов, входной формирователь, выходной счетчик импульсов, запоминающрй регистр, выходной формирователь, блок управления, блоки элементов И (11 .

Однако известное устройство имеет недостаточную точность умножения.частоты следования периодических импульсов, обусловленную тем, что после каждого цикла подсчета импульсов с выхода делителя опорной частоты в нем остается остаток, величина которого может достигать значения единицы младшегр разряда, во входном счетчике импульсов. В результате фактическое значение частоты выходных импульсов оказывается меньше истинного. В особенности данный недостаток проявля ется при высоких значениях -умножаемой частоты и малом значении коэффициента умножения..

Целью изобретения является повышение точности умножения.

Поставления цель достигается тем, что в устройство для умножения частоты следования периодических импульcos, содержащее делитель опорной частоты, счетчик импульсов, счетчик импульсов опорной частоты, входной и выходной формирователи, запоминающий регистр, блок управления, первый выход которого подключен к нулевым входам всех разрядов делителя опорной частоты и запоминающего регистра, нулевой выход каждого разряда счетчика импульсов соединен с первым входом первого блока элементов И, втодовый элемент И, один вход которого. является управляющим, а остальные входы дешифратора 10 являются информационными, соединенными соответственно с дополнительными выходами делителя 1 опорной частоты. Устройство работает следующим обр зом. . Импульсы опорной частоты Ф; со входа 13 поступают на вход делителя

1 опорной частоты, коэффициент .деления которого равен заданному коэффициенту умножения k, и на вход выходного счетчика 4 импульсов. Импуль". сы с основного выхода делителя 1 опофной частоты, частота следования которых равна f 0 t k, ., подаются через эле-.. мент ИЛИ 11 на нулевой .вход триггера 12. На выходе дешифратора 10 также формируются импульсы с частотой следования10я М, которые по фазе one\ режают импульсы на основном выходе делителя 1 опорной частоты на половину периода. Каждым импульсом с выхода дешифратора 10 триггер 12 устанав- ливается в состояние "1", а очередным импульсом с основного выхода де- лителя l опорной частоты, следующим за .импульсом на выходе дешифратора

10, триггер 12 устанавливается в состояй е "0". При этом с его выхода на счетчик 2 импульсов поступают импульсы также с частотой следований, равной1О„ К . Каждый импульс умножаемой частоты f9,> со входа 13 поступает через входной формирователь 3 и блок 7 управления. При этом на соответствующих выходах блока 7 управления каждый раз формируются три следующие друг за другом сигнала. Сигнал с первого выхода блока 7 управле" ния устанавливает в состояние "0" все разряды делителя l опорной частоты, регистра 5, а также закрывает на время, равное длительности импульса, дешифратор 10 по управляющему входу для исключения прохождения на единичный вход триггера 12 помех, которые возможны при сбросе делителя 1 опорной частоты. Кроме того, сигнал с первОго выхода блока 7 управления проходит через элемент ИЛИ 11 на нулевой вхоц триггера 12. Сигнал со второго выхода блока 7 управления пос» тупает на вторые входы блока 8 элементов И и переносит обратный код из входного счетчика 2 импульсов в регистр 5, а сигнал с третьего выхода блока 7 управления устанавливает

824419 4 рой вход которого подключен ко второму входу блока управления, а выход - к единичному входу того же разряда запоминающего регистра, причем третий выход блока управления подключен к единичным входам всех разрядов счетчика импульсов, единичный выход каждого разряда запоминающего регистра соединен с.входом второго блока элементов И, выход которого, соединен с единичным входом того же разряда счетчика импульсов опорной частоты, а второй вход — с выходной шиной выходного формирователя, вход которого подключен к выходу послед- него разряда счетчика импульсов опорной частоты, введены триггер, дешифратор и элемент ИЛИ, первый вход которого соединен с основным выходом делителя опорной частоты, второй вход— с первым выходом блока управления и управляющим входом дешифратора, а выход через триггер — со входом счетчика импульсов, причем дополнительные выходы делителя опорной частоты сое динены с информационными входами дешифратора, выход которого соединен йо вторым входом триггера.

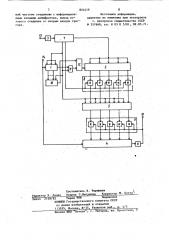

На чертеже представлена стрчктурная электрическая схема устройства.

Устройство содержит делитель 1 опорной частоты, входной счетчик 2 импульсов, входной формирователь 3, счетчик 4 импульсов опорной частоты, регистр 5, запоминающий выходной формирователь 6, блок 7 управления, бло.ки 8 и 9 элементов И, дешифратор 10, элемент ИЛИ 11, триггер 12, вход 13 импульсов умножаемой частоты, вход 14 импульсов опорной частоты, выход 15

40 устройства. Счетчик 2 импульсов, регистр 5 и выходной счетчик 4 импульсов опорной частоты имеют одинаковое число разрядов. Нулевые выходы счетч14ка 2 импульсов соединены поразрядно с первыми входами блока 8 элементов И, 45 выходы которых поразрядно соединены . с единичными входами регистра 5. Единичные выходы регистра 5 соединены поразрядно с первыми входами блока 9 элементов И, выходы которых - Ю рядно соединены с единичными входами регистра 5. Единичные выходы ре гистра 5 соединены поразрядно с первыми входами блока 9 элементов И, выходы которых поразрядно соединены и с единичными входами выходного счетчика 4 импульсов. Дешифратор 10 пред" ставляет собой, например, многовхо"

5 82441 все разряды счетчика 2 импульсов в состояние "1"..

За один период следования импульсов умножаемой частоты f << на вход счетчика 2 импульсов поступает ко- s личество импульсов частоты1оп К, рав"ное1 1п(к4,1 „, Так как в начале периода умножаемой частоты все разряды входного счетчика 2 импульсов устанавливаются в состояние "l", то по 10 окончании этого периода во счетчике

2 импульсов фиксируется число, равное1оп)к f äù -1.. При поступлении сле.дующего импульса умножаемой частоты формируется очередная группа из трех И сигналов блока 7 управления, нри этом в регистр 5 вносится из счетчика 2 импульсов число1рП ц.f „-1 в обратном коде, то есть в регистре 5 устанавливается число М4= Й -Ц1 4„„ „, Эр где и =2 à m — число разрядов в счетчике 2 импульсов а также в ре) гистре 5 и в счетчике 4 импульсов.

Число Й4,.которое представляет собой дополнительный код числами,щ М4Ч ц 1 перейосйтся из регистра 5 в счетчик

4 каждым импульсом переполнения, формируемым на выходе выходного счетчика

4 импульсов и поступающим на вторые . входы блока 9 элементов И через вы- Эр ходной формирователь 6..Частота.следования импульсов на выходе формирователя 6 при этом равна

Э5

4Р

4S,ния точности умножения, в него введены триггер, дешифратор и элемент ИЛИ, первый вход которого соединен с основным выходом делителя опорной частоты, второй вход — с первым выходом блока управления и управляющим входом дешифратора, а выход через триггер— со входом счетчика импульсов, причем дополнительные выходы. делителя опорЕсли при поступлении очередной группы сигналов с выхода блока 7 управления триггер 12 установлен в состояние "0" импульсом с основного выхода делителя 1 опорной частоты, то сигнал с первого выхода блока 7 управления подтверждает нулевое состоя" ние триггера 12. При этом сигнал на вход входного счетчика 2 импульсов с выхода триггера 12 не поступает. В данном случае остаточный код, который образовался в делителе 1 опорной частоты, не превышает половины емкости делителя 1 опорной частоты и половины цены младшего разряда счетчика

2 импульсов. Если же к моменту формирования очередной группы сигналов на выходе блока 7 управления триг9 гер 12 установлен в состояние "1",. то сигнал с.первого, выхода блока 7 управления установит триггер 12 в состояние "0". При этом на вход счетчика 2 импульсов поступает лишний импульс. В данном случае остаточный кбд, который образовался в делителе

1 опорной. частоты к моменту формирования первого сигнала на первом выходе блока 7 управления превышает полоУ вину емкости делителя 1 опорной час\. тоты, а, следовательно, и половины цены младшего разряда счетчика 2 импульсов.

Таким образом, как показывает схемно-технический анализ, за счет введения триггера 12, дешифратора

10 и элемента ИЛИ .11 устройство позволяет по сравнению с известным увеличить в два раза точность формирования в счетчике 2 импульсов числа импульсов частоты 3 „ ц-, равную

k<

Технико-экономический эффект от использования предлагаемого устройства определяется теми потерями, которые исключаются в системе„ использующей устройство, за счет увеличения точности, умножения частоты следования входных импульсов.

° Формула изобретения

Устройство для умножения частоты следования периодических импульсов по авт.св. Р 357668, о т л и ч а ющ е е с я. тем, что, с целью повыше824419

Составитель В Чернышев

P актор В. Данко Техред С.Мигунова Корректор М. Коста

2148 82 Тираж 988 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ

Филиал ППП Патент, r. Ужгород, ул. Проектная, ной частоты соединены с информационными входами дешифратора, выход которого соединен со вторым входом триггера.

Источники информации, принятые во внимание при зкспертиэе

1. Авторское свидетельство СССР

9 357668, кл. Н 03 К 5/01, 09.03.7).