Устройство для умножения

Иллюстрации

Показать всеРеферат

Союз Советсиик

Социалистические

Реслублин

ИСАНИЕ

If АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 23.06. 79 (21) 2801730/18-24 с присоединением заявки J4 (23) f1 ðèîðèòåò (SI )SL. К.н.

G 06 F 7/49

Гвеуднратевнный комитет

СССР до дедам неебретеннй н откритнй

Опубликовано 30.04. 81. виоллетень 34

Дата опубликования описания 04 .05.8 1 (53) УЛ3 68! . 325 (088. 8) С СО,то,.

УЕХАВ.,,. У 7", Bggy<<„, " " / (72) Авторы изобретения и

В. И. Кочергин и А. Ф. Декарев (71) заявители (54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ

0 О 0 0

0402

02Q

0 304

1 1 1 . 0 Н4п

0ф

04QX

Изобретение относится к вычисли- тельной технике и предназначается, в основном, для использования в сле- дяще-.регулировочных электроприводах переменного и постоянного тока с цифровым управлением, где используются многофазные коды, а управление этими электроприводами осуществляется от вычислительной машины, работающей в двоичном коде.

Известны электроприводы постоянно! а го и переменного тока, использующие арифметические устройства, работающие в многофазном коде (1).

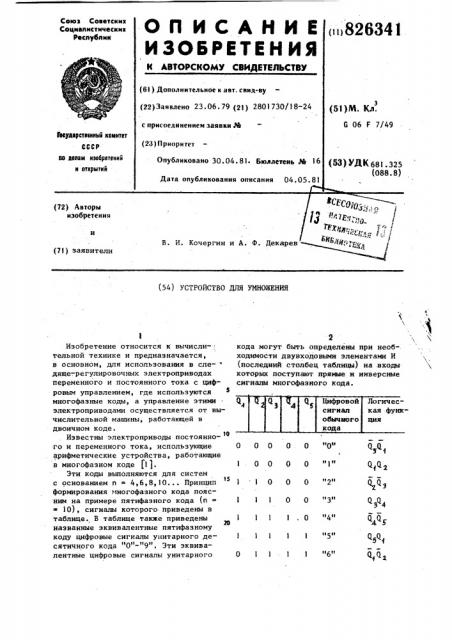

Эти коды выполняются для систем l5 с основанием п = 4,6,8,10... Принцип формирования многофазного кода поясним на примере пятифазного кода (n =

l0), сигналы которого приведены в таблице. В таблице также приведены названные эквивалентные пятифазному коду цифровые сигналы унитарного десятичного кода "0"-"9" ° Эти эквивалентные цифровые сигналы унитарного

2 кода могут быть определены при необходимости двувходовыми элементами И (последний столбец таблицы) на входы которых поступают прямые и инверсные сигиапы многофазного кода.

0 0 0 0 0 "0"

1 1 0 0 0 "2"

1 1 1 0 О "3"

1 l 1 1 "5"

0 1 ! Ъ"

3 82634

Продолжение таблицы .

0 0 1 1 1 и и

0 0 0 1 1, "8"

0 0 0 0 1 "9" Рэ

Ъ 4

50

Известны устройства умножения, работающие в двоичном коде (n = 2) (2).

Использование таких устройств для

15 случая, когда одно из заданных чисел задано в мнагофазном коде и необходим результат умножения также в многофазном коде, требует наличия на входе и

20 выходе устройства умножения преобразователей из одного кода в другой (многофазного в двоичный и двоичного в многофазный}, что приводит к увеличению оборудования и дополнительному снижению быстродействия. Вместе с тем, известно, что системы с основанием и > 2 обладают более высоким быстродействием и, следовательно, переход к системе с основанием n = 2 нецелесообразен.

Наиболее близким к предлагаемому является устройство для умножения, содержащее генератор кратностей и блок суммирования, в котором вход множимого устройства подключен к входу генератора кратностей„ выходы которого соединены са входом блока суммирования, выход которого является выходом устройства (31.

Однако при задании множимого в многофазном коде выполнение такого устройства усложняется за счет необходимости перевода мнажимого в двоична-кодированную систему счисления.

Цель изобретения — упрощение устроиства при ",àäàíèè множимого в многофазном коде. !

Поставленная цель достигается тем, что.в устройстве для умножения, содержащем генератор кратностей и блок суммирования, причем входы разрядов множимого устройства подключены ко входам генератора кратностей, а выходы блока суммирования подключены к выходам разрядов произвЕдения устройства, входы генератора кратностей соедийены с информационными входами соответствующих блоков элементов И, 1 4 выходы которых соединены с соответствующими входами блока суммирования, управляющие входы блоков элементов И, соединены с входами соответствующих разрядов множителя устройства, а генератор кратностей содержит (m-1) блоков умножения на два в многофазном коде m-разрядного множителя, причем входы п ичных разрядов (и >2, и — ос— нование системы счисления) первого блока умножения на два в многофазном коде соединены с входами генератора кратностей, входы разрядов каждого из блоков умножения на два в многофазном коде соединены с соответствующим входом генератора кратностей, выходы разрядов а-го блока умножения на два в многофазном ходе соединены с m-ми выходами генератора кратностей.

Кроме того, каждый блок умножения на два в многофазном коде содержит к узлов умножения на два в многофаз— ном коде, входы каждого из которых яв1 яются входами соответствующего п è÷ного разряда (n > 2, n — основание системы счисления) блока умножения на два, а выходы — выходами соответствующего п-ичного разряда блока умножения, вход переноса каждого узла умножения на два в многофазном коде подключен ко входу старшего двоичного разряда предЫдущего узла умножения на два в многофазном коде.

Кроме того, узел умножения на два в многофазном коде содержит элементы

И, ИЛИ и НЕ и дешифратор, который содержит группу и/2 элементов равнозначности, причем входы дешифратора соединены с соответствующим n/2 вхо-. дами узла, сигналы на которых образуют двоичное представление разряда и-ичного многофазнога кода, выход каждого из элементов равнозначности соединен с соответствующим выходам дешифратора, входы первого элемента равнозначности соединены с первым и и/2-м входами дешифратора, входы каждого j-го элемента равнозначности (j = 2,..., и/2) соединены с 1-м и (j-1)-н входами дешифратора, 1-ый выход дешифратара (1 = 2,...,fg)+>, где jX j — целая часть Х) соединен са входами элементов ИЛИ с первого по

2(1-1)-й, q-ый вход дешифратора (q = I — 4 1 +2,..., †) соединен со вхоИ дами элементов ИЛИ с (и -2q +1)-го по и/2-й, 1-ый выход дешифратора

И (l =1,..., — ) соединен с первым вхо5 82634 дом i-го элемента И, вторые входы первого элемента И и 1-х элементов И соединены со входом переноса узла умножения на два в многофазном коде, выход первого элемента И соединен со вхо- дом первого элемента ИЛИ, выход l-го элемента И вЂ” co входом (21-1)-ro элемента ИЛИ, вторые входы q-х элементов И через элемент НЕ соединени со входом переноса узла умножения на два 30 в многофазном коде, выход q-ro элемента И соединен со входом (n-2q)-ro элемента ИЛИ, выход i-го элемента ИЛИ подключен к i-му выходу узла, сигналы на выходах узла образуют двоичное !S представление разряда, а и-нчного многофазного кода.

На фиг. 1 приведена блок-схема устройства для умножения; на фиг. 2 соотношение между сигналами много- gp фазного кода Q<-Q и сигналами десятичного кода "0"- 9"; на фиг. 3— структурная схема блока умножения на два в многофазном коде; на фиг.4 функциональная схема узла умножения 25 на два в многофазном коде.

Число А (множимое) задано в многофазном коде, число В (множитель) — в двоичном, например четырех-разрядном (в, в„, в, в).

Входы разрядов множимого А соединены со входами генератора кратностей 1, который содержит (m-1) блоков 2 умножения на два в многофазном коде (m — разрядность множителя, в данном случае ((3 = 4), причем входы и-ичных разрядов (n — основа системы счисления, в данном случае и = 10) первого блока 2 являются входами генератора кратностей 1, а входы ка3кцого после- щ дующего блока 2 соединены с выходами предыдущего блока 2. Сформированные блоком кратностей значения А, 2А, 4А, 8А поступают на входы блоков элементов И 3-6 соответственно,на управляю-. 4 щие входы которых подаются значения разрядов множителя В, В » Вз.

Выходы блоков элементов Й 3-6 подключены ко входам блока 7 суммирования, состоящего из последовательно со- щ0 единеннных суммирующих узлов 8-10, на выходе которого формируется значение произведения АВ в многофазном коде.

Каждый блок 2 умножения на два в многофазном коде образует К узлов 11 умножения на два в многофазном коде (K — разрядность числа в п-ичной

1 6 системе счисления, в данном случае

К 3).

При этом входы первого разряда, на которые поступают сигналы Qz-Q соединены с входами первого узла ll умножения на два, вход, на который о поступает сигнал Q, соединен с входом переноса следующего узла ll умножения на два. Входы второго разряда, на которые поступают сигналы

1 соединены с входами второго узла 11, вход Q> соединен с входом переноса

4 следующего узла 11 умножения на два и т.д.

На функциональной схеме узла 1 умножения на два К-ro разряда (фиг.4)

-Х- 3 К- входы,,-Q соединены с входами дешифратора 12, который состоит из элементов равнозначности 13-17, формирующих соответственно выходные сигналы по следующему закону.

"0" "5" = Q О +Q-Q >

11)ll 6" = Я 0 4 6

2 1 Л

"2" "7" - 6Д vQ Q, !

l 311 Q ll8lt Q Q Q ((134и PII9w Q yQ Q f 5 (г

4 =11 к(=11

Выходные сигналы А, А, А, А„, K-1

А формируются на выходах элементов ИЛИ 18-22, один из выходов которых соединен с выходом элемента

И 23-27.

Два других входа элементов ИЛИ 18 и 19 соединены с выходами элементов равнозначности 14 и 15. Два других входа элементов ИЛИ 20 и 21 соединены с выходами элементов равнозначности 15 и 16. Два других входа элемента ИЛИ 22 соединены с выходами .элементов равно" значности 16 и 17. Первые входы элементов И 23-27 соединены с выходаии элементов равнозначности 13, 16, 14, 17, 15 соответственно. Вторые входы элементов И 23, 25 и 27 соединены с входом переноса данного узла !1, который через элемент НЕ 28 соединен с вторыми входааю элементов И 24 и 26.

Сигналы иа выходных винах K-го узла.ll умножения на два формируются по следующим логическим зависимостям

A",,= ("1 "0 6") ("2"1 "7") М(Р ("О"1 "5") < ) ;- - (1" Ь М г ь 3 )y(P (33 °

llQll) ) (2)

A ("2"м"7")y("3"ч"8")((ф ("1"у

"6")) (3)

А - = (2 у 7 )v(3 у8 )y(p (4 Ф и (() ) (4)

4- = ("3" 1 3 8") ("4 "ы" 9") у(Р„(("2"У

ll7ll) ) (5) 7 8263

Устройство для умножения работает следующим образом.

Число многофазного кода А поступает на генератор кратностей 1, где происходит его умножение на два на

5 первом блоке 2, с выхода которого число А поступает в следующий блок 2, .где происходит его умножение на два и т.д. Работа блоков 2 идентична и поэтому, рассмотрим К-ый разрядный узел одного иэ этих блоков. При коде на входах эквивалентном цифре "О"

1в»»-ii (О 4 5 = 1, Q = --0) не будет сигнала

> ( переноса в старший разряд P = Q = О

5 а если при этом нет сигнала переноса из младшего разряда (Р = О), то в соответствии с выражениями (1) †(5) на всех выходах будут нулевые сигналы (А„=О, А =О, А =О, АА=О, А„- -0,что также соответству т цифре 20

"О" на выходе.При наличии сигнала переноса из младшего разряда P 4=1 в соответствии с выражением (1) появится сигнал А,, =I,÷òo соответствует цифре на выходе разряда. 25

При коде на входных шинах, эквивалентном цифре "5" ("О"ч"5" = 1, 6 = l) работа узла 11 происходит

К-1

5 аналогичным обр>ззом с той лишь разницей, что формируется сигнал пере- 30 носа в старший разряд Р = Q

К-4

При коде на входах, эквивалентном будет сигнала переноса в старший разряд, а если при этом нет сигнала пе- З5 реноса из младшего разряда P 4= О, то в соответствии с выражениями (1)—

A 5 = О,.что соо ветствует эквивалентной цифре "2" на выходе. При наличии 40

- сигнала переноса из младшего разряда

К-1

Рк q= 1 и в соответствии с (3) — Ая =1, А = 1 А = О А4=- О А "= 0 что

- К-1 К-4 k-

> 5 » > соответствует цифре "3 на выходе.

При коде на входных шинах, эi вива- 45 лентном цифре "6" (")""ч"6" = 1, Й

1), работа схемы происходит аналогично с той лишь разницей, что формируется сигнал переноса в старший разряд Р, = Ц "= 1 и т.д.

Если на управляющих входах блоков элементов И 3-6 имеются сигналы Во =1, В 1, В = 1, В = 1, то число многофазного кода А и результаты умножения 2А, 4А; 8А поступают в блок 7 суммирования.

Если на управляющем входе какоголибо блока элементов И 3-6 нет сигнала, то на выходах всех разрядов этого блока будут нулевые сигналы, что в соответствии с таблицей эквивалентно нулевому значению слагаемого.

Таким образом, в результате сложения в блоках 8-10 многофазных сигналов с выходов блоков элементов

И 3-6 формируется результат умножения двух чисел А и В, одно из которых задано в многофазном коде, а другое в двоичном. формула изобретения

Устройство для умножения, содержащее генератор кратностей и блок суммирования, причем входы разрядов множимого устройства подключены ко входам генератора кратностей, а выходы блока суммирования подключены к выходам разрядов произведения устройства, о т л и ч а ю щ е е с я тем, что, с целью упрощения устройства нри задании множимого в многофазном коде, выходы генератора кратностей соединены с информационными входами соответствующих блоков элементов И, выходы которых соединены с соответствующими входами блока суммирования, управляющие входы блока элементов И соединены с входами соответствующих разрядов множителя устройства, а генератор кратностей содержит (m-1) блоков умножения, на два, в многофазном коде М-разрядного множителя, причем входы И вЂ” ичных разрядов (14 ) 2, И вЂ” oc нование системы счисления) первого блока умножения на два в многофазном коде соединены с входами генератора кратностей, входы разрядов каждого из блоков умножения на два в многофазном коде соединены с соответствующими входами генератора кратностей, выходы разрядов m-го блока умножения на два в многофазном коде соединены

i с m-ми выходами генератора кратностей.

2. Устройство по п. 1, о т л и— ч а ю щ е е с я тем, что каждый блок умножения на два в многофазном коде содержит к узлов умножения на два в многофазном коде, входы каждого из которых являются входами соответствующего п-ичного разряда (n ) 2, n — основание системы счисления) блока умножения на два, а выходы — выходами соо rnercтвующего и-ичного разряда блока умножения, вход переноса каж9 82634 дого узла умножения на два в многофазном коде подключен к входу старшего двоичного разряда предыдущего узла умножения на два в многофазном коде..

3. Устройство по и. 2, о т л и ч а5 ю щ е е с я тем, что узел умножения на два в многофазном коде содержит элементы И, ИЛИ и НЕ и дешифратор, который содержит группу п/2 элементов равнозначности, причем входы де- 111 шифратора соединены с соответствующими п/2 входами узла, сигналы на которых образуют двоичное представление разряда и-ичного многофазного кода, вход каждого иэ элементов равнознач- 15 ности соединен с соответствующим выходом дешифратора, входы первого элемента равнозначности соединены с пер" вым и n/2"м входами дешифратора, входы каждого j-го элемента равнознач- 20 ности (3 = 2,..., и/2) соединены с

J-м и (j-1)"м входами дешифратора, 1-ый выход дешифратора (1=2,..., Я) 1,. где gx) — целая часть х) соединен с входами элементов ИЛИ с пер- 25 вого по 2(1-1)-й р-ый вход дешифратора (q=I ô)+2,..., и/2) соединен со входами элементов ИЛИ с (n-2 +1)-го по n/2-й, i-ый выход дешифратора

А

By B1 11,В

1 10 (i 1,...,n/2) соединен с первым входом i-ro элемента И, вторые входы первого элемента И и 1 -х элементов И соединены со входом переноса узла умножения на два в многофазном коде выход первого элемента И соединен со входом первого элемента ИЛИ, выход

1-го элемента И - со входом (21-!)-го элемента ИПИ, вторые входы q-х элементов И через элемент .НЕ соединены со входом переноса узла умножения на два в многофазном коде, выход q-го элемента И соединен со входом(И-$-rO элемента ИЛИ, выход i-го элемента

ИЛИ подключен к i«му выходу узлами сигналы на выходах узла образуют двоичное представление разряда Н-ич- -. ного многофазного кода.

Источники информации, принятые во внимание при экспертизе

1. Авторское:свидетельство СССР

У 621090, кл.. Н 03 К 13/00, 1976.

2. Рабинер Л. и Гоулд П. Теория и применение цифровой обработки сигна-. лов. И., "Иир", 1978, с.568-580.

3. Фистер И.. Логическое проектирование ЦВМ. Киев, "Техника", 1960, с. 292-293, рис. 9-16 (прототип).

826341

2 2

4„gS

0 р

1 5

Составитель Н. Слюсарев

Редактор С. Шевченко Техред N.Kîøòóðà Корректор Г. Решетник

Заказ 2516/70 Тираж 745 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1 13035 Москва, Ж-35, Раушская наб., д. 4/5

Э

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4