Умножитель частоты следования периодических импульсов

Иллюстрации

Показать всеРеферат

(ii>826343

Союз Соаетскнк

Соцнапнстнчесинн

Республик

ОПИСАНИЕ изовеитиния

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свиа-ву (53 ) M. Кл.

G 06 F 7/52 (22)Заявлено 03 ° 08.79 (21) 2806947/18-24 с присоединением заявки М (23) Приоритет

3Ьеударстввнныб кемнтвт

СССР пе делам наебрвтвннй н еткрытнй

Опубликовано 30.04.81 ° Бюллетень ¹! 6

Дата опубликования описания 10. 05.8 1 (53) УДК681. .325(088.8) (72) Автор изобретения

А.С.Карпицкий (7l ) Заявитель (54) УМНОЖИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ

ПЕРИОДИЧЕСКИХ ИМПУЛЬСОВ

Изобретение относится к автоматике и вычислительной технике и может быть использовано при обработке ин- формации, представленной в виде периодических частотно-импульсных последовательностей.

Известен умножитель частоты, содержащий блок управления, генератор тактовых импульсов, делитель частоты, счетчик, регистр, сумматор, блок сравнения, элементы И и ИЛИ, триггер и элемент задержки (1 ).

Известен также умножитель частоты, содержащий формирователь импульсов, блок управления, генератор тактовых импульсов, делитель частоты, счетчики, регистр, элемент И и ИЛИ, ключ и одновибратор )2 ).

Недостатком этих устройств является отсутствие привязки выходных

20 импульсов импульсами умножаемой частоты.

Наиболее близким к предлагаемому является умножитель следования периодических импульсов, содержащий генератор тактовых импульсов, подключенный выходом к счетному входу первого делителя частоты, соединенного выходом со счетным входом первого счетчика, выход которого подключен к информационному входу первого регистра, соединенного выходом с первым входом блока сравнения кодов, подключенного вторым входом к выходу второго счетчика, а выходом— к первому входу обнуления второго счетчика, первому входу первого элемента И и к счетному входу второго делителя частоты, соединенного выходом с первым входом триггера, подключенного BblxopGM к вторЬму входу первого элемента И, выход которого соединен с первым входом элемента

ИЛИ, подключенного выходом к выходной шине умножителя, причем второй вход элемента HJIH второй вход триггера, управляющий вход первого регистра, второй вход обнуления вто3 82634 рого счетчика и входы обнуления первого счетчика и делителей частоты соединены с шиной ввода умножаемой частоты, а счетный вход второго .счетчика подключен к выходу генератора тактовых импульсов (3 ).

Недостатком этого устройства является пониженная точность умножения, обусловленная неравномерностью следования выходных импульсов умноженной частоты.

Цель изобретения — повышение точk но сти ум ноже ния .

25

Поставленная цель достигается

15 тем, что умножитель частоты следования периодических импульсов, содержащий генератор тактовых импульсов, подключенный выходом к счетному входу первого делителя частоты, соединен20 ного выходом со счетным входом первого счетчика, выход которого подключен к информационному входу первого регистра, соединенного выходом с первым входом блока сравнения кодов, подключенного вторым входом к выходу второго счетчика, а выходом — к первому входу обнуления второго счетчика, первому входу первого элемента И и к счетному входу второго делителя

30 частоты, соединенного выходом с первым входом триггера, подключенного выходом к второму входу первого элемента И, выход которого соединен с первым входом элемента ИЛИ подклю7

35 ченного выходом к выходной шине умножителя, причем второй вход элемента ИЛИ, второй вход триггера, управляющий вход первого регистра, второй вход обнуления второго счетчика и

- входы обнуления первого счетчика и делителей частоты соединены с шиной ввода умножаемой частоты, введены блок синхронизации, сумматор, второй и третий регистры и второй элемент

И, подключенный выходом к счетному входу второго счетчика, первым входом — к выходу генератора тактовых импульсов, а вторым входом - к выходу блока синхронизации, управляющий

50 вход которого соединен с выходом генератора тактовых импульсов, вход об" нуления — с выходом блока сравнения кодов, а информационный вход - e выходом старшего разряда сумматора, подключенного первым и вторым входам и к информационным выходам второго и третьего регистров соответственно, а выходами остальных разрядов - к

3 4 информационному входу третьего регистра, управляющий вход которого соединен с выходом блока сравнения кодов, причем информационный вход второго регистра подключен к кодовому выходу первого управляемого делителя частоты, а управляющий вход второго регистра и вход обнуления третьего регистра соединены с шиной ввода умножаемой частоты.

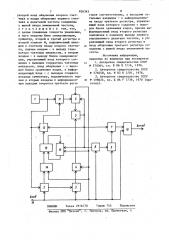

На чертеже изображена блок-схема умножителя частоты следования периодических импульсов.

Умножитель содержит генератор 1 тактовых импульсов, подключенный выходом к счетному входу первого делителя 2 частоты, выход делителя 2 соединен со счетным входом первого счетчика 3, выход которого подключен к информационному входу первого регистра 4, выход регистра 4 соединен с первым входом блока 5 сравнения кодов. Блок 5 подключен вторым входом к выходу второго счетчика 6, а выходом — к первому входу обнуления счетчика 6, первому входу первого элемента И 7 и к счетному входу второго делителя 8 частоты. Выход делителя 8 соединен с первым входом триггера 9, подключенного выходом к второму входу элемента И 7. Выход элемента И 7 соединен с первым входом элемента ИЛИ 10 выход которого подключен к выходной шине умножителя. Второй элемент И 11 подключен выходом к счетному входу счетчика 6, первым входом — к выходу генератора

1, а.вторым входом — к выходу блока

l2 синхронизации. Блок 12 соединен управляющим входом с выходом генератора 1, входом обнуления — с выходом блока 5, а информационным входомс выходом старшего разряда сумматора 13 ° Сумматор 13 подключен первым и вторым входами к выходам второго и третьего регистров 14 и 15 соответственно, авыходами остальных разрядов — к информационному входу регистра 15. Управляющий .вход регистра 15 соединен с выходом блока 5.

Информационный вход регистра 14 подключен к первому выходу делителя 2.

Входы обнуления счетчика 3, делителей 2 и 8 и регистра 15, второй вход обнуления счетчика 6, управляющие входы регистров 4 и 14, второй вход триггера 9 и второй вход элемента

5 82634

ИЛИ 10 соединен с шиной 16 ввода ум- ножаемой частоты.

Умножитель частоты работает сле дующим образом.

Токовые импульсы периода Т с выхода генератора l .поступают через делитель 2 с коэффициентом деления

К, равным требуемому коэффициенту умножения умножителя, на вход счетчика 3. Спустя промежуток времени, 1в равный периоду Т „ умножаемой частоты, в счетчике 3 и в делителе 2 будут зафиксированы соответственно целая и дробная части от деления количества импульсов, поступивших на вход делителя 2, на .коэффициент К.

По окончанию первого периода умножаемой частоты, эти результаты соответственно переносятся из делителя

2 в регистр 14, а из счетчика 3 — 2о в. регистр 4. В этот же момент обнуляются регистр 15 и счетчик 6.

Во второй период счетчик 3 считает аналогично, а результат, записанный в регистре 4, сравнивается посред-25 ством блока 5 с текущим значением числа импульсов, сосчитанных счетчиком 6. В момент совпадения кодов на входах блока 5, на его выходе формируется импульс, который срабатывает счетчик 6 и через элементы И 7 и ИЛИ

10 проходит на выходную шину умножения. Если при этом элемент И 11 открыт в течение всего периода умножаемой частоты, то импульсы на выходе блока 5 появляются через интервалы вРемени д t = — Р о р где! — 1- целаЯ г мъ,, часть отношения. В результате на выходной шине устройства каждый l-ый импульс появляется с опережением 4р (овиояой) иа время t< 1и1т 1, где

N - дробная часть отношения. й)

Уменьшение данной ошибки при работе устройства происходит следующим образом. Код Ь11остатка от делениями/ на К с выхода регистра 14 поступает на первый вход сумматора 13. По приходу первого импульса с выхода блока

5 этот код с сумматора 13 переписывается в регистр 15, и с выхода регистра 15 подается на второй вход сумматора 13. Таким образом в тече3 ние периода умножаемой частоты сумматором 13 производится сложенме кодов остатков, причем результат увеличивается íà dN с приходом каждого импульса с выхода блока 5. Если текущее значение суммы остатков превы3 6 шает число К, то на выходе старшегораэряда сумматора 13 формируется сигнал логической единицы. Этот сигнал с выхода сумматора 13 поступает на информационный вход блока !2 ° приведенного в исходное состояние импульсом с блока 5 и управляемый импульсами генератора 1. Блок 12 вырабатывает импульс длительностью Т, который закрывает на время Т элемент И ll, запрещая прохождение на вход счетчика 6 одного импульса с выхода генератора 1, В результате импульсы с выхода блока 5 могут появляться с опережением не более, чем на То.

Дпя синхронизации и привязки последнего выходного импульса к концу периода умножаемой частоты импульсы с выхода блока 5 поступают на счетный вход делителя 8.на коэффициент

К. Если на счетный вход делителя 8 успевает поступить К импульсов, а период умножаемой частоты еще ие оканчивается, то сигнал с выхода делителя 8 закрывает через триггер 9 элемент И 7 и прекращает подачу импульсов на выходную шину умножителя.

Таким образом, предлагаемое устройство позволяет по сравнению с известным уменьшить неравномерность следования выходных импульсов и повысить точность умножения.

Формула изобретения

Умножитель частоты следования периодических импульсов, содержащий генератор тактовых импульсов, подключенный выходом к счегному входу первого делителя частоты, соединенного выходом со счетным входом первого счетчика, выход которого подключен к информационному входу первого регистра, соединенного выходом с первым входом блока сравнения кодов, подключенного вторым входом к выходу второго счетчика, а выходомк первому входу обнуления второго счетчика, первому входу первого эле-. мента И и к счетному входу второго делителя частоты, соединенного выходом с первым входом триггера, подключенного выходом к второму входу первого элемента И, выход которого соединен с первым входом элемента ИЛИ

t подключенного выходом к выходной шине умиожителя, причем второй вход элемента ИЛИ, второй вход триггера, управляющий вход первого регистра, -7 82

1второй вход обнуления второго счетI чика и входы обнуления первого счет- чика и делителей частоты соединены с шиной ввода умножаемой частоты, отличающийся тем, что, с целью повышения точности умножения, в него введены блок синхронизации, сумматор, второй и третий регистры и . второй элемент И, подключенньФ выходом к счетному входу второго счетчика, первым входом — к выходу генератора тактовых импульсов, а вторым входом — к выходу блока синхрониза-, ции, управляющий вход которого соединен с выходом генератора тактовых импульсов, вход обнуления — с выходом блока сравнения кодов, а инфор мационный вход — с выходом старшего . разряда сумматора, подключенного первым н вторым входами к информационным выходам второгон третьего реги6343 8 стров соответственно, а выходами остальных разрядов — к информационному входу третьего регистра, управляющий вход которого соединен с выходом блока сравнения кодов, причем информационный вход второго регистра подключен к кодовому выходу первого управляемого делителя частоты, а управляющий вход второго регистра и

1р вход обнуления третьего регистра соединены с шиной ввода умножаемой частоты, Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

У 570064, кл. G 06 G 7/16, 1976.

2. Авторское свидетельство СССР

11 576658> кл. Н 03 Е 5/01, 1976.

3. Авторское свидетельство СССР

2о Ф 498624, кл. 6 06 F 7/39, 1970 (прототип).

ВНИИПИ Заказ 2516/70 Тираж 745 Подписное

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4