Арифметическое устройство

Иллюстрации

Показать всеРеферат

CoIo3 Севетскин

Сотаиалистическиа

Республик

О П И С А.Н И Е

ИЗЬБРЕТЕН ИЯ

И . АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

)826344 (6I ) Дополнительное к авт. свид-ву (22)Заявлено 13.04.79 (2!) 2752840/ 18-24 с присоединением заявки № (Sl )Nl. К.Ф, 6 06 F 7/548

Ркударственнм!! кемнтет

СССР ав девам наэбратений н вт«рмтнй (23) Приоритет

Опубликовано 30.04. 81. бюллетень ¹ 16 (53) УДК 681. .325(088.8) Дата опубликования описания 10.05.81

Новороссийскоевысшее инженерно (7!) Заявитель (54) АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО

Изобретение относится к вычислительной технике и предназначено для построения на его основе специализированных ЦВМ.

Известны арифметические устройства, состоящие из регистров, сумматоров-вычислителей и коммутаторов, вы- . полняющие операции поворота вектора (! ) и (2).

Однако эти устройства отличаются сложностью оборудования, !

О

Известно арифметическое устройство 12), выполняющее операции поворота вектора на плоскости х = k(x со5 f + y 51пт) (!) т5

k(y, cos 9 - x sing) где х, у — координаты исходного вектора; х, у» — координаты вектора повер к нутого на угол У; — коэффициент удлинения координат.

Преобразование (!) выполняется в числе других преобразований при ре2 ализации двухточечного преобразования Фурье.

Однако это устройство содержит большое количество оборудования.

Цель изобретения — уменьшение затрат оборудования блока поворота вектора арифметического устройства.

Поставленная цель достигается тем, что в арифметическое устройство, содержащее первый и второй регистры, первый и второй сумматоры-вычитатели, первый и второй коммутаторы, причем первый н второй информационные входы устройства соединены с первыми входами старших разрядов первого и второго регистров, выходы младших разрядов которых соединены с первыми входами соответственно первого и второго сумматоров-вычитателей, разрядные выходы старших разрядов первого и второго регистров соединены с соответствующими входами первого и второго коммутаторов соответственно, выходы первого и второго коммутаторов

2.6344 4

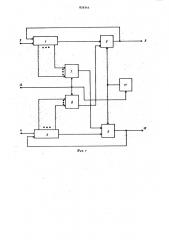

При реализации алгоритма (2) устройство работает следующим образом.

Величины х„. и у- хранятся соответ5 ственно в регистрах и 2, величина хранится в дешифраторе ll. С начала очередной итерации коммутаторы 7 и 8 соединяют соответствующие выходы регистров и 2 со входами сумматороввычитателей 6 и 5 таким образом, что на их входы поступают соответственно величиных"2 и у„..g ". Кроме того, на

4 вторые входы сумматоров-вычитателей

5 и 6 поступают величины х„ и у„.

4 э полученные на выходах сумматоров-вычитателей 5 и 6, величины х ° и у.

1+ 1 4+! записываются соответственно в регистрах и 2. Работа сумматоров-вычитателей управляется по величинам хранящимся в дешифраторе 11, который выдает очередное значение 9 но но«у1 меру итерации i который йоступает через вход 12 устройства на вход дешифратора. Номер итерации i используется также для управления работой коммутаторов 7 и 8 и подается на их управляющие входы.

Начальное значение х и у подается

3l! по входам 3 и 4 устройства, величины х и у снимаются с выходов 9 и 10 устройства.

Дешифратор (фиг. 2) предназначен

З: для выработки по номеру первых восьми итераций последовательности восьми значений (см. таблицу), соответствующих углу 49 53

000

001

010

011

100

110

При подаче на вход дешифратора ко- 55 да номера первой итерации на выходе . первой схемы И появляется сигнал ь!" соответствующий = +1, при подаче

H& вход дешифратора кода второй ите3 8 соединены со вторыми входами соответственно второго и первого сумматороввычитателей, выходы первого и второго сумматоров-вычитателей соединены соответственно со вторыми входами старших разрядов первого и второго регистров, первый и второй выходы устройства соединены с выходами соответственно первого и второго сумматоров-вычитателей, дополнительно введен дешифратор, причем вход дешифратора соединен с управляющим входом устройства, а выход — с управляющими входами первого и второго сумматоров-вычитателей.

На фиг. 1 показана структурная схема .устройства; на фиг. 2 — функциональная схема дешифратора.

Арифметическое устройство содержит регистры и 2, входы 3 и 4, сумматоры-вычитатели 5 и 6 коммутаторы

7 и 8, выходы 9 и 10 дешифратор 11, управляющий вход !2.

Вычисление выражения (1) в устройстве осуществляется но модифицированному алгоритму Волдера

- х1-+„= < j - 1 у! 2 (2)

У1+4 = У1 + 31 Х12 где ) - + 1 — функция, указывающая направление. поворота„

1=0,n"! " номер итерации.

Отличие алгоритма Волдера от алгоритма (2) состоит в том, что алго" . ритм Волдера предполагает одновременное вычисление 1 .. При реализации алгоритма (2) используются значения ; вычисленные заранее и хранящиеся в

1 дешифратопе. рации на выходе дешифратора появляется сигнал "0", соответствующий

1, для этого входы второй схемы

И не подключены к внутренним шинам дешифратора, и т. д.

5 82

Таким образом на выходе дешифра1 тора возникает развернутая во време- ни необходимая последовательность значений .

Эффективность изобретения заключается в уменьшении аппаратурных затрат на реализацию арифметического устройства для выполнения операции поворота вектора для двухточечного преобразования Фурье.

Формула изобретения

Арифметическое устройство, содержащее первый и второй регистры, первый и второй сумматоры-вычитатели, первый и второи коммутаторы, прйчем первый и второй информационные входы устройства соединены соответственно с первыми входами старших разрядов, первого и второго регистров, восходы младших разрядов которых соединены с первыми входами соответственно первого и второго сумматоров-вычитателей, разрядные выходы первого и второго регистров соединены с соот

6344 6 . ветствующнми входами первого и второго коммутаторов соответственно, выходы первого и второго коммутаторов соединены со вторыми входами соответственно второго и первого сумматоров-вычитателей, выходы первого и второго сумматоров-вычитателей соединены со вторыми .входами старших разрядов соответственно первогои второ1а ro регистров, первый и второй выходы устройства соединены с выходами соответственно первого и второго сумматоров-вычитателей, о т л и ч а— ю щ е е с я тем, что, с целью умень1 шения затрат оборудования, оно содержит дешифратор, причем вход дешифратора соединен с управляющим вхо- . дом устройства, а выход — с управляющими входами первого и второго сумщ маторов-вычитателей.

Источники информации, принятые во внимание при экспертизе !. Авторское свидетельство СССР

11 465630, кл. G 06 F 7/38, 1975.

25 2. Авторское свидетельство СССР

11 706846, кл. G 06 F 7/38, 1978 (прототип).

82б344

Составитель В.Венцель

Редактор С.Шевченко Техред А.Бафинец Корректор Г.Реыетннк

Заказ 2516 20 Тираа 245 Ноднисное

ВНИИПИ Государственного комитета СССР но делам изобретений и открытий

313035, Москва, Ж-35, Рауиская наб., д. 4УS

Филиал ППП Патент, r. Укгород, ул. Проектная, 4